# **Cadence Tutorial A: Schematic Entry and Functional Simulation** Created for the MSU VLSI program by Professor A. Mason and the AMSaC lab group.

#### **Revision Notes:**

| Feb 2013  | Minor updates                                 | P. O'Hara                 |

|-----------|-----------------------------------------------|---------------------------|

| Jan. 2010 | Minor updates/fixes                           | M. Carpenter              |

| Jun. 2008 | Updated for use with Cadence 6.1.2            | Waqar A Qureshi & C.Young |

| Jan. 2006 | Updated for use with spectre simulator        | C. Wallace                |

| Aug. 2003 | update and edit                               | A. Mason                  |

|           | add intro/revision/contents sections          |                           |

|           | standardize document format for all tutorials |                           |

| Jan. 2003 | modify simulation section                     | M. Parr                   |

| Aug. 2002 | update figures for AMI06 process              | J. Zhang                  |

| Jan. 2002 | create original tutorial                      | K. Zhang & A. Mason       |

#### **Document Contents**

Introduction Environment Setup Creating a Design Library Creating a Schematic Cellview Functional Simulation (transient analysis)

# Introduction

This document is one of a three-part tutorial for using CADENCE Custom IC Design Tools for a typical bottom-up digital circuit design flow with the AMIC5N process technology and NCSU design kit. This document, Tutorial A, covers setup of the Cadence environment on a UNIX platform, use of the Virtuoso schematic entry tool, and use of the Virtuoso Analog Design Environment (ADE) analog simulation tool. Tutorial B and C cover other Cadence tools important for custom IC design.

**Note:** Your paths may be different depending on the class or project you are working on. Also note that you can find additional tutorials and notes on the web from courses at other universities. These may be helpful in learning Cadence, but because of differences in the environment setup, you probably will not be able to follow a different tutorial step by step.

For more information about Cadence Virtuoso or the ADE tool, see the manuals.

# **Environment Setup**

<u>Before beginning this tutorial</u> you must setup Cadence to work with your account. The steps for doing this may vary with each class/project, so be sure to follow any class-specific setup steps before proceeding with this tutorial.

If you have not already done so, launch Cadence now by going to your working directory and typing virtuoso& at the command prompt. A Command Interpreter Window (CIW) similar to the example below will appear. When all the configuration files have been read, the END OF SITE CUSTOMIZATION message will be displayed indicating the start up was successful. With each new session, Cadence starts a new CDS.log file in your home directory where all the messages that appear in the CIW will be stored.

Along with the CIW window, you should also see the Library Manager window that lists the libraries in your working directory. For now the NCSU\_Analog\_Parts library is the

important one since it has basic circuit elements like transistors, current sources, voltage sources, ground, resistors, capacitors etc.

| Eils Tools Options Help                                                                 | cādence |

|-----------------------------------------------------------------------------------------|---------|

| The Topy Chrone Tech                                                                    | cauence |

| loaling vars from v/.cdsenv for tool asimenv                                            | 2       |

| Loaling wars from ~/.cdsenv for tool diserv                                             |         |

| loaling wars from /opt/soft/nest-odk-1.6.0 heta/cdssetup/cdsenv for tool designEditor   |         |

| loading waro from "/. odocny for tool dooignEditor                                      |         |

| loading wars from ~/.cdsenv for tool graphic                                            |         |

| loading wars from ~/.cdsenv for tool lavout                                             |         |

| loading wars from /opt/soft/ncsu-cdk-1.6.0.beta/cdssetup/cdsenv for tool layout0ptimize |         |

| loaling vars from ~/.cdsenv for tool layoutOptimize                                     |         |

| loading wars from ~/.cdsenv for tool layoutXL                                           |         |

| loading wars from w/.cdsenw for tool schematic                                          |         |

| loading wars from /opt/soft/ncsu-cdk-1.6.0.beta/cdssetup/cdsenw for tool spectre        |         |

| loading wars from ~/.cdsenv for tool spectre                                            |         |

| Loading wars from ~/.cdsenv for tool ui                                                 |         |

| Loading NCSU SKILL routines                                                             |         |

| lConvCodec::convertFromUnicode: using ASCII for conversion, iconv_open failed           |         |

| QIconvCodec::convertToUnicode: using ASCII for conversion, iconv_oren failed            |         |

| Done loading NCSU_CDK customizations.                                                   |         |

| QIconvCodecconvertFromUnicode. using ASCII for conversion, iconv_open failed            |         |

| QIconvCodec::convertToUnicode: using ASCII for conversion, iconv_open failed            |         |

|                                                                                         |         |

| I mouse L: M:                                                                           | F       |

**Command Interpreter Window**

Library Manager Window

In this tutorial, a simplified convention will be used to show the sequence of steps for the pull down menu. For example, File => Exit will indicate that you open the pull down menu for File and then click on Exit. Another example could be Tools => Analog Artist => Simulation, which will indicate that you pull down the Tools menu, then click on the Analog Artist button and finally click on the Simulation button.

**Note:** If at anytime during this tutorial you want to quit Cadence, make sure you save your work by selecting Design  $\Rightarrow$  Save and close the design windows by selecting Close from the menu. After you have closed all your working windows, select File  $\Rightarrow$  Exit and click Yes in the pop-up confirmation window to end the Cadence session.

### **Cadence File Organization**

To start a design in Cadence, you must first create a library where you can store your design cells. Every Library is associated with a technology file and it is the technology file that supplies

the color maps, layer maps, design rules, and extraction parameters required to view, design, simulate and fabricate your circuit. Cadence stores its files in libraries, cells, and cellviews.

A library (which actually appears as a directory in UNIX) contains cells (subdirectories), which in turn contain views. Each library contains a catalog of all cells, viewed along with the actual UNIX paths to the data files. Each cell in a library uses the same mask layers, colors, design rules, symbolic devices, and parameter values (i.e. the information contained in the technology file). A *cell* is the basic design object. It forms an individual building block of a chip or system. It is a logic, rather than a physical, design object. Each cell has one or more *views*, which are files that store specific data for each cell. A *cellview* is the virtual data file created to store information in Cadence. A cell may have many cellviews, signifying different ways to represent the same data represented by the cell (for example, a layout, schematic, etc).

# Example Organization:

Library: logic\_gates Cell: inv View: schematic View: symbol Cell: nand2 View: schematic View: symbol View: layout View: extracted Library: ripple\_carry\_adder Cell: 1bit\_adder View: schematic Cell: 2bit\_adder View: schematic

### **The Custom Design Process**

For a full custom design (as opposed to a coded/synthesized design using, e.g., Verilog HDL), the design process begins by creating a schematic. The schematic is then simulated to verify operation and optimize performance. A layout of the circuit is generated and checked for design rule violations (DRC). The layout is then extracted and a layout vs. schematic (LVS) comparison is run to ensure the cell layout exactly matches the schematic. Finally the extracted layout is simulated to observe the effect of *parasitics* that will be present on the fabricated chip. These post layout simulation are closer to reality and will show if your design would work if fabricated. In this tutorial you will create a schematic for a basic digital logic gate, and inverter, and perform some basic simulations on the schematic to verify it is functioning properly.

# Creating a Design Library <u>STEP 1</u>.

- In the Library Manager window, select File => New => Library to open the Create Library window shown below.

- Enter a Name for your library. The example shows the library name *project1*, but since you will probably be using the cells in this library (and adding more to it) choose a name like *lab*, *cmos*, or *digital*. Click Ok

- When the next dialog box appears, click on Attach to Existing Tech Library and click OK. Note that this dialog box may be hidden beneath another window.

- Choose NCSU\_TechLib\_ami06 as the technology file to be associated with your new library.

- Finally, click on the OK button and you now have an empty library to start adding cells to.

| 😽 New Library (on sati) 🛛 🗙                                                                                                                                                                                 |                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Library                                                                                                                                                                                                     |                                             |

| Name project1                                                                                                                                                                                               |                                             |

| Directory 🔄 /home/qureshiw/newcadence/                                                                                                                                                                      |                                             |

| Ib.defs     DCsignalgenerator IIbManager.log     New Folder IIbManager.log.cdslck     Slab5     project1     simulation     stimulusfiles     ade_viva.log     cds.lib     ddsLibEditor.log     display.drf | Technology File for New Library (on sati) 🗙 |

| File type: Olirectories                                                                                                                                                                                     | Technology File for library "project2"      |

| Design Manager                                                                                                                                                                                              | You can: 🔾 Compile an ASCII technology file |

| Use NONE                                                                                                                                                                                                    | Reference existing technology libraries     |

| Use No DM                                                                                                                                                                                                   | Attach to an existing technology library    |

| OK Apply Cancel Help                                                                                                                                                                                        | Do not need process information             |

| OK Apply Cancel Help                                                                                                                                                                                        | OK Cancel Help                              |

# **Creating a Schematic Cellview**

### **<u>STEP 2</u>**: Create a new schematic

- Go to the Library Manager window and click/select your library (for example "tutorial").

- Now select File => New => Cellview. Use the Create New File window that pops up to create the schematic view for an inverter cell.

- Enter the Cell Name "inv".

- Click on Type drop-down list and select Schematics. This is where you choose which Cadence tool you want to use and the appropriate View Name for each tool will be filled in automatically. Here we will be creating the schematic view.

- Click the OK button. The Virtuoso schematic editing tool will open with an empty Schematic Editing window as shown below.

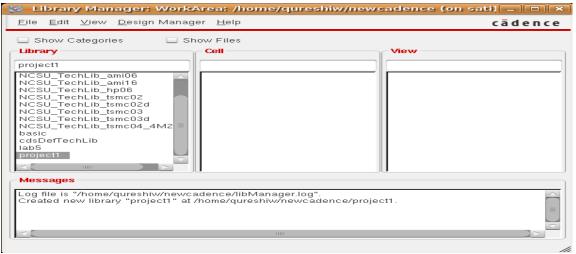

| 🔀 Library Manager: WorkArea: /home/qureshiw/ne                                                                                                                                                    | wcadence (on sati) 💶 🗖 🗙 |                                                        |                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------|------------------------|

| <u>File E</u> dit <u>V</u> iew <u>D</u> esign Manager <u>H</u> elp                                                                                                                                | cādence                  |                                                        | New File (on sati) 🛛 🗙 |

| Show Categories Show Files  Library  roject1  NCSU_TechLib_ami06  NCSU_TechLib_ami16  NCSU_TechLib_tsmc02  NCSU_TechLib_tsmc03  NCSU_TechLib_tsmc03  NCSU_TechLib_tsmc03  NCSU_TechLib_tsmc04_4M2 | cādence                  | File<br>Library<br>Cell<br>View<br>Type<br>Application | New File (on sati)     |

| basic<br>cdsDefTechLib<br>lab5<br>project1<br>Messages<br>Log file is "/home/qureshiw/newcadence/libManager.log".<br>Created new library "project1" at /home/qureshiw/newcadence/pr               | oject1.                  | Library path fi                                        | Schematics L           |

|                                                                                                                                                                                                   |                          |                                                        | OK Cancel Help         |

| aunc | h E    | jle | <u>E</u> di | : Vi  | вw | Cre | ate | C | hec | C C | ptio | ns | Mi | grat | е | ₩i | ndov  | <i>N</i> | NCS | SU . | Help |    |   |   |   |   |     |     |   |   |     |   |   |       |     | c    | ād   | Ιег | I C  |

|------|--------|-----|-------------|-------|----|-----|-----|---|-----|-----|------|----|----|------|---|----|-------|----------|-----|------|------|----|---|---|---|---|-----|-----|---|---|-----|---|---|-------|-----|------|------|-----|------|

| Þ    |        | -   |             | - fo  | C  | þ   |     | > | ۲   |     |      | 0  |    | •    | ۶ |    | Q     | 0        | 2   | •    | E.   |    |   | 5 | ι | 1 | . 4 | abc | - | Þ | *** |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     | Ĩ.   |

|      |        |     |             |       |    |     |     |   |     |     |      |    |    |      |   |    |       |          |     |      |      |    |   |   |   |   |     |     |   |   |     |   |   |       |     |      |      |     |      |

| nous | e L: s | how | Clic        | kinfo | 0  |     | _   | _ | _   | _   | _    |    | _  | _    | _ | M  | 1: sc | bHi      | Mou | iseP | onH  | nû | _ |   | _ |   | _   |     | _ |   | _   | _ | F | 3: sr | shH | iM4c | ouse | Pop | L Dr |

#### **<u>STEP 3</u>**: Add an nFET to the schematic

• In the Schematic Editing window Select Create => Instance to activate the Create Instance tool for adding components (transistors, sources, etc.) to your schematic. You can also invoke this tool by clicking on the *Instance* icon on the left-hand toolbar, or by typing the hot key 'I' with your mouse over the Schematic Editing window. Two windows (Component Browser window and Add Instance) will pop open.

| Virtuoso® Schematic Edito                                                                                                                                                                                                                                                   | r L Editing: project1 inv sch                                                                                                                                                       | ematic (on sati)                                                    |                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------|

| Launch <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>C</u> reate Chec <u>k</u> O <u>p</u> tons <u>M</u> igrate                                                                                                                                                                  | e <u>W</u> indow NCSU <u>H</u> elp                                                                                                                                                  |                                                                     | cādenc                  |

| 产 🛃 🗐 🥠 🗅 💷 🗙 🗊 🖻 🥱 🤞                                                                                                                                                                                                                                                       | IQ Q Q 🕅 I🏞                                                                                                                                                                         | 1 1 🚢 🛥 🖻                                                           |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             | · · · ·                                                                                                                                                                             |                                                                     |                         |

|                                                                                                                                                                                                                                                                             | amiPDN'<br>N⇒1.5u                                                                                                                                                                   |                                                                     |                         |

|                                                                                                                                                                                                                                                                             | 1 = 630m<br>m:1                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     | · · · · · · · · · ·     |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

|                                                                                                                                                                                                                                                                             |                                                                                                                                                                                     |                                                                     |                         |

| <u> </u>                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |                                                                     | <u>&gt;</u>             |

| 0 >                                                                                                                                                                                                                                                                         | M: schHiMousePopUp()                                                                                                                                                                | Instance (on sa                                                     | Cmd: Se                 |

| 0 >                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                   |                                                                     | Cmd: Se                 |

| Component Bro Commands Help cadence                                                                                                                                                                                                                                         | DDA D                                                                                                                                                                               |                                                                     | Cmd: Se                 |

| Component Bro _ 🗆 🗙                                                                                                                                                                                                                                                         | Add                                                                                                                                                                                 |                                                                     | Cmd: Se                 |

| ) ><br>Component Bre     ><br>Commands Help cādence                                                                                                                                                                                                                         | Cell nmos4                                                                                                                                                                          |                                                                     | Cmd: Se                 |

| Component Bro N                                                                                                                                                                                                                                                             | Add<br>Library NCSU Analor<br>Cell rmos4<br>View symbol<br>Names                                                                                                                    | g Parts                                                             | Cmd: Se                 |

| Component Bre X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten Filter *                                                                                                                                                                                   | Add<br>Library NOSU Analor<br>Cell rmos4<br>View symbol<br>Names<br>Array Row                                                                                                       | s 1 Co                                                              | Cind: Se                |

| Component Bro NCSU_Analog_Parts<br>Flatten                                                                                                                                                                                                                                  | Add<br>Library NCSU Analor<br>Cell rmos4<br>View symbol<br>Names                                                                                                                    | g Parts                                                             | Candi Se                |

| Component Bro - X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten -<br>Filter * <br>Contents<br>Contents<br>Current_Sources<br>Diodes                                                                                                                      | Add<br>Library NOSU Analor<br>Cell rmos4<br>View symbol<br>Names<br>Array Row                                                                                                       | s 1 Co                                                              | Cind: Se                |

| Component Bro _ X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten _<br>Filter *<br>Contents<br>Contents<br>Current_Sources<br>Diodes<br>H_Spice_Only<br>Microwave_Parts                                                                                    | Add<br>Library NOSU Analor<br>Cell rmos4<br>View symbol<br>Names<br>Array Row                                                                                                       | s 1 Co                                                              | Cind: Se                |

| Component Bre X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten<br>Filter * <br>Uncategorized<br>CONTENTS<br>Current_Sources<br>Diodes<br>H_Spice_Only<br>Microwave_Parts<br>Misc_Parts                                                                    | Add<br>Library NOSU Analor<br>Cell rmos4<br>View symbol<br>Names<br>Array Row                                                                                                       | s 1 Co                                                              | Diumns 1<br>Upside Down |

| Component Bro NCSU_Analog_Parts<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten Fitter *1<br>Uncategorized<br>CONTENTS<br>CONTENTS<br>CUNTENTS<br>Diodes<br>Diodes<br>H_Spice_Only<br>Microwave_Parts<br>Microwave_Parts<br>N_Transistors<br>P_Transistors | Add<br>Library NCSU Analor<br>Cell rmos4<br>View symbol<br>Names<br>Array Row<br>(2 Rotate<br>Model name                                                                            | s 1 Co                                                              | Diumns 1<br>Upside Down |

| Component Bro - X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten -<br>Filter *1<br>Uncategorized<br>CONTENTS<br>CONTENTS<br>Diodes<br>Diodes<br>Diodes<br>Diodes<br>Microwsve_Parts<br>Microwsve_Parts<br>N_Transistors<br>Parasitic_Devices<br>R_Lo      | Add<br>Library NCSU Analor<br>Cell rinos4<br>View symbol<br>Names<br>Array Row<br>(12 Rotate<br>Model name<br>Model Type                                                            | s 1 Co<br>ALSideways<br>ami06N<br>e system                          | Diumns 1<br>Upside Down |

| Component Bro _ X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten _<br>Filter * <br>Current_Sources<br>Diodes<br>H_Spice_Only<br>Misc_Parts<br>N_Transistors<br>P_Transistors<br>Parasitic_Devices                                                         | Add<br>Library NCSU Analor<br>Cell rimos4<br>View symbol.<br>Names<br>Array Row<br>Array Row<br>Array Row<br>Model name<br>Model Type<br>Multiplier                                 | s 1 Co<br>A Sideways<br>ami06N<br>• system<br>1                     | Diumns 1<br>Upside Down |

| Component Bro - X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten -<br>Filter *1<br>Uncategorized<br>CONTENTS<br>CONTENTS<br>Diodes<br>Diodes<br>Diodes<br>Diodes<br>Microwsve_Parts<br>Microwsve_Parts<br>N_Transistors<br>Parasitic_Devices<br>R_Lo      | Add<br>Library Nesu Analor<br>Cell rimos4<br>View symbol<br>Names<br>Array Row<br>Array Row<br>Model name<br>Model name<br>Model Type<br>Multiplier<br>Fingers                      | s 1 Co<br>A Sideways (<br>system<br>1<br>1                          | Diumns 1<br>Upside Down |

| Commands Help cadence                                                                                                                                                                                                                                                       | Add<br>Library NOSU Analor<br>Cell rimos4<br>View symbol<br>Names<br>Array Row<br>Array Row<br>Array Row<br>Model name<br>Model Type<br>Multiplier<br>Fingers<br>Width (grid units) | s 1 Co<br>A Sideways (<br>ami06N<br>• system<br>1<br>1<br>10        | Diumns 1<br>Upside Down |

| Component Bro - X<br>Commands Help cadence<br>Library NCSU_Analog_Parts<br>Flatten -<br>Filter *1<br>Uncategorized<br>CONTENTS<br>CONTENTS<br>Diodes<br>Diodes<br>Diodes<br>Diodes<br>Microwsve_Parts<br>Microwsve_Parts<br>N_Transistors<br>Parasitic_Devices<br>R_Lo      | Add<br>Library NOSU Analor<br>Cell rmos4<br>View symbol.<br>Names<br>Array Row<br>Array Row<br>Array Row<br>Model name<br>Model Type<br>Multiplier<br>Fingers<br>Width (grid units) | s 1 Co<br>Sideways<br>ami06N<br>• system<br>1<br>1<br>10<br>1. Su M | Browse                  |

- In the Component Browser window, under Library select NCSU\_Analog\_Parts. A list of parts will be displayed near the bottom of this window. From the parts list, click on N\_transistors and a list of of available nFET transistor elements will be displayed. Pick up the nmos4 element by clicking on it. This will attach the component to your mouse pointer.

- If necessary, click on the Rotate, Sideways, or Upside-down buttons in the Add Instance window to manipulate the component you are adding.

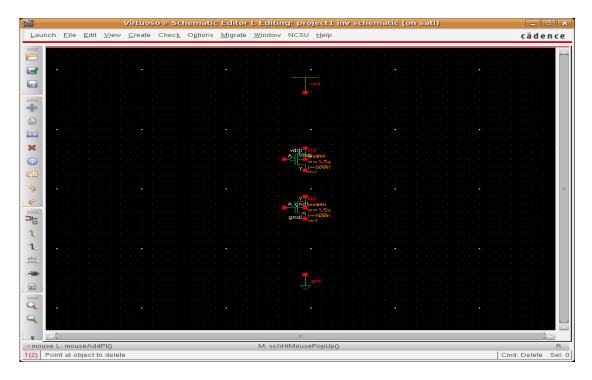

- Click on schematic area of the Schematic Editing window (main black area of the window) and the nmos4 component will appear in your schematic. Clicking on the schematic window again will add another copy of the component (don't do this). Pressing ESC on the keyboard will end the Add Instance function (but don't do this yet).

# **<u>STEP 4</u>**: Add other components to the schematic

- In Component Browser window, go to the P-Transistors category in NCSU\_Analog\_Parts, and pick up pmos4 and add it to your schematic. Place it above the nFET as appropriate for a CMOS inverter. If you need to move a component, press "ESC" and left-click on the component and drag it to a new location. Pressing "ESC" will cancel the Add Instance command so you will need to restart it to add more components.

- In Component Browser window, go to the Supply-nets category and pick up vdd (supply voltage) and gnd (ground reference) and add them above and below, respectively, the MOSFET components. Now the Schematic Editing window looks like the figure below.

# STEP 5: Add I/O pins

- In the Schematic Editing window select Create => Pin (or use hot key 'p') to add an input pin.

- In the Add Pin window enter 'A' for the Pin Name and select input for the Direction.

- Click on the Schematic Editing window and drop the pin to the left of the transistors (between the gate inputs).

• Follow the same procedure to add output pin 'Y' to the right of the transistors between the drain nodes. Be sure to use the correct pin direction. Press "ESC" when you are done.

|                                  | Add P       | in (on sati)  | ×                   |  |  |  |  |  |  |  |

|----------------------------------|-------------|---------------|---------------------|--|--|--|--|--|--|--|

| Pin Names                        | A           |               |                     |  |  |  |  |  |  |  |

| Direction                        | input -     | Bus Expansion | 🖲 off 🔾 on          |  |  |  |  |  |  |  |

| Usage                            | schematic 🗧 | Placement     | 🖲 single 🔾 multiple |  |  |  |  |  |  |  |

| Attach Net Expression:   No  Yes |             |               |                     |  |  |  |  |  |  |  |

| Property Name                    |             |               |                     |  |  |  |  |  |  |  |

| Default Net Name                 | -           |               |                     |  |  |  |  |  |  |  |

| Font Height                      | 0.0625      |               | stick.              |  |  |  |  |  |  |  |

| A Rotate                         | ▲ Sideways  | 🗲 Upside Down | Show Sensitivity >> |  |  |  |  |  |  |  |

|                                  |             | Hide Canc     | el Defaults Help    |  |  |  |  |  |  |  |

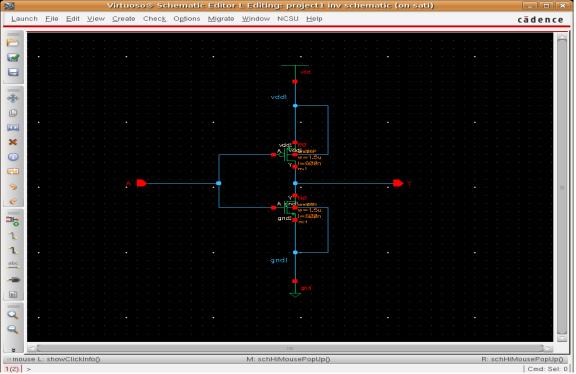

# **STEP 6:** Add wire connections

- In the Schematic Editing window select Create => Wire (or use hot key 'w') to begin placing wires which will connect the terminals of the components and pins in the schematic.

- Wire the schematic as appropriate for a CMOS inverter. Be sure to connect the *bulk* terminal of each transistor (nMOS to ground, pMOS to VDD). Press **ESC** to end wiring.

# **<u>STEP 7</u>: Setting global labels**

- In the Schematic Editing window type the letter 'l' to invoke the labeling tool. Since we will be using the same vdd and gnd supplies for all our cells, we want to make a *global declaration* for these labels. Cadence uses the '!' symbol after a label-name to indicate a global label, i.e., one that is common to all cells in a design.

- In the label pop-up window, enter the Name vdd!

- Move your mouse to the Schematic Editing window and drop the vdd! label on the wire that connects to the vdd pin.

- Repeat this procedure to label the global gnd! net. Press ESC when you are done.

Final schematic of an inverter

## **STEP 8:** Check and Save the cellview

Now that you are familiar with the schematic editing tool, explore the menu commands in the Schematic Editing window to do the following:

- Check the cell for errors. If errors exist the error section will blink in the Schematic Editing window.

- Save the cellview.

# **General Editing Tips**

<u>Mouse Buttons</u>: In most Cadence tools, the left mouse button is used to select components, wires, etc., and the middle mouse button can be used to change object properties, e.g., the width and length of a transistor.

<u>Moving Objects</u>: If you want to move any object, just move the cursor on top of the object and type 'm'. The object will then move with the cursor. Or you can select the objects to be moved by left-click and drag to draw a box around the objects. After highlighting the objects to be moved, type 'm' and the highlighted objects will move with your cursor.

<u>Deleting Objects</u>: If you want to delete an object, move the cursor on top of the object and hit the "DEL" key. You can also highlight an object or a group of objects by drawing a box around it, as described above, and pressing the "DEL" key.

<u>Undo Operations</u>: When you make a mistake (accidentally delete a component, etc.), you can undo the action by click on the <u>Undo</u> icon in the toolbar.

BindingKey: The following "hot keys" are available for the schematic editing tool.

- 1). Press 'p' to add pins

- 2). Press 'q' on the device/instance to edit properties for the device

- 3). Press 'w' to add wires

- 4). Press 'f' fit the schematic in your schematic window

- 5). Press 'z' to zoom in the window

- 6). Press "shift+z" to zoom out the window

- 7). Press 'l' to label a wire

- 8). Press "Up" and "Down" arrows to move up and down within a schematic window

- 9). Press "ESC" to terminate an operation in the schematic window

- 10). Press 'u' to undo an operation in the schematic window

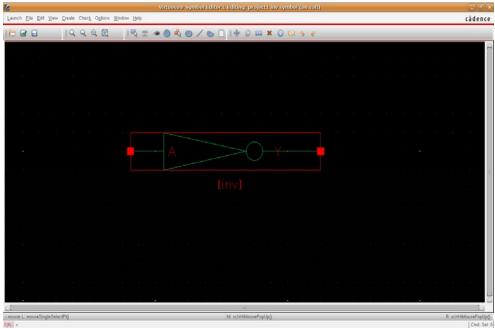

### **<u>STEP 9</u>**: Create a symbol

- In the Schematic Editing window, select Create => Cellview => From Cellview.

- In the Cellview From Cellview window that pops up, you should notice source (From View Name) set to *schematic* and the destination (To View Name) set to *symbol*, which is linked to the Composer-Symbol tool. You should not have to modify this window.

- Click on OK in the Cellview From Cellview window.

- A Symbol Generation Options window will popup. Keep the default values and select OK.

|                                  | Cellview F  | rom Cellview (on s               | ati) X                    |                                                               |                   |                  |                                        |

|----------------------------------|-------------|----------------------------------|---------------------------|---------------------------------------------------------------|-------------------|------------------|----------------------------------------|

| Library Name                     | project1    |                                  | Browse                    | -                                                             | Symbol Generatio  | on Options (on s | ati) 🗙                                 |

| Cell Name                        | inv         |                                  |                           | Library Name<br>project1                                      | Cell Name         |                  | View Name<br>symbol                    |

| From View Name                   | schematic 🔽 | To View Name<br>Tool / Data Type | symbol<br>schematicSymbol | Pin Specifications<br>Left Pins A<br>Right Pins Y<br>Top Pins |                   |                  | Attributes<br>List<br>List<br>List     |

| Display Cellview<br>Edit Options | ⊻<br>⊻      |                                  |                           | Bottom Pins<br>Exclude Inherited Col<br>None Q All Q          |                   |                  | List                                   |

|                                  |             | OK Cancel                        | Defaults Apply Help       | Load/Save 🗌                                                   | Edit Attributes 📃 | Edit Labels 🗌    | Edit Properties 🔒<br>Cancel Apply Help |

- A Symbol Generation Options window will popup. Keep the default values and select OK.

- The Symbol Editing window will pop up showing the default symbol, a rectangle with red square dots for input and out pins. You can keep this symbol, but it would be helpful if you modified it to a more meaningful symbol (such as a triangle for an inverter). Explore the options on this window and the tips below to define your symbol graphic.

- When the symbol is complete, save it. In the Symbol Editing window select File => Save or click on the Save icon at the top of the toolbar.

- In the Symbol Editing window, select File => Close to close the symbol.

Final inverter symbol

# Symbol Editing Tips

General Notes:

• The red box around your symbol is called a selection box. When you place your symbol in a schematic, this box represents the area you can click in to select the symbol. You can

change the size of selection box. It is a good practice to fit the symbol entirely within the red box; otherwise, you may not easily be able to select it when you instantiate it later on.

- The red square dots indicate the pin connections.

- [@InstanceName] and [@PartName] are display variables, which you may keep or delete. These are generally annoying for small cells/symbols but can be useful for higher-level circuits.

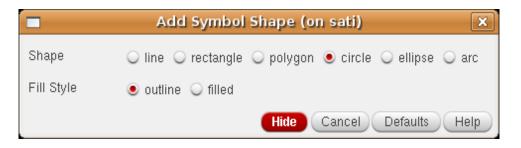

<u>Drawing Lines:</u> To draw a line, move your cursor to the Line icon (the icon with a descending line) and click on the left mouse button. Icons are to the left of the symbol window. Move your cursor to the location where you want to draw a line and click on the left mouse button. If you draw a closed object, all you have to do is to click on the points where you want to change the direction of the line. However, if you are drawing just a straight line, you need to double click the left mouse button on the end point of the line to signify the completion of drawing the line. Drawing Shapes: To draw a circle (or any other shape), first click on the Line icon and then click on the options icon (the second to last icon). A pop-up menu will appear in which you can select different shapes and fill styles. Then move your cursor to the location where you want to draw the circle/shape and left-click. That is the location of the center of your circle. Move your mouse so that the circle is as big as you desire it to be and then click on the left mouse button again.

# Simulation with Virtuoso Analog Design Environment (ADE)

To verify a circuit is working and test the functionality of the schematic we must simulate the circuit. For this we will use the Cadence Virtuoso analog simulation tool. For now we will just run a simple transient analysis to confirm the circuit designed above is operating as an inverter should be. Additional information for running simulations with Cadence tools is provided in Tutorial C.

### **<u>STEP 10</u>**: Launch the Virtuoso analog simulation tool

With your "inv" schematic open, in the Schematic Editing window select Launch => ADE L, and the Virtuoso Analog Design Environment window will open.

(You can also launch this tool from the CIW by selecting Launch => ADE L in the CIW.)

|                  | iuoso          | ® Analog         | Design I          | Environr        | nent (1) -         | projec          | tl inv        | schema       | itic (on sati) | _     |                     |

|------------------|----------------|------------------|-------------------|-----------------|--------------------|-----------------|---------------|--------------|----------------|-------|---------------------|

| S <u>e</u> ssion | Set <u>u</u> p | <u>A</u> nalyses | <u>V</u> ariables | <u>O</u> utputs | <u>S</u> imulation | <u>R</u> esults | <u>T</u> ools | <u>H</u> elp |                | cād   | ence                |

| III Status: F    | Ready          | T=27 C S         | iimulator: sp     | ectre           |                    |                 |               |              |                |       |                     |

| Design Va        |                | Value            | Â                 | Analyses        | Enable             | -               | Arg           | uments       | _              | <<br> | AC     DC     Trans |

|                  |                |                  | ≣                 | Outputs         | e/Signal/Exp       | r ∧∣Va          | Iue   Plo     | it  Save     | Save Options   |       | <u>1</u> .          |

|                  |                |                  |                   |                 |                    |                 |               |              |                |       |                     |

| >                |                |                  |                   | Plotting m      | iode: Rep          | lace            |               |              |                |       |                     |

| 7 Choose         | Desigr         | ۱                |                   |                 |                    |                 |               |              |                |       |                     |

- In Virtuoso Analog Design Environment, click on Setup => Simulator/Directory/Host.

- Choose **spectre** as the Simulator (if not default).

- The default Project Directory should be "./simulation". This points to a directory named "simulation" inside of the directory you launched Cadence from. This is where your simulations files and results will be saved. You may set the Project Directory to any valid path, but you might find it useful to keep all simulations in one directory. To run multiple simulations on the same cell, you can use different paths for each simulation. Note that upon closing and reopening this screen, the project directory will automatically be transformed to the absolute path name: /egr/courses/unix/ECE/410/<**USERNAME**>/cadence/simulation/

- When the Virtuoso Analog Design Environment opens you have to click Setup => Design to specify the library and cell, for example "tutorial" and "inv".

| 🔲 Choosing Si     | mulator/Directory/Host Virtuoso® Analog Desit 🗙 |

|-------------------|-------------------------------------------------|

| Simulator         | spectre                                         |

| Project Directory | ./simulation                                    |

| Host Mode         | 💿 local 🔾 remote 🔾 distributed                  |

| Host              |                                                 |

| Remote Directory  |                                                 |

|                   | OK Cancel Defaults Apply Help                   |

- In Virtuoso Analog Design Environment, click on Setup => Environment.

- Next to "Use SPICE Netlist Reader(spp):", click the box "Y". This is necessary because the AMI06 transistor model libraries use SPICE netlist syntax. Click OK to close this window.

|                                | Environment Options (on sati)                |

|--------------------------------|----------------------------------------------|

| Switch View List               | spectre cmos_sch cmos.sch schematic veriloga |

| Stop View List                 | spectre                                      |

| Parameter Range Checking File  |                                              |

| Analysis Order                 |                                              |

| Print Comments                 |                                              |

| userCmdLineOption              |                                              |

| Automatic output log           |                                              |

| Use SPICE Netlist Reader(spp): | V N                                          |

| savestate(ss):                 | I Y I N                                      |

| recover(rec):                  | Y N                                          |

|                                | OK Cancel Defaults Apply Help                |

#### **<u>STEP 11</u>**: Set up stimulus

The schematic defines the components within the cell but does not define the control signals (typically voltage sources) necessary to test the operation of the circuit, such as the power supply voltage and an input voltage signal. These signals are referred to as the *stimulus*, and here we will use a *spectre* stimulus text file to define these signals.

You will need to use a text editor in order to create a stimulus text file. You can use any editor you are familiar with. You can name the stimulus file any name with a .scs or .txt file extension, and put it wherever you wish. In this tutorial, we will call the file "stimulus.txt" and place it in your ECE410 Cadence directory. If you are new to UNIX, you may want to "NEdit" or "GEdit" by doing the following:

- Open a terminal screen (or use any one that is already open).

- Make sure you are in your Cadence directory. If unsure, type cd /egr/courses/unix/ECE/410/<USERNAME>/cadence

- Type "nedit &" or "gedit &" to create a new file.

- Once you have opened a text editor, type in the following five lines to define the simulator language (*spectre*), the DC supply voltage and a square wave pulse input voltage that will be useful for a transient analysis simulation to verify functionality of the inverter circuit. Note that the input waveform used may vary with the type of analysis needed, although the supply voltage source will generally remain constant.

- o simulator lang=spectre

- o global gnd!

- o vdd (vdd! 0) vsource dc=3

- o gnd (gnd! 0) vsource dc=0

- o V1 (A 0) vsource type=pulse val0=0 val1=3 delay=0 rise=0.05n

fall=0.05n width=10n period=20n

- Note: Each bulleted item represents one line in your stimulus file. The third bullet item (voltage pulse) is broken into two lines due to the document margins, but should only take up one line in your stimulus file.

- Make sure that you always end the last line by pressing Enter. This adds a new line character to the line, and informs the simulator that the voltage definition is complete. If you do not do this, you will likely get a netlist read error when you try to Netlist and Run the simulation.

- Save the text file. If you are using *Nedit*, this can be done by

- Selecting Files => Save As

- In the "New File Name:" box, the current path will be displayed. Click on the blinking cursor and add "stimulus.txt" to the path.

- Click OK. This will save the file

- You can exit the text editor at this point (nedit: select File=>Exit). However, you may want to keep it open if you plan on making changes to the file during simulation.

# **Stimulus File Tips**

The voltage sources above are defined using *spectre* syntax. The DC supply voltage named "vdd" is between nodes vdd! and 0 (ground) with value of 3V. The input square wave is defined using the *spectre pulse* syntax

```

<vname> (node+ node-) vsource type=pulse val0=min_voltage val1=max_voltage

delay=delay_length rise=rise_time fall=fall_time width=pulse_width

period=period_length

```

where the default units are volts and seconds. The 'n' on the time values sets them to nanoseconds (i.e. n" is a 10<sup>-9</sup> multiplier). Although you can vary the timing values as necessary to meet simulation goals, the rise and fall times listed are good for the AMI-C5N technology and should not be modified unless you are sure you know what you are doing.

- Once you have written a stimulus file, open (refocus) the Virtuoso Analog Design Environment window. Click on Setup => Simulation Files.

- Click on the box that is labeled "Stimulus File" so that a blinking cursor appears in it.

- Click the "..." button to open a file browser window.

- Navigate to where you have saved the file "stimulus.txt" if you have followed the tutorial exactly, it should appear in the default directory opened by the file browser.

- Click on the name "stimulus.txt" and then click OK. The file browser should close, and the absolute pathname for your stimulus file should appear in the "Stimulus File" box.

- Click OK to apply changes and close this window.

| spectre1: Simulation Files Setup (on sati)                                 |            | × |

|----------------------------------------------------------------------------|------------|---|

| Paths/Files Vector Files                                                   |            |   |

| Files/Paths                                                                |            | 1 |

| E- Include Paths<br>└──            └──             └──                     |            |   |

| d→ Definition Files                                                        |            |   |

| └── <click a="" add="" file="" here="" to=""></click>                      | ×          |   |

| ✓ /egr/courses/personal/ece410/ <username>/cadence/stimulus.scs</username> | $\bigcirc$ |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            |   |

|                                                                            |            | 1 |

| OK Cancel A                                                                | pply Help  |   |

# **STEP 12: Setup Model Files**

- In Virtuoso Analog Design Environment, click on Setup => Model Libraries...

- If you have correctly set up your ECE410 Cadence environment, two Model Library Files should already appear, "ami06N.m" and "ami06P.m". If so, you may exit this dialog by pressing OK.

- You can add the necessary Model Library Files by

- Click the bottom "Model Library File" box

- o Type "/opt/soft/NCSU-CDK-1.6.0.beta/models/spectre/nom/ami06N.m"

- Click the "Add" button. This should add the model to the Model Library File list and clear the Model Library File box

- Repeat the process or "/opt/soft/NCSU-CKD-1.6.0.beta/models/spectre/nom/ami06P.m"

- Your Model Library Setup dialog box should look like the one below. Once it does, you can click "OK" to close the dialog.

| spectre1: Model Library Setup (on                                                                                                                                     | sati) 🛛 🗙            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Model File<br>└opt/soft/ncsu-cdk-1.6.0.beta/models/spectre/nom/ami06N.m<br>/opt/soft/ncsu-cdk-1.6.0.beta/models/spectre/nom/ami06P.m<br>Click here to add model file> | Section              |

|                                                                                                                                                                       | OK Cancel Apply Help |

### **STEP 13**: Setup analysis

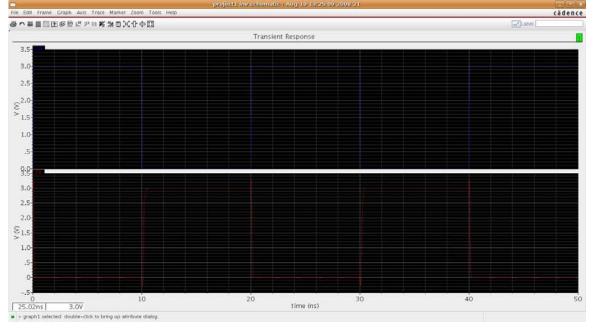

With the stimulus defined, we need to choose what type of analysis we wish to perform. Different analyses are useful for getting a variety of different data from the simulations. Here we wish to simulate the response of our inverter to a simple square wave input and verify that the output is indeed being inverted. For this we will setup a *transient* (over time) analysis.

Alternative analysis types, including DC analysis, that are used to simulate different performance characteristics of a circuit are covered in Tutorial C.

- In Virtuoso Analog Design Environment window, select Analyses => Choose.

- In the window that pops up, select **tran** to choose a transient analysis.

- Enter the time limits for simulation by entering a *Stop Time* of "**50n**".

- Choose Enabled at the bottom of the screen and press OK.

| 🗖 Choosir                           | ng Anal            | iyses  | Virtuoso® | Analog Design E 🗙 |  |  |

|-------------------------------------|--------------------|--------|-----------|-------------------|--|--|

| Analysis                            | 💌 tran             | 🔾 dc   | 🔾 ac      | 🔾 noise           |  |  |

|                                     | 🔾 xf               | 🔾 sens | 🔾 dcmatch | 🔾 stb             |  |  |

|                                     | 🔾 pz               | 🔾 sp   | 🔾 envlp   | 🔾 pss             |  |  |

|                                     | 🔾 pac              | 🔾 pstb | 🔾 pnoise  | ⊖ p×f             |  |  |

|                                     | 🔾 psp              | 🔾 qpss | 🔾 qpac    | 🔾 qpnoise         |  |  |

|                                     | 🔾 qp×f             | 🔾 qpsp |           |                   |  |  |

|                                     | Transient Analysis |        |           |                   |  |  |

| Stop Time                           | 50n                |        |           |                   |  |  |

| Accuracy Defaults (errpreset)       |                    |        |           |                   |  |  |

| 🗆 conservative 🔲 moderate 🔲 liberal |                    |        |           |                   |  |  |

| 🔲 Transier                          | nt Noise           |        |           |                   |  |  |

| Enabled ⊻                           |                    |        |           | Options           |  |  |

| OK Cancel Defaults Apply Help       |                    |        |           |                   |  |  |

# **STEP 13:** Setup output traces

- In Virtuoso Analog Design Environment window, select Outputs => to be plotted => Select on Schematic. This will activate the Schematic Window allowing you to pick which signals (nets/wires) you would like to have plotted during the simulation.

- In the Schematic Window click on the wire that is the input to your inverter and also click on the output wire. This will complete the simulation setup.

| 🍸 🛛 Virtuoso® Analog Design Environment (1) - project1 inv schematic (on sati) 📃 🗖                                                                          |              |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|

| S <u>e</u> ssion Set <u>up</u> <u>A</u> nalyses <u>V</u> ariables <u>O</u> utputs <u>S</u> imulation <u>R</u> esults <u>T</u> ools <u>H</u> elp <b>cāde</b> | nce          |  |  |  |  |

| Ⅲ Status: Selecting outputs to be plotted T=27 C Simulator: spectre                                                                                         |              |  |  |  |  |

|                                                                                                                                                             | AC           |  |  |  |  |

|                                                                                                                                                             | DC<br>Trans  |  |  |  |  |

| ■ Outputs<br>Name/Signal/Expr //alus  Plot  Save   Save Options   △                                                                                         | +® →<br>+® → |  |  |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                      | ×            |  |  |  |  |

|                                                                                                                                                             |              |  |  |  |  |

|                                                                                                                                                             |              |  |  |  |  |

| Plotting mode: Replace                                                                                                                                      | 104          |  |  |  |  |

| > Select on Schematic Outputs to Be Plotted                                                                                                                 |              |  |  |  |  |

| 7 Select On Schematic                                                                                                                                       |              |  |  |  |  |

# STEP 14: Run simulation

- In the Virtuoso Analog Design Environment window select Simulation => Netlist and Run. Or, click the green arrow button on the screen.

- When the simulation is complete, the CIW should show "Reading Simulation Data ...... Successful". If the simulation was not successful, go to Simulation => Output Log in your Virtuoso Analog Design Environment to find out what the problem was.

- If the simulation results show a typical inverter response (i.e. output high when input is low and vice versa) then the circuit is working properly. If not, you will need to go back to the schematic to track down the problem and rerun simulations until you get the proper response.

- To separate input and output signals, in the Waveform Window click on Axis => Strips.

- When this simulation"s results are correct, you have completed Tutorial A.

### **<u>Optional</u>:** Saving and loading the simulation state

The Analog Design Environment state can be saved so that the settings do not need to be manually entered each time a design is simulated.

To save the simulation state, in the Virtuoso Analog Design Environment window select Session => Save State

| Saving State \       | /irtuoso®                                 | Analog Desig         | n Environment (1)   | (on sati) 🗙  |

|----------------------|-------------------------------------------|----------------------|---------------------|--------------|

| Save State Option    | ۲                                         | 🖲 Directory 🔾 Cel    | lview               |              |

| Directory Options    |                                           |                      |                     |              |

| State Save Directory | ~/.artis                                  | t_states             |                     | Browse       |

| Save As              | state1                                    | state1               |                     |              |

| Existing States      |                                           |                      |                     | -            |

|                      |                                           |                      |                     |              |

|                      |                                           |                      |                     |              |

|                      |                                           |                      |                     | ]            |

| Cellview Options     | project1                                  |                      | 10                  |              |

|                      |                                           |                      |                     |              |

| Cell                 | inv                                       |                      | Browse              |              |