### No Excess Babbage - Design Considerations for the Interface to a Systolic Matrix Processor

T. Shaw B.Sc., B.E. (Hons)

A thesis submitted to the Department of Electrical and Electronic Engineering, The University of Adelaide, to meet the requirements for award of the degree of Master of Engineering Science by research.

May 1995

## Contents

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iv                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | viii                                                  |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ix                                                    |

| Statement of Originality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | х                                                     |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xi                                                    |

| 1 Introduction         1.1 Systolic Arrays         1.2 Wavefront Arrays         1.3 Standard Systolic/Wavefront Arrays         1.3.1 Systolic and Wavefront SIMD Array Processors         1.3.2 Multi-bit SIMD Processing Arrays         1.3.3 Configurable Processing Arrays         1.4 Conclusion                                                                                                                                                                                                                                                                                              | 2<br>3<br>5<br>7<br>8                                 |

| <ul> <li>2 The System</li> <li>2.1 The University of Adelaide Systolic Processing Array</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <ul> <li>3 Algorithms</li> <li>3.1 Memory Subsystem: An Overview</li> <li>3.2 Matrix Multiplication</li> <li>3.2.1 Partitioning</li> <li>3.3 Solution of Sets of Linear Equations</li> <li>3.4 Gauss-Jordan Elimination</li> <li>3.4.1 Block Version</li> <li>3.4.2 Determining the Inverse of the Pivot Block</li> <li>3.4.3 Implementation on the Proposed Memory Architecture</li> <li>3.4.4 Inverting Rather Than Solving a Set of Matrix Equations</li> <li>3.4.5 Solving Sets of Equations That Don't Fit Into the Cache</li> <li>3.4.6 Iteratively Improving a Set of Solutions</li> </ul> | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

| <ul> <li>3.5 The Discrete Fourier Transform</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                                                     |

| 4 | Arit                                                                                                  | hmetic 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.1                                                                                                   | Signed-Digit, or Carry-Propagation Free, Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                                                                       | 4.1.1 Why SD Arithmetic 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                                                                                                       | 4.1.2 Sign Magnitude Specifics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                                       | 4.1.3 Conversion To and From Signed Digit and Two's Complement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                                       | 4.1.4 Signed Digit Implementation 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                                       | 4.1.5 VLSI Layout and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.2                                                                                                   | Byte Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                       | 4.2.1 Newton-Raphson Iterative Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                       | 4.2.2 Byte Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 4.3                                                                                                   | $8 \times 8$ Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 1.0                                                                                                   | 4.3.1 Pipelined Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.4                                                                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.4                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5 | Add                                                                                                   | ress Generator 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0 |                                                                                                       | 5.0.1 Matrix Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                                       | 5.0.2 Parallelizing and Expanding the Difference Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                                       | 5.0.3 Example Mappings on the Difference Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.1                                                                                                   | Address Generator Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 0.1                                                                                                   | 5.1.1 Sign Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                                                                       | 5.1.2 Initialisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   |                                                                                                       | 5.1.3 Dimension Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                                       | 5.1.4 Complete Decrement Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.2                                                                                                   | 5.1.5 Multiplexer Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 52                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.3                                                                                                   | After Calculating the Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6 | $\begin{array}{c} 5.3 \\ 5.4 \end{array}$                                                             | After Calculating the Offset       101         Conclusion       102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6 | 5.3<br>5.4<br><b>Me</b> i                                                                             | After Calculating the Offset       101         Conclusion       102         nory Interface       103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 | 5.3<br>5.4<br><b>Me</b><br>6.1                                                                        | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6 | 5.3<br>5.4<br><b>Me</b> i                                                                             | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       103         Applying and Extracting the Outer Product       103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6 | 5.3<br>5.4<br><b>Me</b><br>6.1<br>6.2                                                                 | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       104         Applying and Extracting the Outer Product       105         6.2.1       Extracting the Outer Product       105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 | 5.3<br>5.4<br><b>Me</b><br>6.1                                                                        | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       104         Applying and Extracting the Outer Product       105         6.2.1       Extracting the Outer Product       103         Memory Overview       104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

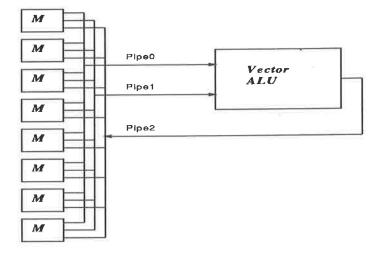

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       104         Applying and Extracting the Outer Product       105         6.2.1       Extracting the Outer Product       105         Memory Overview       104         6.3.1       Difference From Vector Memory Systems       104                                                                                                                                                                                                                                                                                                                                                                                                                                  |

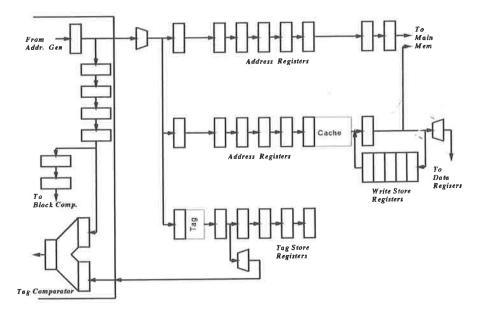

| 6 | 5.3<br>5.4<br><b>Me</b><br>6.1<br>6.2                                                                 | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       104         Applying and Extracting the Outer Product       103         6.2.1       Extracting the Outer Product       103         Memory Overview       104         6.3.1       Difference From Vector Memory Systems       104         Cache       106                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset       101         Conclusion       102         aory Interface       103         Introduction       104         Applying and Extracting the Outer Product       103         Memory Overview       104         6.3.1       Difference From Vector Memory Systems       104         Cache       106         6.4.1       Cache Size       106                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       105         Applying and Extracting the Outer Product       105         6.2.1       Extracting the Outer Product       106         Memory Overview       104         6.3.1       Difference From Vector Memory Systems       104         Cache       106         6.4.1       Cache Size       106         6.4.2       Block Size       106                                                                                                                                                                                                                                                                                                                        |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset101Conclusion102nory Interface103Introduction104Applying and Extracting the Outer Product1056.2.1Extracting the Outer Product105Memory Overview1046.3.1Difference From Vector Memory Systems104Cache1061066.4.1Cache Size1066.4.3Associativity107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset       101         Conclusion       102         nory Interface       103         Introduction       103         Applying and Extracting the Outer Product       103         6.2.1       Extracting the Outer Product       103         Memory Overview       104         6.3.1       Difference From Vector Memory Systems       104         6.4.1       Cache       106         6.4.2       Block Size       106         6.4.3       Associativity       107         6.4.4       Latency After a Miss       108                                                                                                                                                                                                                                                      |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset101Conclusion102nory Interface103Introduction104Applying and Extracting the Outer Product1056.2.1Extracting the Outer Product105Memory Overview1046.3.1Difference From Vector Memory Systems1046.4.1Cache1066.4.2Block Size1066.4.3Associativity1076.4.4Latency After a Miss1086.4.5Write Policy108                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset101Conclusion102nory Interface103Introduction104Applying and Extracting the Outer Product1056.2.1Extracting the Outer Product106Memory Overview1046.3.1Difference From Vector Memory Systems1046.4.1Cache Size1066.4.2Block Size1066.4.3Associativity1076.4.4Latency After a Miss1086.4.5Write Policy1096.4.6Implementation109                                                                                                                                                                                                                                                                                                                                                                                                                                        |

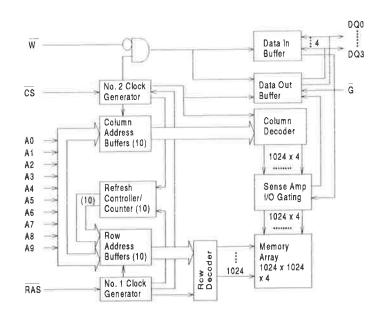

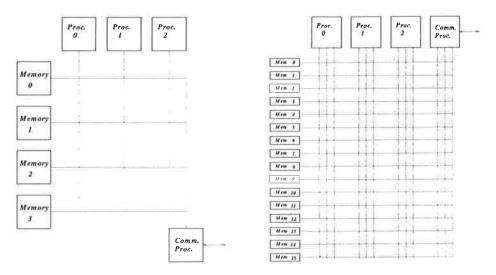

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>              | After Calculating the Offset101Conclusion102nory Interface103Introduction103Applying and Extracting the Outer Product1036.2.1Extracting the Outer Product1046.3.1Difference From Vector Memory Systems104Cache1066.4.1Cache Size1066.4.2Block Size1066.4.3Associativity1076.4.4Latency After a Miss1086.4.5Write Policy1096.4.6Implementation109Main Memory104                                                                                                                                                                                                                                                                                                                                                                                                                                    |

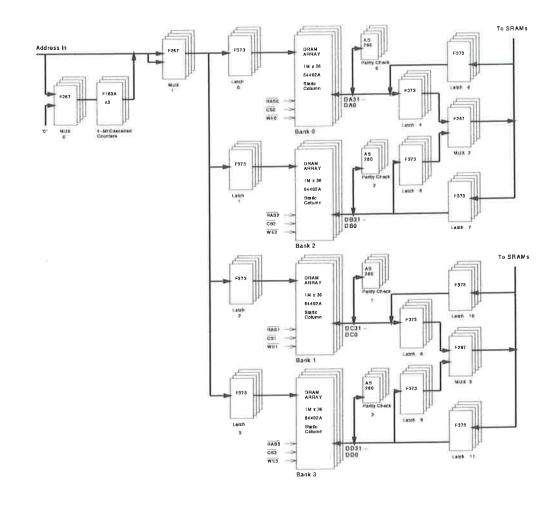

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | Implementation101After Calculating the Offset101Conclusion105 <b>nory Interface</b> 103Introduction105Applying and Extracting the Outer Product1056.2.1 Extracting the Outer Product105Memory Overview1046.3.1 Difference From Vector Memory Systems1066.4.1 Cache Size1066.4.2 Block Size1066.4.3 Associativity1076.4.4 Latency After a Miss1066.4.5 Write Policy1066.4.6 Implementation106Main Memory1116.5.1 Implementation111                                                                                                                                                                                                                                                                                                                                                                 |

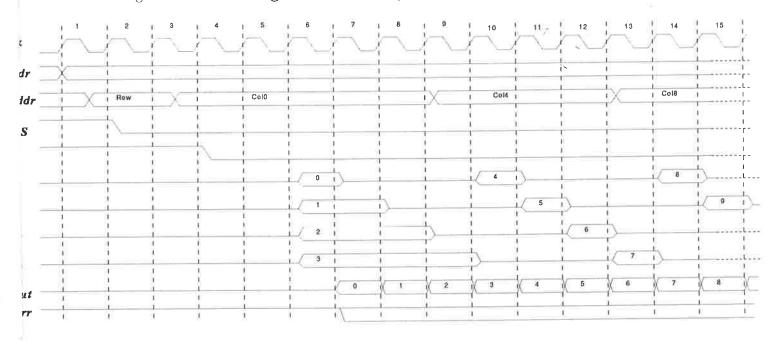

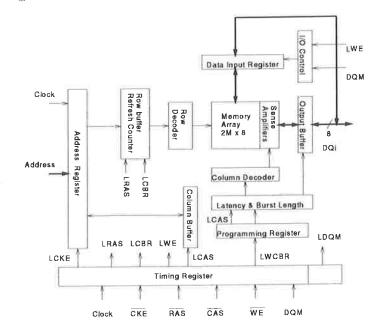

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | Implementation101After Calculating the Offset102Conclusion105Introduction105Applying and Extracting the Outer Product1056.2.1 Extracting the Outer Product105Memory Overview1046.3.1 Difference From Vector Memory Systems1066.4.1 Cache Size1066.4.2 Block Size1066.4.3 Associativity1076.4.4 Latency After a Miss1066.4.5 Write Policy1066.4.6 Implementation107Main Memory1116.5.1 Implementation1126.5.2 Synchronous DRAMs114                                                                                                                                                                                                                                                                                                                                                                 |

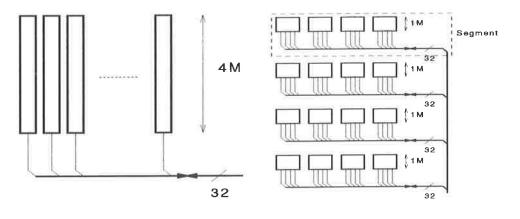

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | After Calculating the Offset       101         Conclusion       102 <b>nory Interface</b> 103         Introduction       103         Applying and Extracting the Outer Product       103         6.2.1 Extracting the Outer Product       103         Memory Overview       104         6.3.1 Difference From Vector Memory Systems       104         Cache       106         6.4.1 Cache Size       106         6.4.2 Block Size       106         6.4.3 Associativity       107         6.4.4 Latency After a Miss       106         6.4.5 Write Policy       106         6.4.6 Implementation       107         6.5.1 Implementation       107         6.5.2 Synchronous DRAMs       114         6.5.3 Bank Size       114                                                                     |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | After Calculating the Offset101Conclusion102nory Interface103Introduction104Applying and Extracting the Outer Product1066.2.1 Extracting the Outer Product106Memory Overview1046.3.1 Difference From Vector Memory Systems104Cache1066.4.1 Cache Size1066.4.2 Block Size1066.4.3 Associativity1076.4.4 Latency After a Miss1066.4.5 Write Policy1066.4.6 Implementation1066.5.1 Implementation1116.5.2 Synchronous DRAMs114Bus Exchangers114                                                                                                                                                                                                                                                                                                                                                      |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | After Calculating the Offset101Conclusion102nory Interface103Introduction104Applying and Extracting the Outer Product1006.2.1 Extracting the Outer Product100Memory Overview1046.3.1 Difference From Vector Memory Systems104Cache1066.4.1 Cache Size1066.4.2 Block Size1066.4.3 Associativity1076.4.4 Latency After a Miss1066.4.5 Write Policy1006.4.6 Implementation100Main Memory1116.5.1 Implementation1126.5.3 Bank Size1146.5.1 Control1146.5.1 Control1146.5.1 Control114                                                                                                                                                                                                                                                                                                                 |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | After Calculating the Offset       101         Conclusion       102 <b>nory Interface</b> 103         Introduction       104         Applying and Extracting the Outer Product       100         6.2.1 Extracting the Outer Product       100         Memory Overview       100         6.3.1 Difference From Vector Memory Systems       104         Cache       106         6.4.1 Cache Size       106         6.4.2 Block Size       106         6.4.3 Associativity       107         6.4.4 Latency After a Miss       106         6.4.5 Write Policy       106         6.4.6 Implementation       100         Main Memory       111         6.5.1 Implementation       112         6.5.2 Synchronous DRAMs       114         6.5.1 Control       114         6.5.2 Read/Write Path       114 |

| 6 | <ul> <li>5.3</li> <li>5.4</li> <li>Men</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul> | After Calculating the Offset101Conclusion102nory Interface103Introduction100Applying and Extracting the Outer Product1006.2.1 Extracting the Outer Product100Memory Overview1006.3.1 Difference From Vector Memory Systems100Cache1006.4.1 Cache Size1006.4.2 Block Size1006.4.3 Associativity1006.4.4 Latency After a Miss1006.4.5 Write Policy1006.4.6 Implementation100Main Memory1116.5.1 Implementation1116.5.3 Bank Size1146.5.1 Control1146.5.1 Control114                                                                                                                                                                                                                                                                                                                                 |

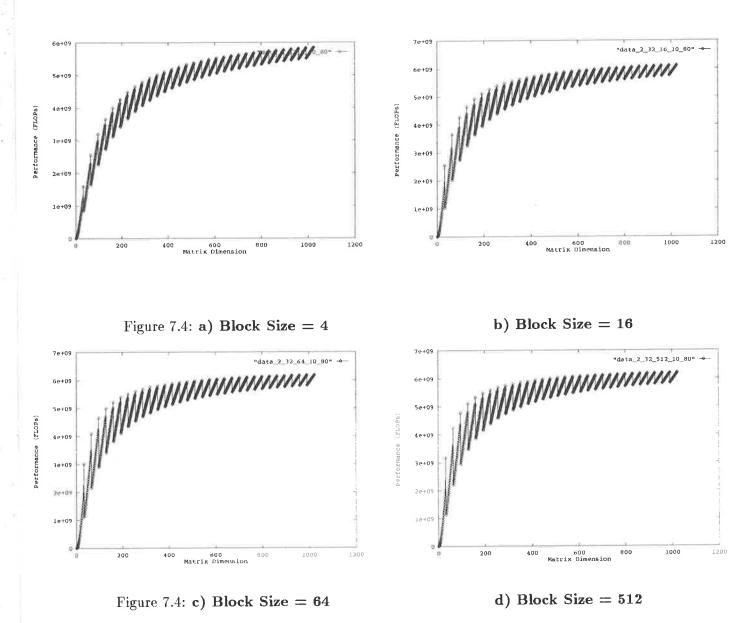

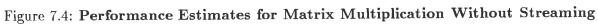

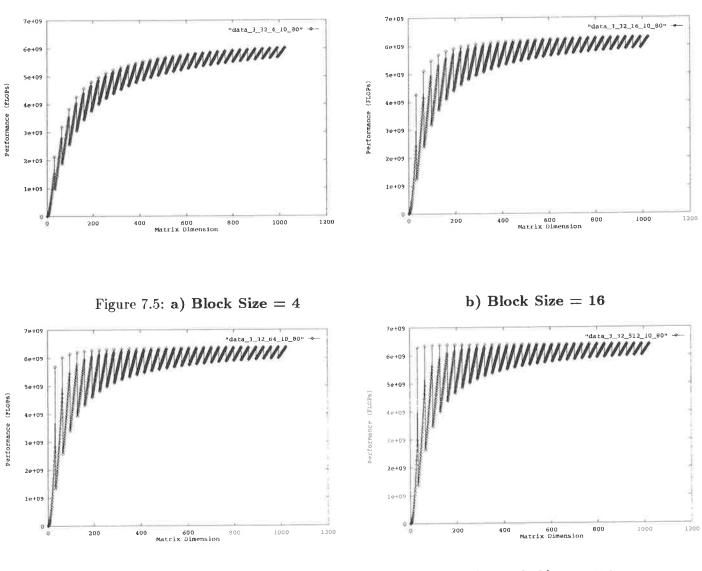

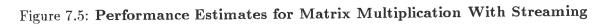

| 7 | $\mathbf{Per}$ | formance Estimates 125                                                  |

|---|----------------|-------------------------------------------------------------------------|

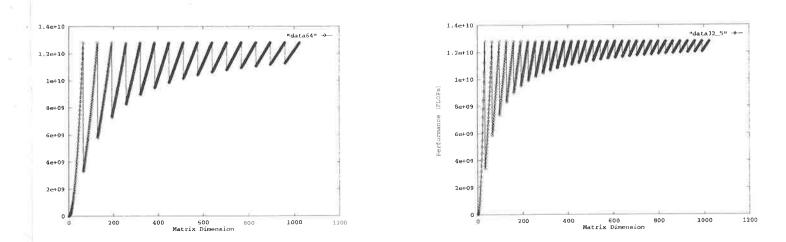

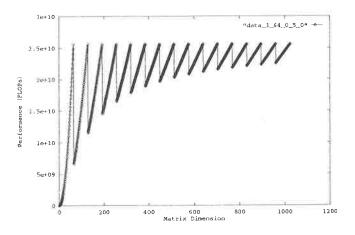

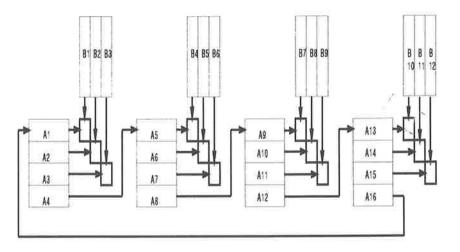

|   | 7.1            | Matrix Multiplication                                                   |

|   | 7.2            | Gauss Jordan Elimination and Inversion                                  |

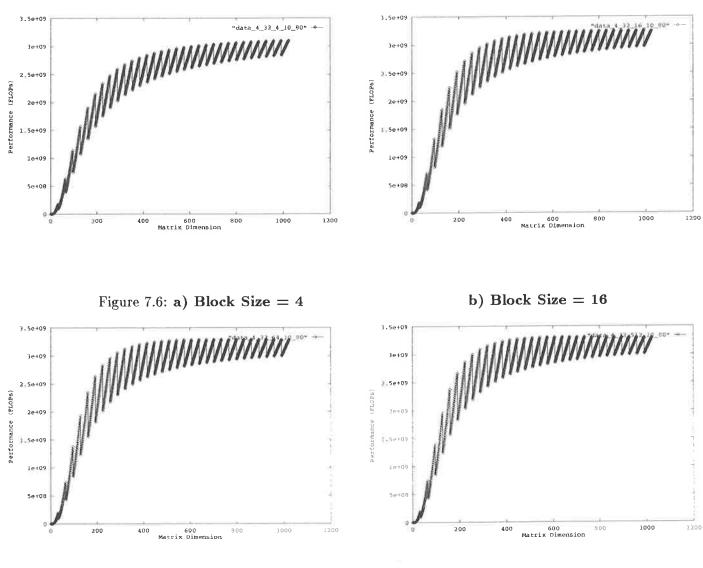

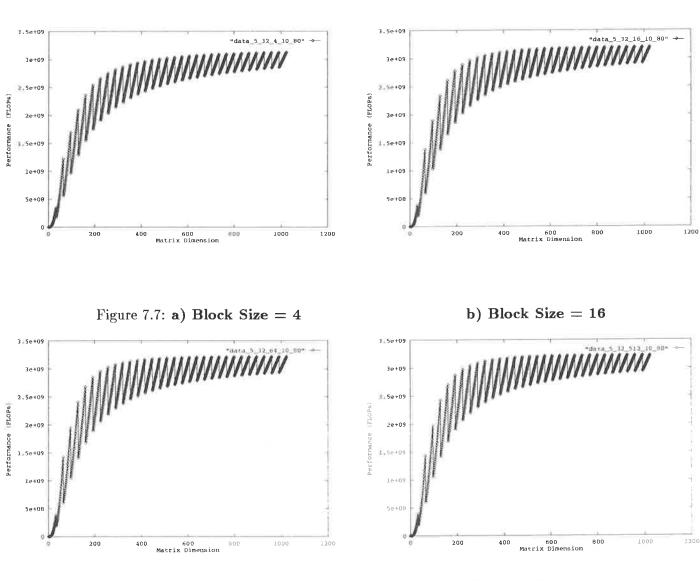

|   |                | 7.2.1 Gaussian Elimination for Matrices Smaller than the Cache Size 130 |

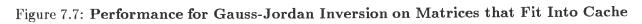

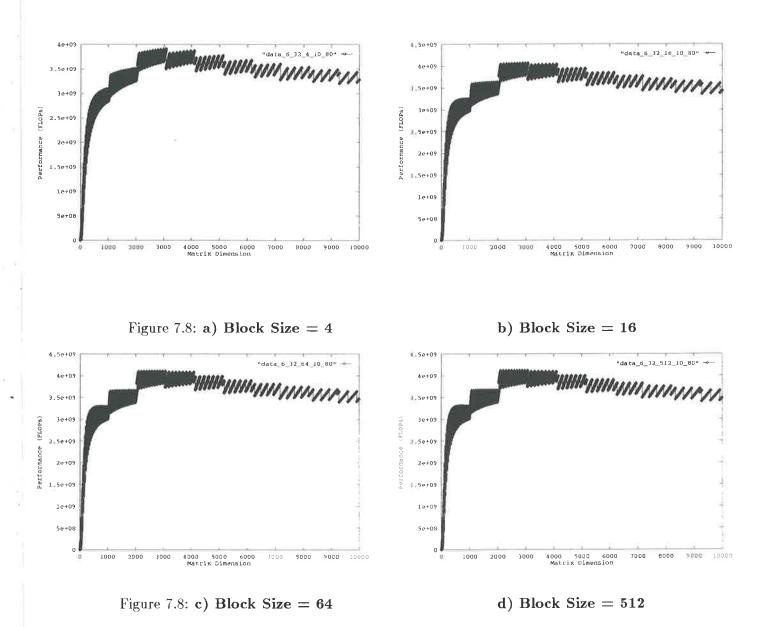

|   |                | 7.2.2 Gaussian Elimination for Matrices Larger than the Cache Size      |

|   |                | 7.2.3 Conclusion                                                        |

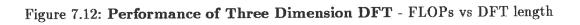

|   | 7.3            | Discrete Fourier Transform                                              |

|   |                | 7.3.1 Discrete Fourier Transform Without Multi-level Memory System      |

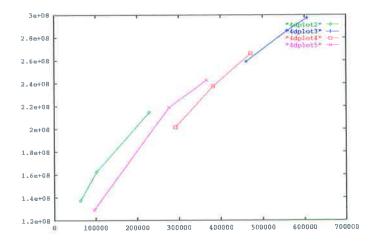

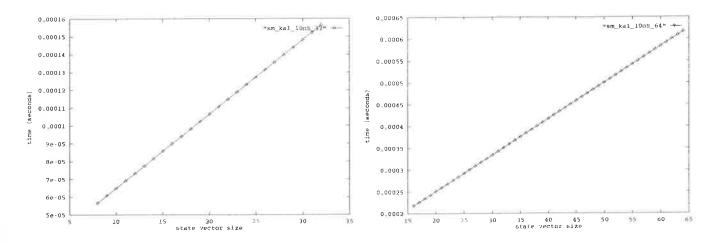

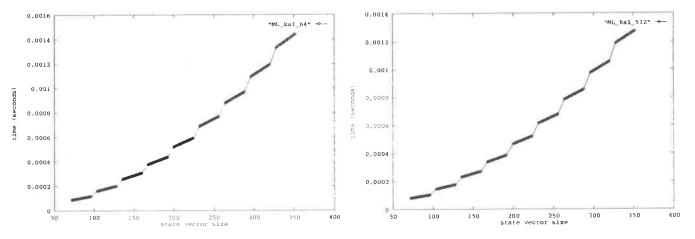

|   | 7.4            | The Kalman Filter                                                       |

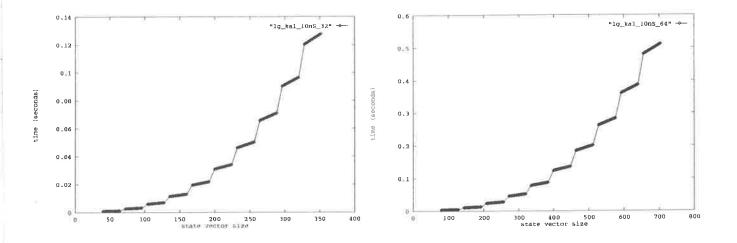

|   |                | 7.4.1 Small Problem Size Running From SRAM                              |

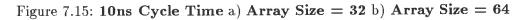

|   |                | 7.4.2 Large Problem Size Running From SRAM                              |

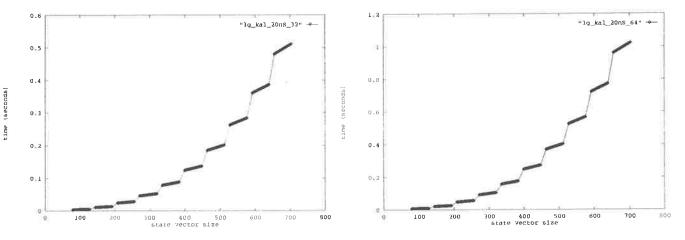

|   |                | 7.4.3 Kalman Filter With a Multi-level Memory Sub-system                |

|   | 7.5            | Conclusion                                                              |

|   |                |                                                                         |

| 8 | Fut            | sure Projects 153                                                       |

|   | 8.1            | A Multi-Processor Teraflop Engine 15:                                   |

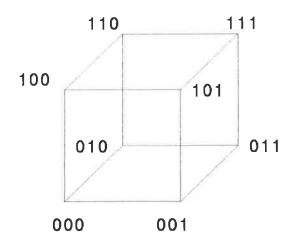

|   |                | 8.1.1 The Hypercube                                                     |

|   |                | 8.1.2 Fibre-Optical Interconnection                                     |

|   |                | 8.1.3 Utilising the Hypercube - the Proposed Model                      |

|   |                | 8.1.4 Algorithms                                                        |

|   | 8.2            | Wavelet Processor                                                       |

|   |                | 8.2.1 Still Picture Compression                                         |

|   |                | 8.2.2 Moving Picture Compression                                        |

|   | 8.3            | Conclusion                                                              |

| 9 | Sur            | mmary and Conclusion 171                                                |

Appendices

| A  | SCAP Data Sheets                                                                                    | 173               |

|----|-----------------------------------------------------------------------------------------------------|-------------------|

| в  | Proof of Convergence for Iterative Matrix Inversion<br>B.1 Initialising the Pivot Inverse Iteration | <b>179</b><br>179 |

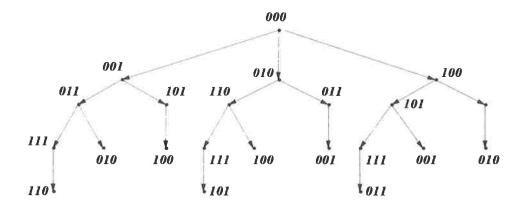

| С  | Broadcasting Data on a Hypercube                                                                    | 182               |

|    | C.1 Simple Broadcast                                                                                | 182               |

|    | C.2 Pipelined Broadcast                                                                             |                   |

|    | C.3 Parallel or Rotated Broadcast                                                                   | 184               |

|    | C.4 Pipelined and Rotated Broadcast                                                                 |                   |

| Bi | ibliography                                                                                         | 187               |

# List of Figures

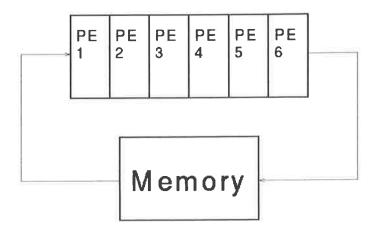

| 1.1  | Basic Systolic Array                                                                                                                      |    |                         |      |      |       |          |        | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------|------|------|-------|----------|--------|----|

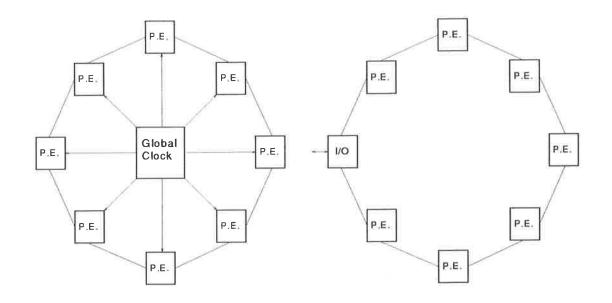

| 1.2  | Timing Ring Diagram for a) Systolic Array b) Wavefront Array                                                                              | ŧŝ | $\sim s$                | 8.8  |      |       | $\sim 1$ | s se   | 3  |

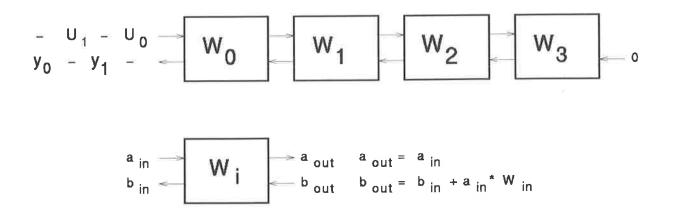

| 1.3  | Linear Systolic Array for Convolution                                                                                                     | ÷  | а.                      | . e  | s s  |       | æ. 9     |        | 4  |

| 1.4  | Array for the Direct Solution of a Set of Linear Equations                                                                                | æ  | $\tilde{c} \rightarrow$ | . x: | x x  |       |          | •      | 4  |

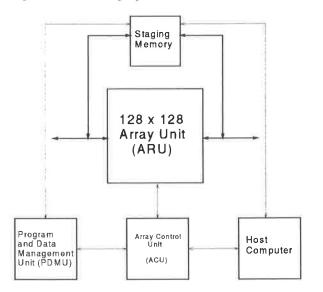

| 1.5  | MPP Architecture                                                                                                                          | 8  | 2.2                     | 8.8  | a a  | - 20  | × 3      | ē (10) | 5  |

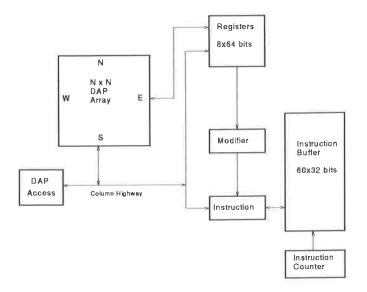

| 1.6  | DAP Architecture                                                                                                                          | ų) | $\psi = \psi$           | 14   | æ. 4 | 1     | а÷ р     | 2.12   | 6  |

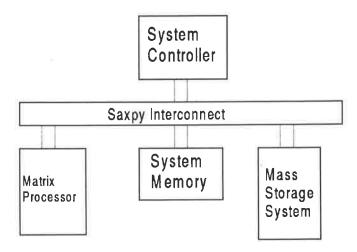

| 1.7  | Saxpy-1 Block Structure                                                                                                                   | ÷. | 8.8                     | 8    | 2.2  | 2     | a 1      | 2.2    | 7  |

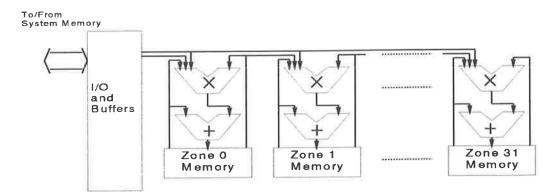

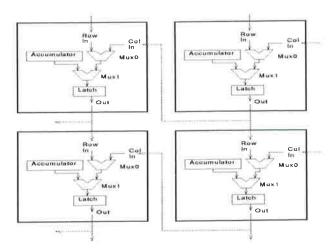

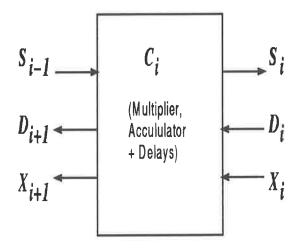

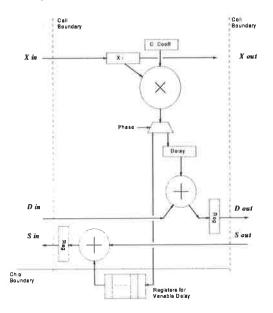

| 1.8  | Processing Element Structure                                                                                                              |    |                         |      |      |       |          |        | 8  |

| 1.9  | Warp Architecture                                                                                                                         |    |                         |      |      |       |          |        | 9  |

|      |                                                                                                                                           |    |                         |      |      |       |          |        |    |

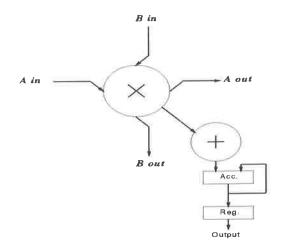

| 2.1  | Processing Element Structure                                                                                                              |    |                         |      |      |       |          |        | 11 |

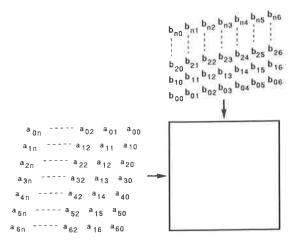

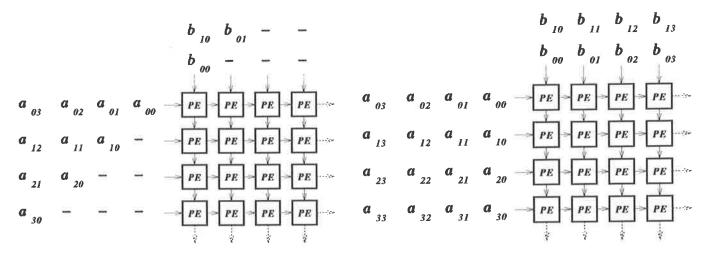

| 2.2  | Nibble (Digit) Skewing Input Data                                                                                                         | ÷  | 8.9                     | 8    |      | Ť     | 89       | 19     | 12 |

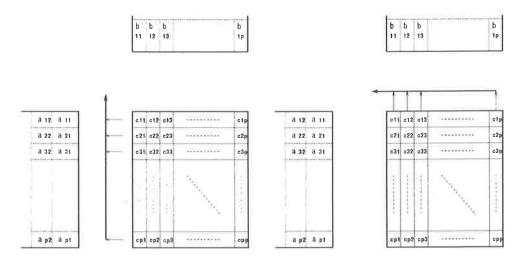

| 2.3  | a) Inner Product b) Outer Product                                                                                                         |    | $a \cdot c$             | 2    |      | •     | æ i      | 8      | 12 |

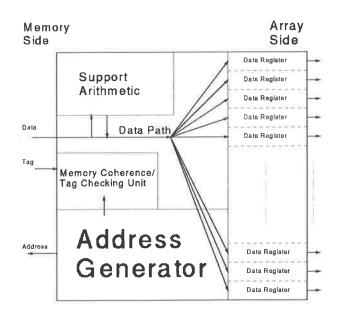

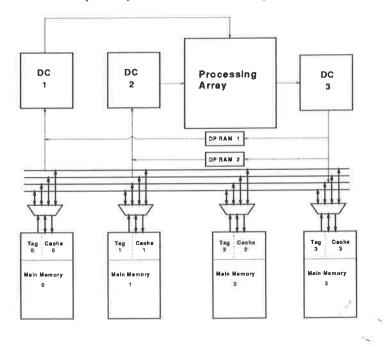

| 2.4  | Block Diagram of Data Controller                                                                                                          |    |                         |      |      |       |          |        |    |

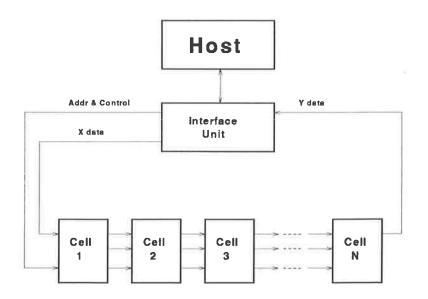

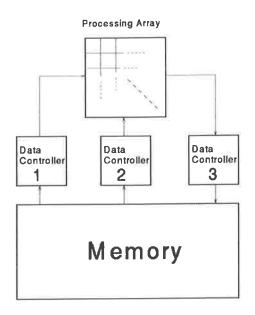

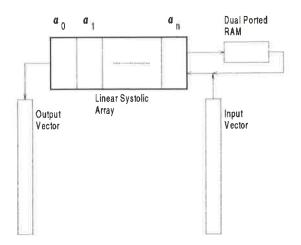

| 2.5  | Block Diagram of System                                                                                                                   |    |                         |      |      |       |          |        |    |

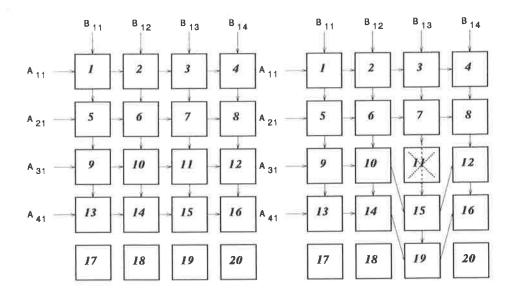

| 2.6  | Redundant Array a) Before Failure b) After Failure                                                                                        | æ  | × ×                     |      |      |       | 18-1     | e 18   |    |

| 2.7  | Redundancy Using Data Controller                                                                                                          | ÷  | æ. 9                    | 6 10 |      | (4)   | 18-1     | 8.18   | 16 |

|      |                                                                                                                                           |    |                         |      |      |       |          |        |    |

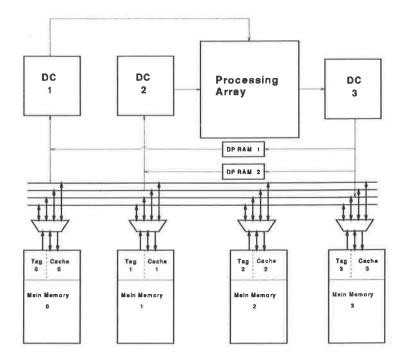

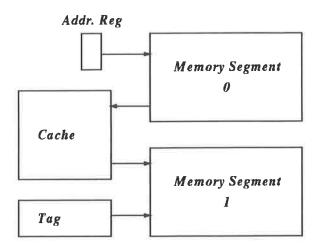

| 3.1  | Block Diagram of System                                                                                                                   |    | * 9                     | : :: | 8 B  | 5     | 98 - 9   | 5 35   | 21 |

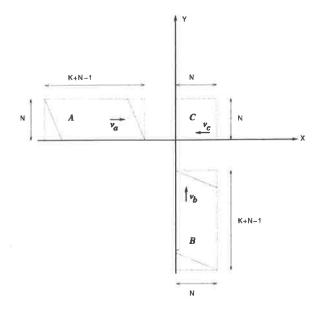

| 3.2  | Four Regions of a Partitioned Matrix Product                                                                                              |    |                         |      | 8.3  | 8-195 | * 2      | • *    | 23 |

| 3.3  | Memory Access for Matrix Product                                                                                                          |    |                         |      |      |       |          |        |    |

| 3.4  | Row Oriented Gauss-Jordan Elimination                                                                                                     |    |                         |      |      |       |          |        |    |

| 3.5  | Extracting a) Standard b) Transpose                                                                                                       | Ŷ  | \$ 3                    | i ii | ¥ 3  | 1 72  | 3 5      | : :    | 26 |

| 3.6  | Column Oriented Gauss-Jordan Elimination                                                                                                  |    |                         |      |      |       |          |        |    |

| 3.7  | Dividing Sets of Equations Into Blocks                                                                                                    |    |                         |      |      |       |          |        |    |

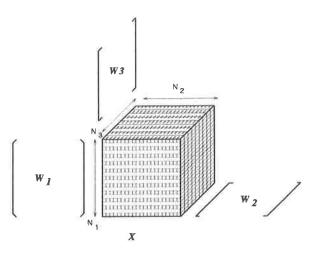

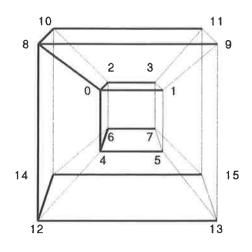

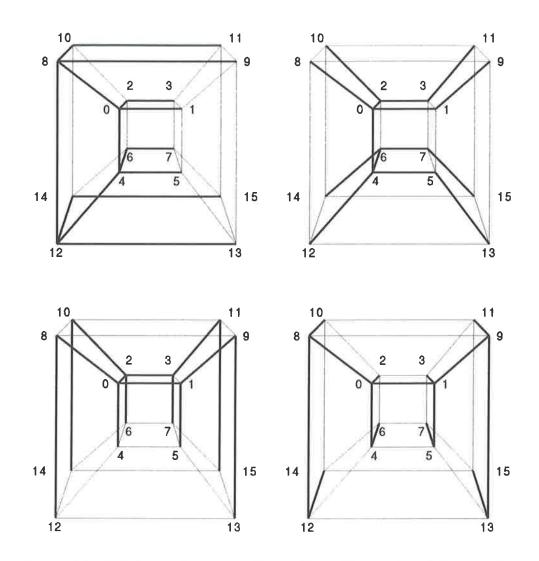

| 3.8  | 3 Dimensional Representation of Prime Factor DFT                                                                                          |    | :: ;                    | t st | s s  | 1     | a 1      | e - 2  | 34 |

|      |                                                                                                                                           |    |                         |      |      |       |          |        | 90 |

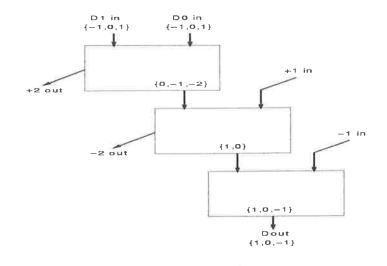

| 4.1  | Sign-Digit Addition Cell.                                                                                                                 |    |                         |      |      |       |          |        |    |

| 4.2  | Sign-Digit Propagation Path.                                                                                                              |    |                         |      |      |       |          |        |    |

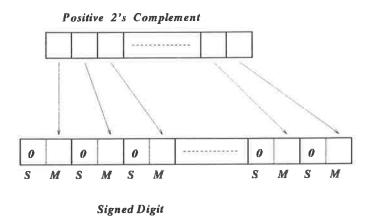

| 4.3  | Converting Positive 2's Complement to Signed Digit.                                                                                       |    |                         |      |      |       |          |        |    |

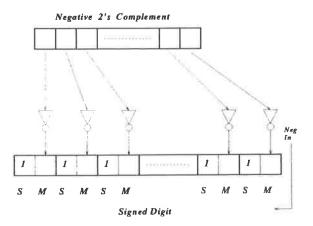

| 4.4  | Converting Negative 2's Complement to Signed Digit.                                                                                       |    |                         |      |      |       |          |        |    |

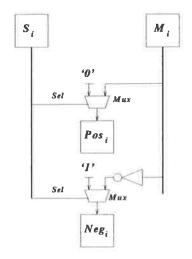

| 4.5  | Converting Signed Digit to 2's Complement.                                                                                                |    |                         |      |      |       |          |        |    |

| 4.6  | a) b)                                                                                                                                     |    |                         |      |      |       |          |        |    |

| 4.6  | c) d)                                                                                                                                     |    |                         |      |      |       |          |        |    |

| 4.6  | Karnaugh Maps for First Digit Cell of an Adder                                                                                            |    | . 3                     | 12   | a a  | 1 24  | 94-9     | ្នះ    | 46 |

| 4.7  | a) b)                                                                                                                                     |    |                         |      |      |       |          |        |    |

| 4.7  | c)                                                                                                                                        |    |                         |      |      |       |          |        |    |

| 4.7  | d) $\ldots \ldots \ldots$ |    |                         |      |      |       |          |        |    |

| 4.7  | Karnaugh Maps for First Digit Cell of an Adder                                                                                            |    |                         |      |      |       |          |        | 47 |

| 4.8  | a) b)                                                                                                                                     |    |                         |      |      |       |          |        |    |

| 4.8  | d)                                                                                                                                        |    |                         |      |      |       |          |        |    |

| 4.8  | Karnaugh Maps for Last Digit Cell of an Adder with Single In                                                                              |    |                         |      |      |       |          |        |    |

| 4.9  | Unlatched Signed-Digit Adder Cell                                                                                                         |    |                         |      |      |       |          |        |    |

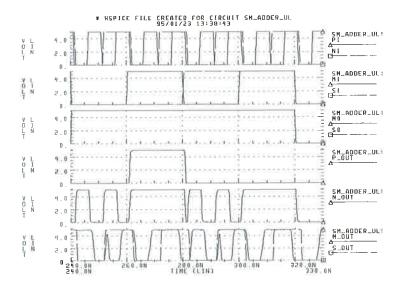

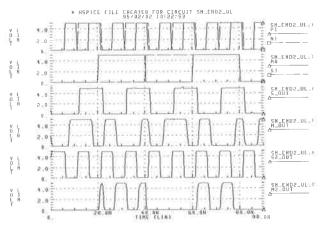

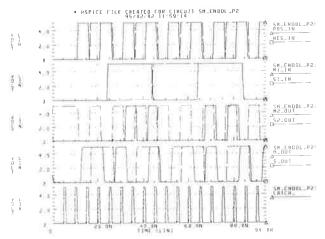

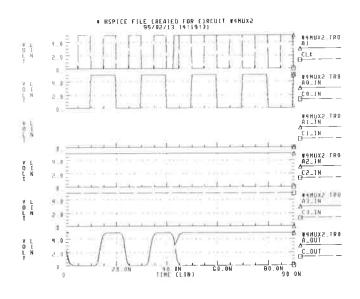

| 4.10 | HSpice Plots for Unlatched Adder Cell                                                                                                     |    |                         |      |      |       |          |        | 49 |

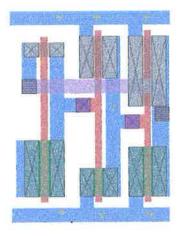

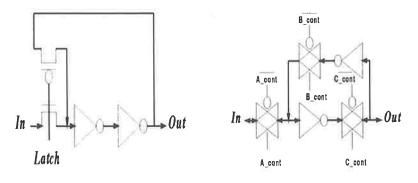

|      | Layout of Latch Cell                                                                                                                      |    |                         |      |      |       |          |        |    |

| 4.40 |                                                                                                                                             | 50       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.12 | Latched Signed-Digit Adder Cell                                                                                                             | 50       |

| 4.13 | HSpice Simulation for Latched Adder Cell                                                                                                    | 51       |

| 4.14 | Latched Adder Cell With Multiplexer                                                                                                         | 51       |

| 4.15 | Layout of Unlatched Beginning Cell                                                                                                          | 52       |

|      | HSpice Simulation Results for Unlatched Beginning Cell                                                                                      | 52       |

|      | Layout of Latched Beginning Cell                                                                                                            | 53       |

|      | Layout of Latch & Multiplexed Input Beginning Cell                                                                                          | 53       |

|      |                                                                                                                                             | 54       |

|      | a) Unlatched End Cell With Standard Propagated Outputs                                                                                      |          |

| 4.19 | b) Unlatched End Cell With Sign Magnitude Progopated Outputs                                                                                | 54       |

| 4.20 | a) Unlatched End Cell With Standard Propagated Outputs Simulation Results                                                                   | 55       |

| 4.20 | b) Unlatched End Cell With Sign Magnitude Progopated Outputs Simulation                                                                     |          |

|      | Results                                                                                                                                     | 55       |

| 4.21 | a) Latched End Cell With Standard Propagated Outputs                                                                                        | 56       |

|      | b) Latched End Cell With Sign Magnitude Progopated Outputs                                                                                  | 56       |

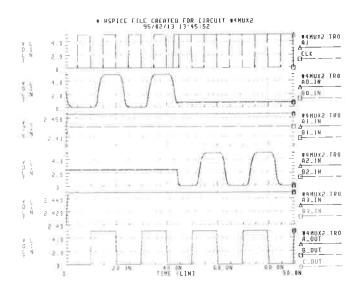

| 1.21 | a) Latched End Cell With Standard Propagated Outputs Simulation Results                                                                     | 57       |

| 4.22 | b) Latched End Cell With Sign Magnitude Progopated Outputs Simulation                                                                       | 01       |

| 4.22 |                                                                                                                                             | 57       |

|      | Results                                                                                                                                     |          |

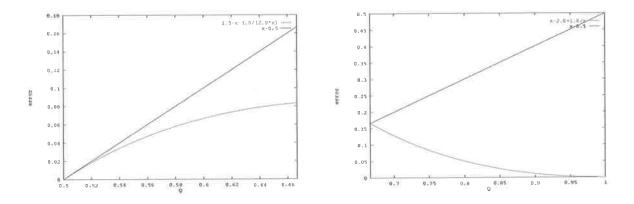

| 4.23 | <b>Error graphs for a)</b> $0.5 < Q \le \frac{2}{3}$ <b>b)</b> $\frac{2}{3} < Q \le 1$                                                      | 60       |

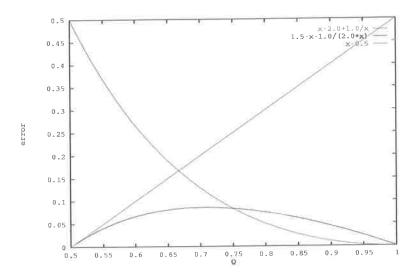

| 4.24 | Error graph over full range of $\mathbf{Q}$                                                                                                 | 61       |

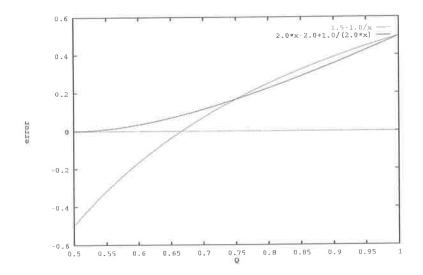

| 4.25 | Difference in Errors for Two Schemes                                                                                                        | 61       |

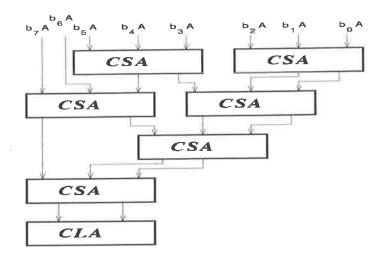

| 4.26 | Wallace-tree Multiplier.                                                                                                                    | 67       |

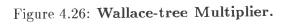

|      | Signed Digit Multiplier.                                                                                                                    | 67       |

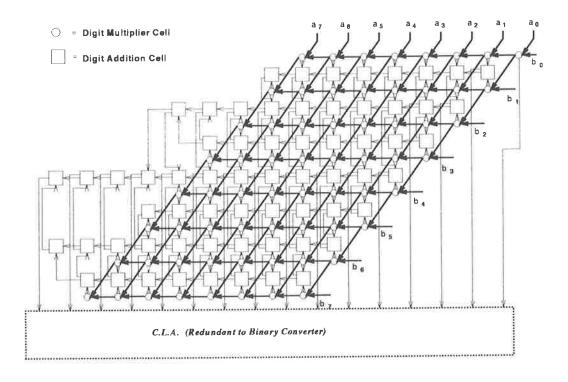

|      | VLSI Layout of Digit Multiply Cell                                                                                                          | 69       |

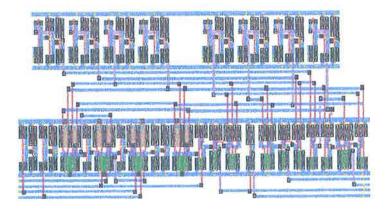

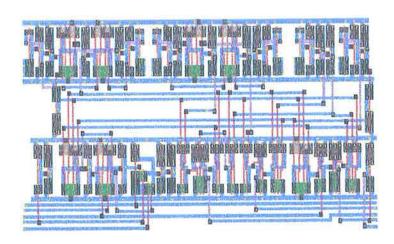

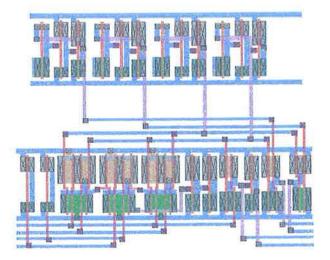

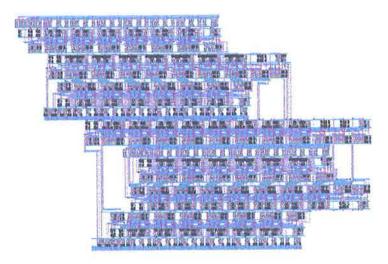

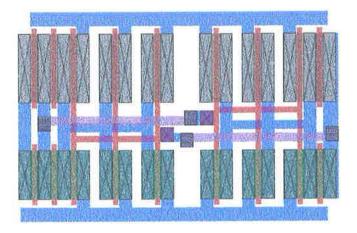

|      | VLSI Layout of 8 × 8 Non-pipelined Multiplier                                                                                               | 69       |

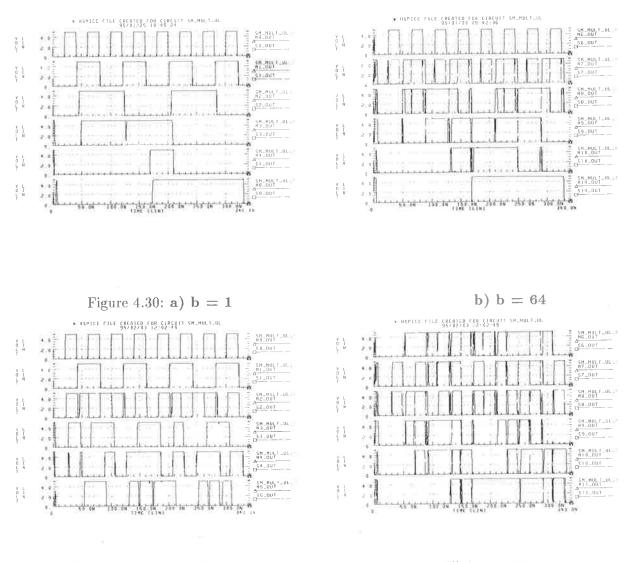

|      |                                                                                                                                             | 70       |

|      |                                                                                                                                             |          |

|      | ci) $b = 141$ cii) $b = 141$                                                                                                                | 70       |

|      | ciii) $b = 141$ d) $b = 255 \dots \dots$    | 71       |

| 4.30 | dii) $b = 255$ diii) $b = 255$                                                                                                              | 71       |

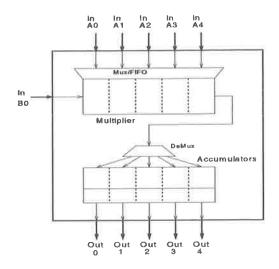

| 4.31 | Processing Cell Using Pipelined Multiplier                                                                                                  | 74       |

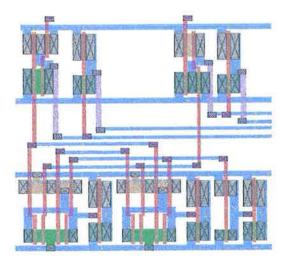

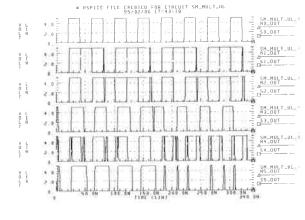

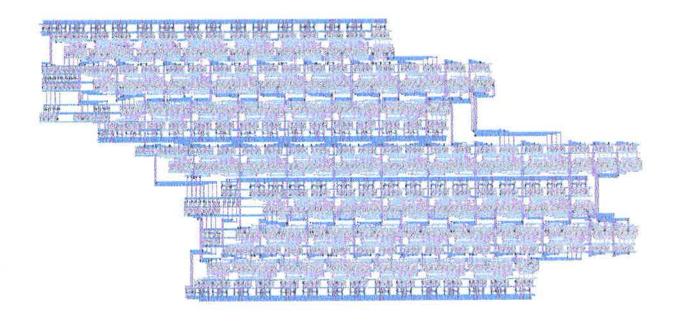

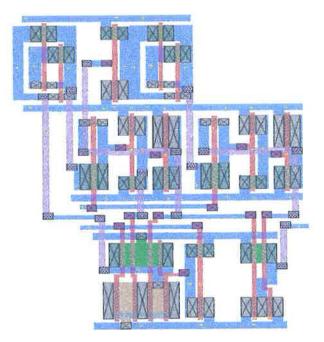

| 4.32 | VLSI Layout of Pipelined 8 × 8 Multiplier                                                                                                   | 75       |

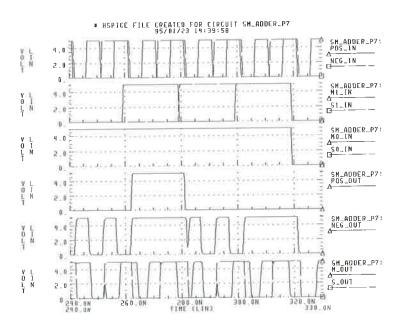

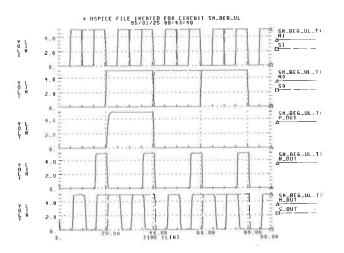

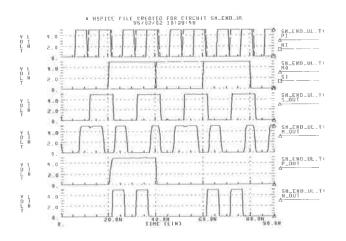

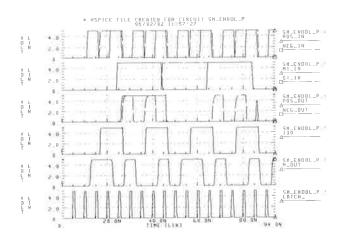

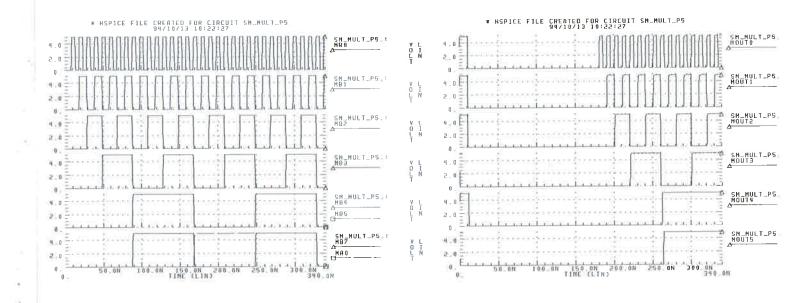

| 4.33 | HSpice Simulation Plots a) Input b) Output                                                                                                  | 75       |

|      | · / · / ·                                                                                                                                   |          |

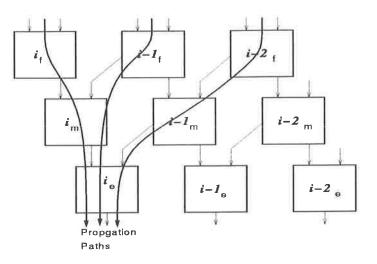

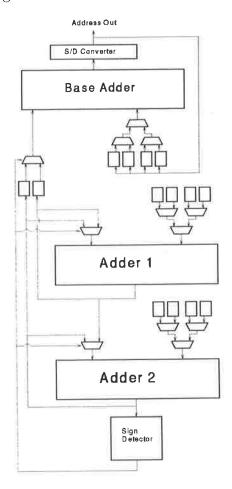

| 5.1  | Lattice Representation of a Matrix Product                                                                                                  | 79       |

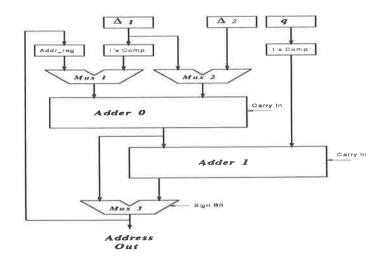

| 5.2  | 2D Addr Gen.                                                                                                                                | 79       |

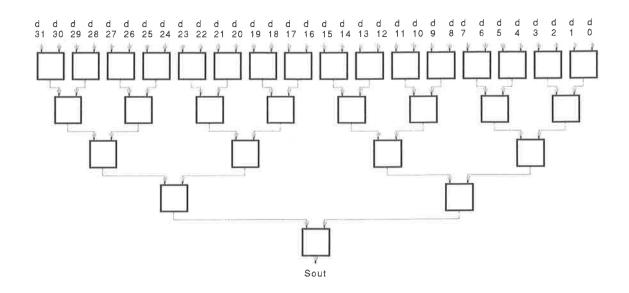

| 5.3  | 4D Addr Gen.                                                                                                                                | 81       |

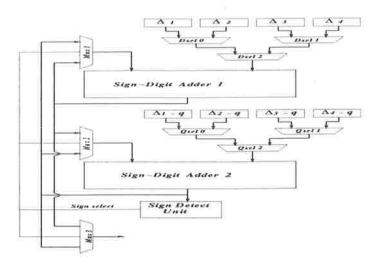

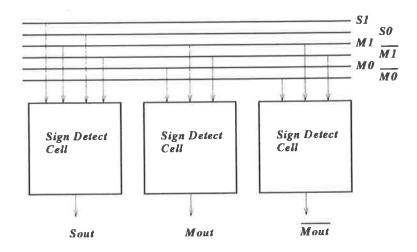

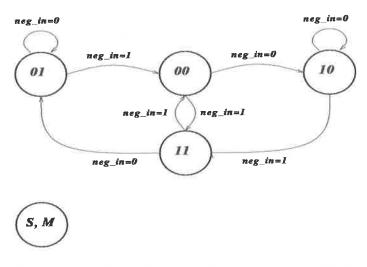

| 5.4  | Sign Detect Unit Cell                                                                                                                       | 82       |

| 5.5  | Sign Detect Unit                                                                                                                            | 84       |

| 5.6  | Domino Logic Exclusive-OR Gate                                                                                                              | 85       |

|      |                                                                                                                                             | 87       |

| 5.7  | Flow Diagram for Decrement Cell                                                                                                             |          |

| 5.8  | Decrement Cell                                                                                                                              | 87       |

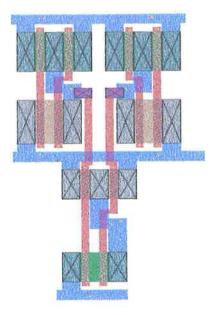

| 5.9  | Full Decrement Cell                                                                                                                         | 88       |

| 5.10 | Four Input Zero Detection Cell                                                                                                              | 89       |

| 5.11 | Four-Bit Decrement Unit                                                                                                                     | 90       |

| 5.12 | Simulation Results of Four Bit Decrement Cell                                                                                               | 90       |

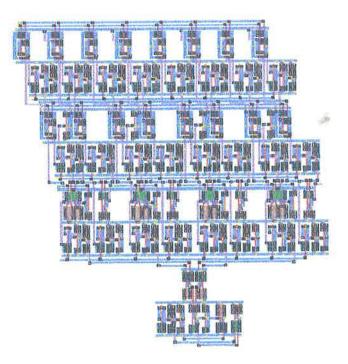

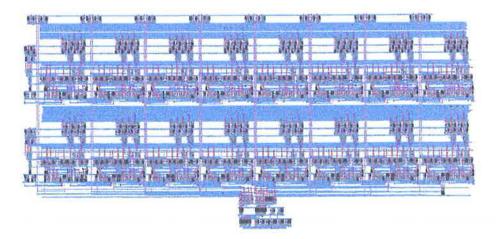

| 5.13 | Sixteen-Bit Decrement Unit                                                                                                                  | 91       |

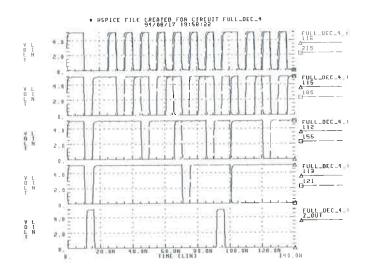

|      | HSpice Simulation Results for Sixteen Bit Decrementer                                                                                       | 92       |

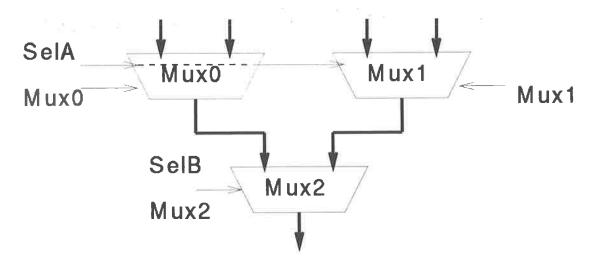

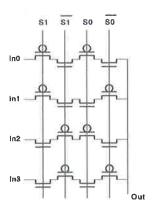

|      | Delta Register Multiplexers                                                                                                                 | 92       |

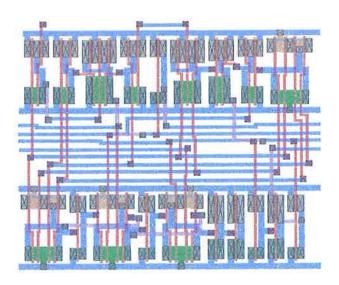

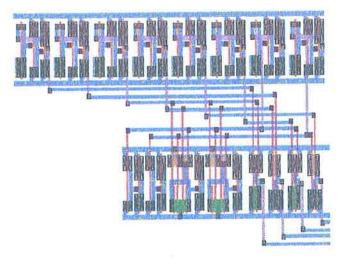

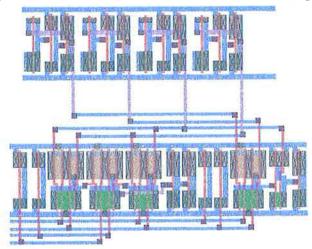

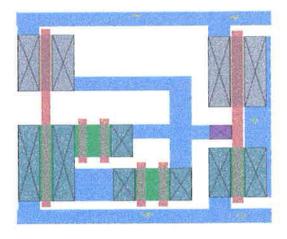

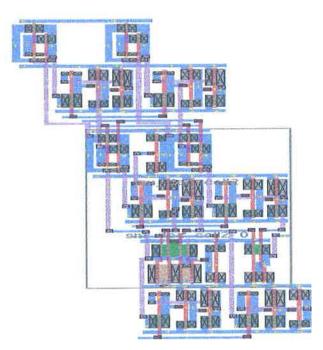

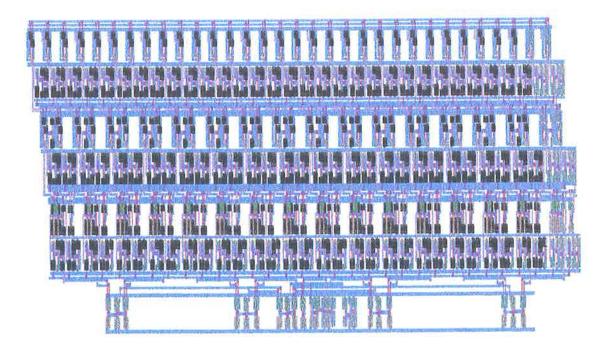

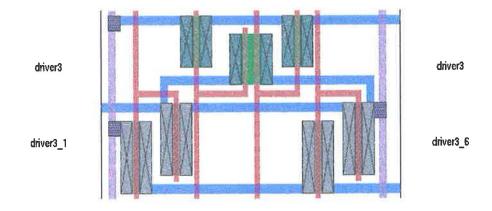

|      | VLSI Layout of an Eight-bit Address Generator                                                                                               | 93       |

|      |                                                                                                                                             | 95<br>95 |

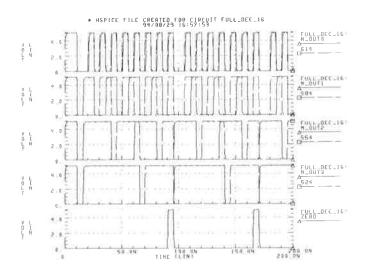

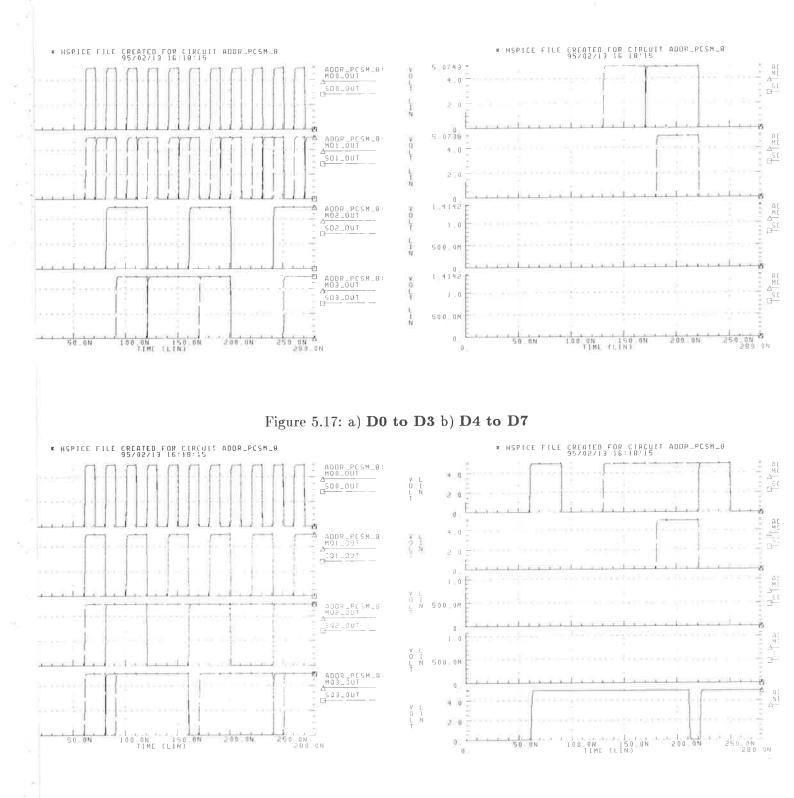

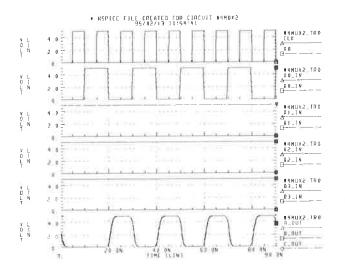

|      | a) D0 to D3 b) D4 to D7 $\dots \dots \dots$ |          |

|      | c) Q0 to Q3 d) Q4 to Q7 & Neg $\ldots$                                                                                                      | 95       |

|      | Simulation of Normal Address Generation                                                                                                     | 95       |

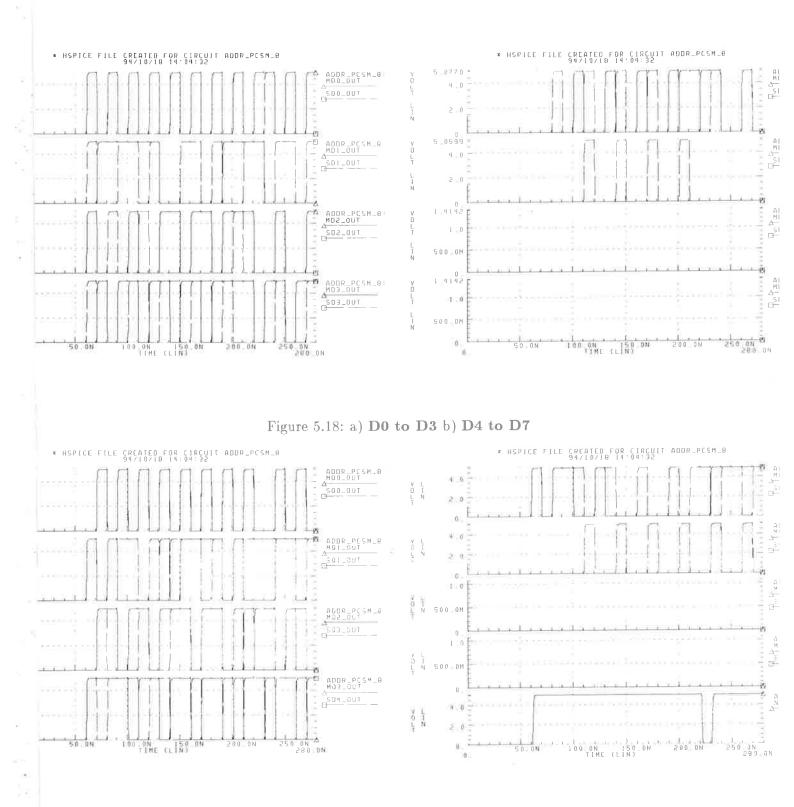

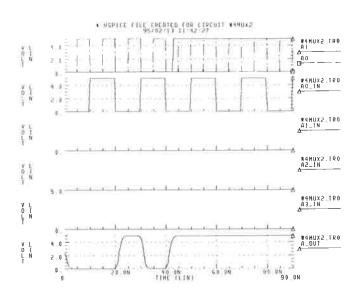

|      | a) D0 to D3 b) D4 to D7 $\dots \dots \dots$ | 97       |

| 5.18 | c) Q0 to Q3 d) Q4 to Q7 and Neg Out                                                                                                         | 97       |

|      | Simulation of Transposed Address Generation                                                                                                 | 97       |

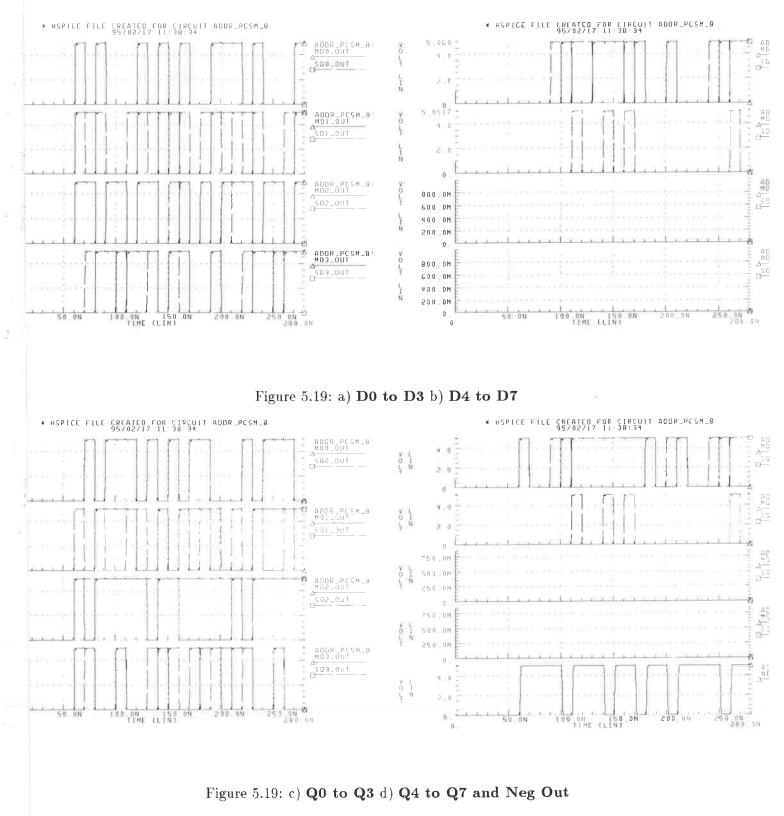

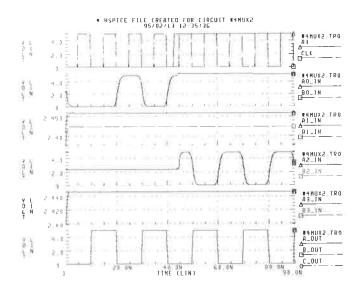

|      | a) D0 to D3 b) D4 to D7                                                                                                                     | 99       |

|      |                                                                                                                                             |          |

| 5.19 Simulation of Prime Factored Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Out         99           ress Generation         99           101         101                                                                                                                                                                                                                                                                                                                                                                                                     |