## Type of Instruction

Flaxer Eli - Computer Architecture

Ch 2 - 3

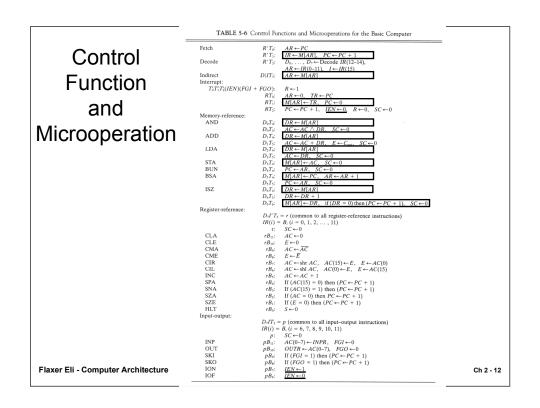

### Register - Reference Instruction

TABLE 5-3 Execution of Register-Reference Instructions

$D_7 I' T_3 = r$  (common to all register-reference instructions)  $IR(i) = B_i$  [bit in IR(0-11) that specifies the operation]

|            | r:          | $SC \leftarrow 0$                                                              | Clear SC         |

|------------|-------------|--------------------------------------------------------------------------------|------------------|

| CLA        | $rB_{11}$ : | $AC \leftarrow 0$                                                              | Clear AC         |

| CLE        | $rB_{10}$ : | $E \leftarrow 0$                                                               | Clear E          |

| <b>CMA</b> | $rB_9$ :    | $AC \leftarrow \overline{AC}$                                                  | Complement AC    |

| <b>CME</b> | $rB_8$ :    | $E \leftarrow \overline{E}$                                                    | Complement E     |

| CIR        | $rB_7$ :    | $AC \leftarrow \operatorname{shr} AC, AC(15) \leftarrow E, E \leftarrow AC(0)$ | Circulate right  |

| CIL        | $rB_6$ :    | $AC \leftarrow \text{shl } AC, AC(0) \leftarrow E, E \leftarrow AC(15)$        | Circulate left   |

| <b>INC</b> | $rB_5$ :    | $AC \leftarrow AC + 1$                                                         | Increment AC     |

| SPA        | $rB_4$ :    | If $(AC(15) = 0)$ then $(PC \leftarrow PC + 1)$                                | Skip if positive |

| <b>SNA</b> | $rB_3$ :    | If $(AC(15) = 1)$ then $(PC \leftarrow PC + 1)$                                | Skip if negative |

| <b>SZA</b> | $rB_2$ :    | If $(AC = 0)$ then $PC \leftarrow PC + 1)$                                     | Skip if AC zero  |

| <b>SZE</b> | $rB_1$ :    | If $(E = 0)$ then $(PC \leftarrow PC + 1)$                                     | Skip if E zero   |

| HLT        | $rB_0$ :    | $S \leftarrow 0$ (S is a start-stop flip-flop)                                 | Halt computer    |

Flaxer Eli - Computer Architecture

Ch 2 - 4

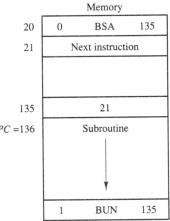

# Memory - Reference Instruction

TABLE 5-4 Memory-Reference Instructions

| Symbol | Operation decoder | Symbolic description                                    |

|--------|-------------------|---------------------------------------------------------|

| AND    | $D_0$             | $AC \leftarrow AC \land M[AR]$                          |

| ADD    | $D_1$             | $AC \leftarrow AC + M[AR], E \leftarrow C_{\text{out}}$ |

| LDA    | $D_2$             | $AC \leftarrow M[AR]$                                   |

| STA    | $D_3$             | $M[AR] \leftarrow AC$                                   |

| BUN    | $D_4$             | $PC \leftarrow AR$                                      |

| BSA    | $D_5$             | $M[AR] \leftarrow PC, PC \leftarrow AR + 1$             |

| ISZ    | $D_6$             | $M[AR] \leftarrow M[AR] + 1,$                           |

|        |                   | If $M[AR] + 1 = 0$ then $PC \leftarrow PC + 1$          |

Flaxer Eli - Computer Architecture

Ch 2 - 5

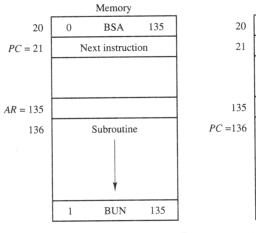

## **BSA Example**

Figure 5-10 Example of BSA instruction execution.

(a) Memory, PC, and AR at time  $T_4$

(b) Memory and PC after execution

Flaxer Eli - Computer Architecture

Ch 2 - 6

#### Input - Output Instruction

There has 6 I/O reference instruction.

TABLE 5-5 Input-Output Instructions

$D_7IT_3 = p$  (common to all input-output instructions)  $IR(i) = B_i$  [bit in IR(6-11) that specifies the instruction]

```

Clear SC

p:

SC \leftarrow 0

AC(0-7) \leftarrow INPR, FGI \leftarrow 0

Input character

INP

pB_{11}:

OUTR \leftarrow AC(0-7), FGO \leftarrow 0

Output character

OUT

pB_{10}:

If (FGI = 1) then (PC \leftarrow PC + 1)

Skip on input flag

pB_9:

SKI

Skip on output flag

If (FGO = 1) then (PC \leftarrow PC + 1)

SKO

pB_8:

ION

pB_7:

IEN \leftarrow 1

Interrupt enable on

IOF

pB_6:

IEN \leftarrow 0

Interrupt enable off

```

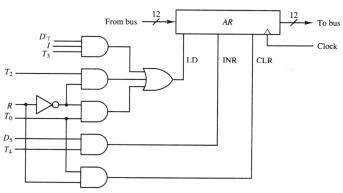

# Control of AR Register

Figure 5-16 Control gates associated with AR.

• In the similar way we can drive the control for the other register.

Flaxer Eli - Computer Architecture

Ch 2 - 13

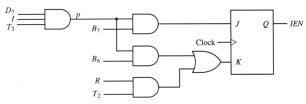

### Control of Flags

Figure 5-17 Control inputs for IEN

Flaxer Eli - Computer Architecture

Ch 2 - 14