| Mill A | REPORT                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------|

|        | DESIGN AND DEVELOPMENT<br>OF A FIXED AND A MOBILE<br>DATA COLLECTION PLATFORM                                             |

|        | CONTRACT NO: NAS5-21164                                                                                                   |

|        | prepared for<br>NATIONAL AERONAUTICS AND SPACE ADMINISTRATION<br>GODDARD SPACE FLIGHT CENTER<br>GREENBELT, MARYLAND 20771 |

|        | JUNE 1971<br>American<br>JElectronic<br>Colmar, penna.                                                                    |

N71-32895

DESIGN AND DEVELOPMENT OF A FIXED AND A MOBILE DATA COLLECTION PLATFORM  $\ \cdot$

American Electronic Laboratories Colmar, Penna.

June 1971

This document has been approved for public release and sale.

## DESIGN AND DEVELOPMENT OF A FIXED AND A MOBILE DATA COLLECTION PLATFORM

CONTRACT NO: NAS5-21164

prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION GODDARD SPACE FLIGHT CENTER GREENBELT, MARYLAND 20771

**JUNE 1971**

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1                                                                                                                                                                                                               |

|         | <pre>1.1 System Aspects 1.2 Platforms</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-1<br>1-1                                                                                                                                                                                                        |

| 2       | SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-1                                                                                                                                                                                                               |

| •       | 2.1 Mobile Platform<br>2.2 Fixed Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-1<br>2-4                                                                                                                                                                                                        |

| 3       | PLATFORM TRANSMITTER SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-1                                                                                                                                                                                                               |

|         | <pre>3.1 General Description<br/>3.1.1 Oscillator-Buffer<br/>3.1.1.1 Crystal Oscillator Loop<br/>3.1.1.2 Buffer Amplifier<br/>3.1.2 Buffer Amplifier<br/>3.1.2 Multiplier Modulator<br/>3.1.2.1 Multipliers<br/>3.1.2.2 Premodulator Linear Amplifier<br/>3.1.2.3 Phase Modulator and Driver<br/>3.1.2.4 Postmodulator Linear Amplifier<br/>3.1.2.5 C+ Control<br/>3.1.3 RF Amplifier<br/>3.1.3.1 Linear Amplifier<br/>3.1.3.2 Broadband Power Module<br/>3.1.3.3 Output Filter<br/>3.2 Detailed Description<br/>3.2.1 Circuit Operation<br/>3.2.1.1 Frequency Stability Tests<br/>3.2.1.2 Multiplier-Modulator<br/>3.2.1.3 RF Amplifier<br/>3.2.1.3 RF Amplifier<br/>3.2.2 Device Selection<br/>3.2.1.3 RF Amplifier<br/>3.2.3 Preferred Circuit Operation<br/>3.2.3 RF Amplifier<br/>3.2.3.1 Oscillator Buffer<br/>3.2.3.2 Multiplier-Modulator<br/>3.2.3.3 RF Amplifier-Fixed</pre> | 3-3<br>3-3<br>3-9<br>3-10<br>3-10<br>3-10<br>3-14<br>3-14<br>3-14<br>3-16<br>3-16<br>3-17<br>3-20<br>3-21<br>3-21<br>3-21<br>3-21<br>3-21<br>3-24<br>3-27<br>3-29<br>3-30<br>3-34<br>3-34<br>3-38<br>3-42<br>3-44 |

.

.

•

|                                              | 1-1<br>1-1<br>1-1 |

|----------------------------------------------|-------------------|

| 4.1 General Description 4                    | l-1               |

|                                              |                   |

| 4.1.1 Circuitry 4                            | 1 2               |

| 4.1.2 Timing 4                               | 1-3               |

| 4.1.2.1 Mobile Platform Timing 4             | <u>l-4</u>        |

| 4.1.2.2 Fixed Platform Timing 4              | 1-4               |

| 4.2 Detailed Description 4                   | <u>l</u> -7       |

| 4.2.1 Master Timer 4                         | <b>ŀ</b> −7       |

|                                              | l-9               |

| 4.2.3 Warmup Delay Circuitry 4               | 1-11              |

| 4.2.4 Control and Clear Gates 4              | l-13              |

| 4.2.5 Master Clock . 4                       | 4-13              |

| 4.2.6 Power Supply Circuitry 4               | 1-16              |

| 4.2.7 Input Multiplexer 4                    | 1-19              |

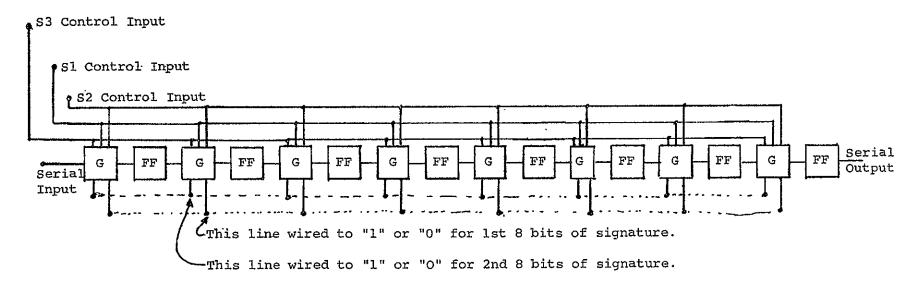

| 4.2.8 Signature Logic 4                      | 1-20              |

| 4.2.9 Format Switch 4                        | l-21              |

| 4.2.10 Convolutional Encoder 4               | 1-21              |

| 4.2.11 Output Gating Circuitry 4             | <b>I-22</b>       |

|                                              | <b>↓</b> −25      |

| 4.2.12.1 General 4                           | -25               |

|                                              | l-25              |

| 4.2.12.3 Offset Correction 4                 | -28               |

|                                              | <b>I-2</b> 8      |

|                                              | <b>↓</b> −29      |

|                                              | l-31              |

| · · · · · · · · · · · · · · · · · · ·        | -31               |

|                                              | l-33              |

|                                              | L-33              |

|                                              | -33               |

|                                              | -35               |

|                                              | -37               |

| 4.2.13.7 Load Signature (A15) and Format     |                   |

|                                              | l-37              |

|                                              |                   |

| 5 EQUIPMENT 5                                | 5-1               |

| 5.1 Manufacturing and Packaging Techniques 5 | 5-1               |

|                                              | -1                |

| 5.1.2 Transmitter Section 5                  | -4                |

|                                              | -7                |

|                                              | -14               |

|                                              | -14               |

|                                              | -17 <sup>.</sup>  |

|                                              | -17               |

|                                              | -19               |

TABLE OF CONTENTS (Cont.)

|                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COST ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                            | 6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.1 General<br>6.2 Cost Factors                                                                                                                                                                                                                                                                                                                                                                                          | 6-1 .<br>6-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ENVIRONMENTAL CONSIDERATION AND TRADEOFFS                                                                                                                                                                                                                                                                                                                                                                                | 7-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>7.1 Tradeoffs Oscillator-Buffer</li> <li>7.2 Tradeoffs Multiplier-Modulator</li> <li>7.3 Tradeoffs-RF Amplifier</li> <li>7.4 Environment Design Considerations</li> <li>7.4.1 RF Portion</li> <li>7.4.2 Logic Portion</li> <li>7.4.2.1 Symbol Rate-Master Clock</li> <li>7.4.2.2 A/D Conversion</li> <li>7.4.2.3 Offset Correction Error</li> <li>7.4.2.4 Error Summary</li> </ul>                              | 7-1<br>7-2<br>7-3<br>7-3<br>7-4<br>7-4<br>7-6<br>7-10<br>7-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RECOMMENDATIONS                                                                                                                                                                                                                                                                                                                                                                                                          | 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

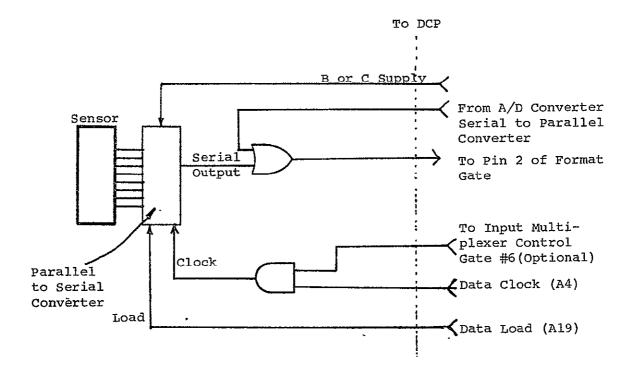

| <ul> <li>8.1 Oscillator and RF Improvements</li> <li>8.2 Logic Improvements</li> <li>8.2.1 Implementation Using Future<br/>Developments</li> <li>8.2.1.1 Digital</li> <li>8.2.1.2 Analog</li> <li>8.2.2 Circuit Improvements to Simplify<br/>or Reduce Cost</li> <li>8.2.3 Circuit Recommendations to Improve<br/>Circuit Performance</li> <li>8.2.4 Serial Digital Data</li> <li>8.3 Recommendations Summary</li> </ul> | 8-2<br>8-3<br>8-3<br>8-5<br>8-5<br>8-5<br>8-10<br>8-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>6.1 General</li> <li>6.2 Cost Factors</li> <li>ENVIRONMENTAL CONSIDERATION AND TRADEOFFS</li> <li>7.1 Tradeoffs Oscillator-Buffer</li> <li>7.2 Tradeoffs Multiplier-Modulator</li> <li>7.3 Tradeoffs-RF Amplifier</li> <li>7.4 Environment Design Considerations</li> <li>7.4.1 RF Portion</li> <li>7.4.2 Logic Portion.</li> <li>7.4.2.1 Symbol Rate-Master Clock</li> <li>7.4.2.2 A/D Conversion</li> <li>7.4.2.3 Offset Correction Error</li> <li>7.4.2.4 Error Summary</li> <li>RECOMMENDATIONS</li> <li>8.1 Oscillator and RF Improvements</li> <li>8.2.1 Implementation Using Future Developments</li> <li>8.2.1.1 Digital</li> <li>8.2.1.2 Analog</li> <li>8.2.2 Circuit Improvements to Simplify or Reduce Cost</li> <li>8.2.3 Circuit Recommendations to Improve Circuit Performance</li> <li>8.2.4 Serial Digital Data</li> </ul> |

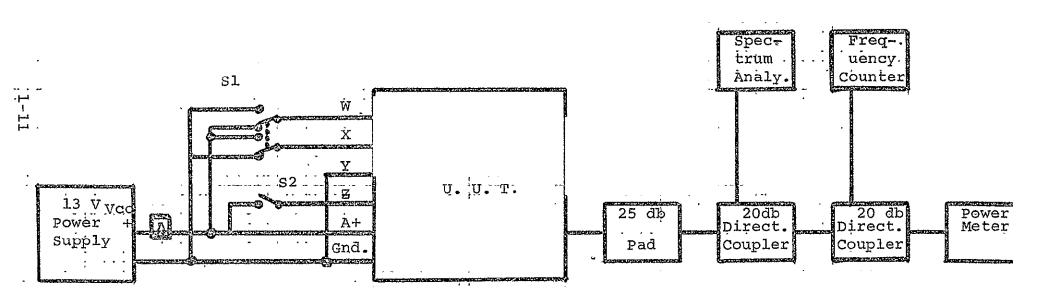

# APPENDIX A. Functional Performance Tests

•

٠.

.

.

• •

|   | Figure |                                                                                | Page |

|---|--------|--------------------------------------------------------------------------------|------|

|   | 1-1    | Data Collection Platform (Artist's Concept)                                    | 1-2. |

|   | 2-1    | Data Collection Platform                                                       | 2-2  |

|   | 3-1    | DCP Transmitter Assembly Al                                                    | 3-2  |

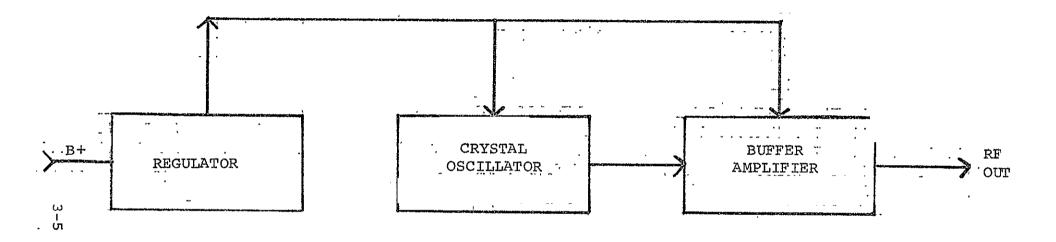

| , | 3-2    | Oscillator-Buffer-Regulator, Block Diagram                                     | 3-5  |

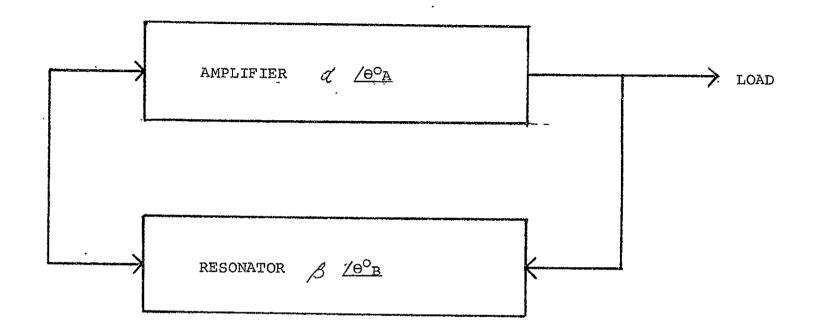

|   | 3-3    | Oscillator Loop, Block Diagram                                                 | 3-6  |

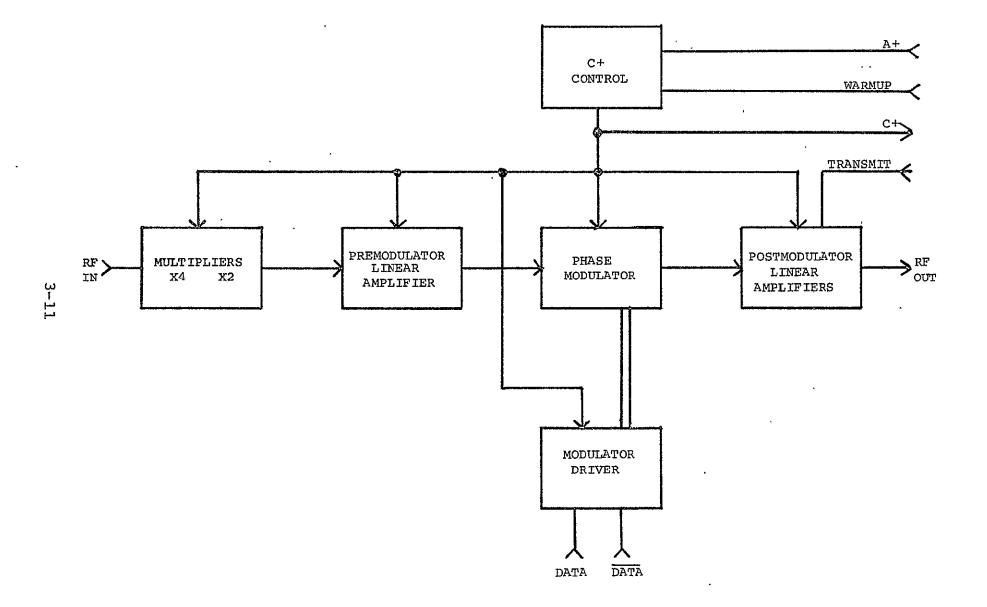

|   | 3-4    | Multiplier-Modulator, Block Diagram                                            | 3-11 |

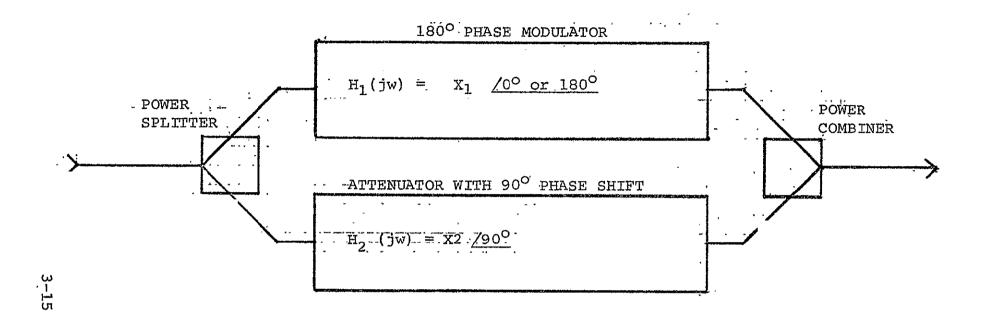

|   | 3–5    | Phase Modulator, Block Diagram                                                 | 3-15 |

|   | 3–6    | RF Amplifier, Mobile, Block Diagram                                            | 3-18 |

|   | 3-7    | RF Amplifier, Fixed, Block Diagram                                             | 3-19 |

|   | 3-8    | Frequency Stability Data                                                       | 3-26 |

|   | 3-9    | Transmitter                                                                    | 3-35 |

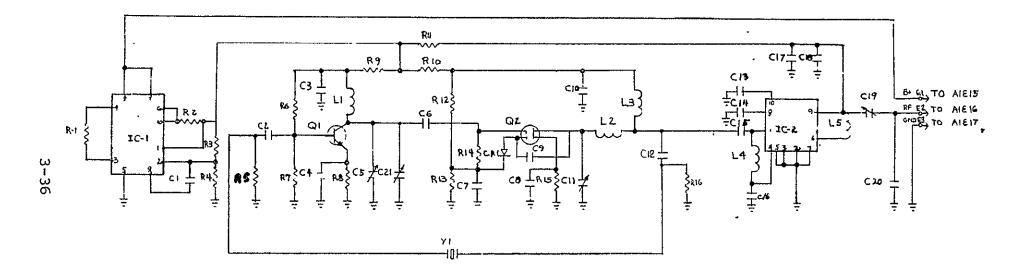

|   | 3-10   | Oscillator and Buffer                                                          | 3-36 |

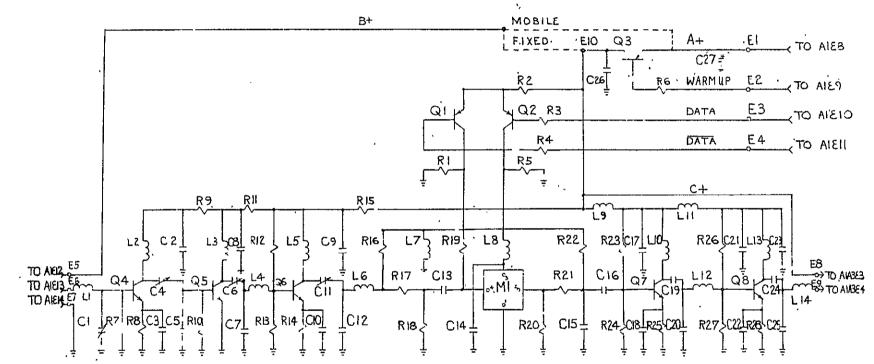

|   | 3-11   | Multiplier/Modulator                                                           | 3-39 |

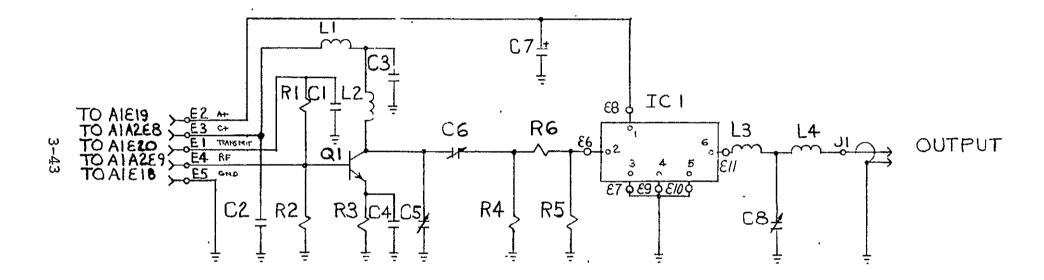

|   | 3-12   | RF Amplifier, Mobile                                                           | 3-43 |

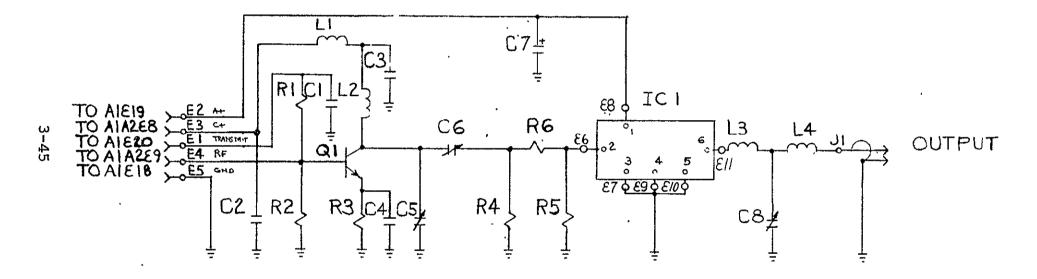

|   | 3-13   | RF Amplifier, Fixed                                                            | 3-45 |

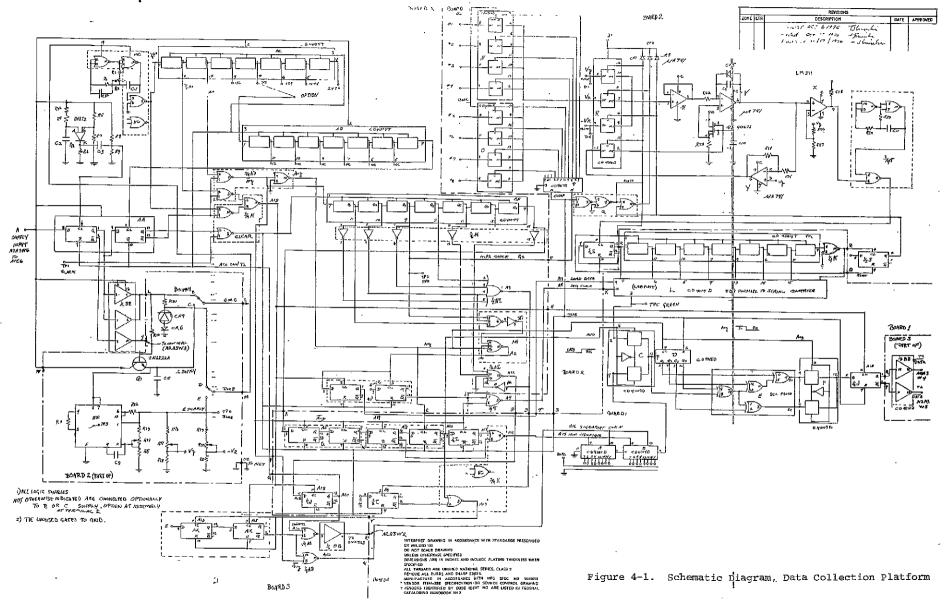

|   | 4-1    | Schematic Diagram, Data Collection Platform                                    | 4-2  |

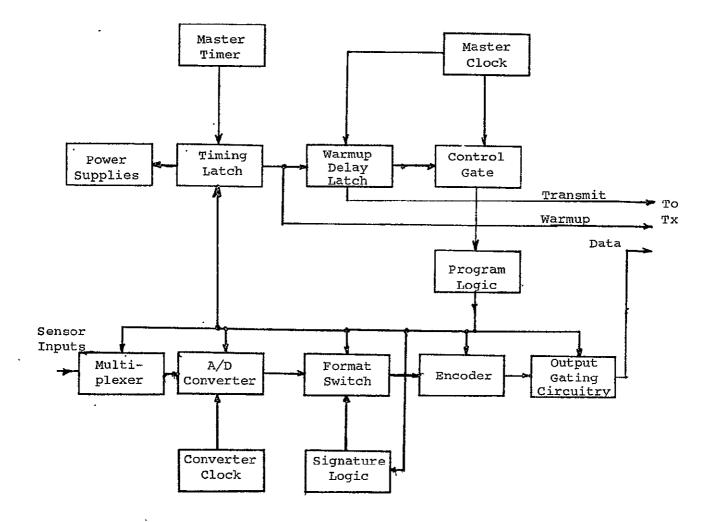

|   | 4-2    | Data Collection Platform, Digital Logic,<br>Block Diagram                      | 4-3  |

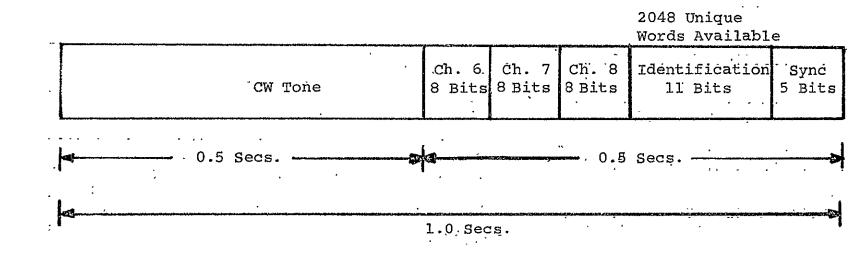

|   | 4-3    | Data Frame Format, Mobile Platform                                             | 4-5  |

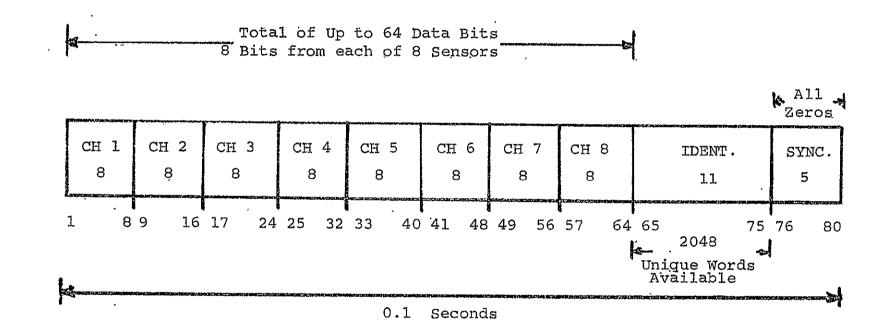

|   | 4-4    | Message Format, Fixed Platform                                                 | 4-6  |

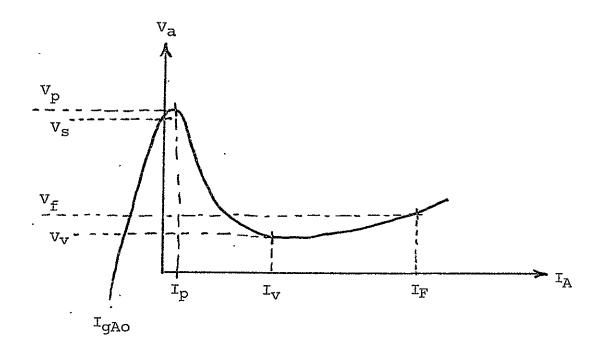

|   | 4-5    | Programmable Unijunction, $V_a$ , $I_a$ Curve                                  | 4-8  |

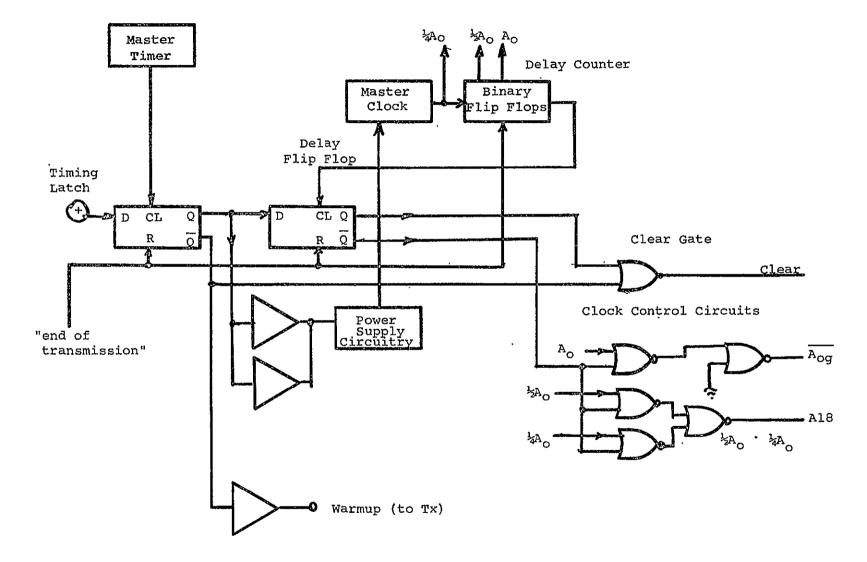

|   | 4-6    | Timing Latch, Delay Latch, Clock Control,<br>Clear Circuits, Schematic Diagram | 4-10 |

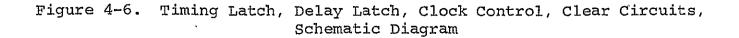

|   | 4-7    | Data Collection Platform, Overall Timing .<br>Diagram                          | 4-12 |

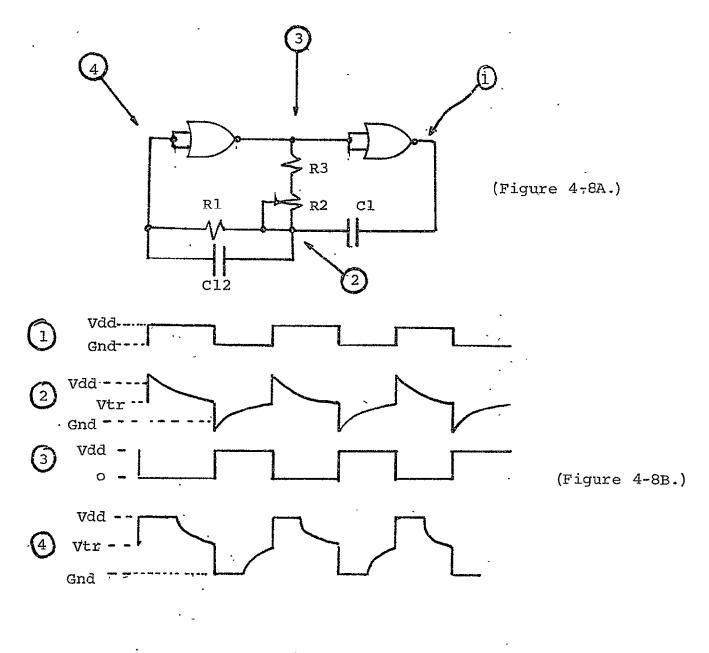

|   | 4-8    | Timing Diagram for Master Clock                                                | 4-15 |

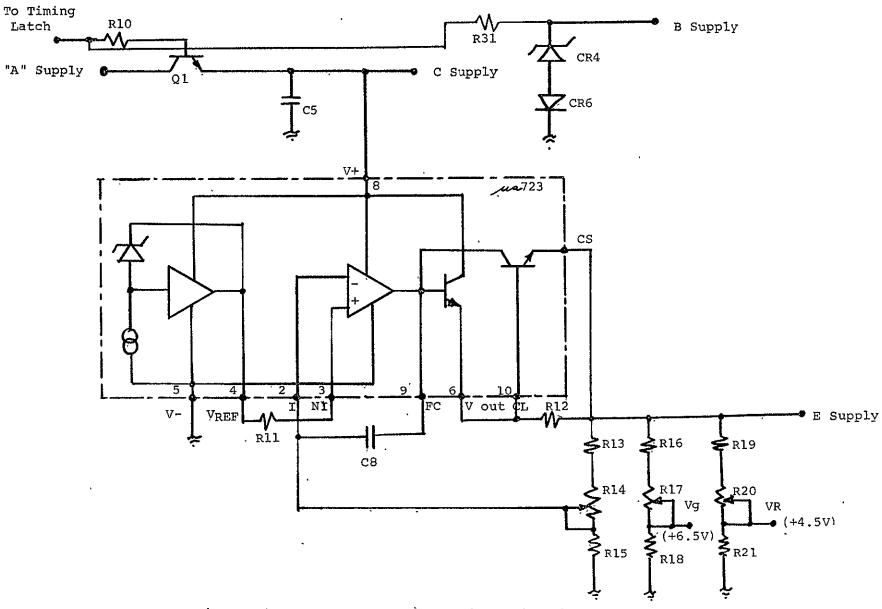

|   | 4-9    | Power Supply, Schematic Diagram                                                | 4-18 |

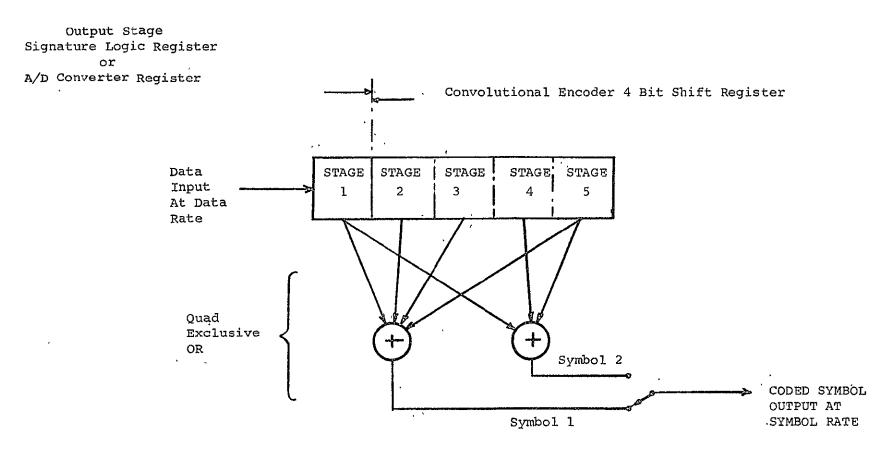

|   | 4-10   | Convolutional Encoder, Block Diagram                                           | 4-23 |

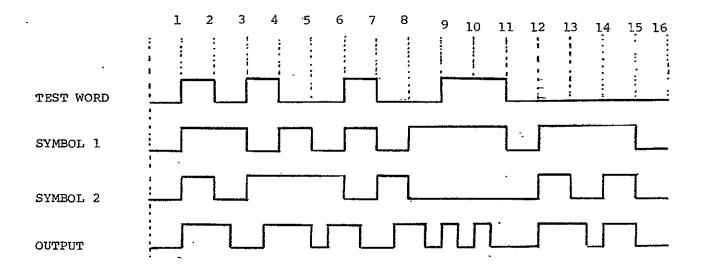

|   | 4-11   | Convolutional Encoder Waveforms                                                | 4-24 |

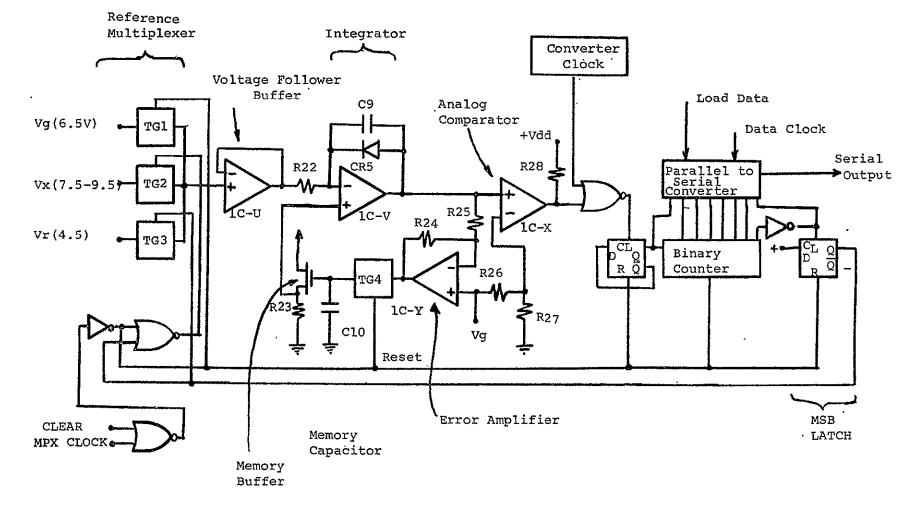

|   | 4-12   | A/D Converter                                                                  | 4-26 |

|   |        |                                                                                |      |

V

.

## LIST OF ILLUSTRATIONS (Cont.)

.

.

| . <u>Figure</u> |                                                                          | Page   |

|-----------------|--------------------------------------------------------------------------|--------|

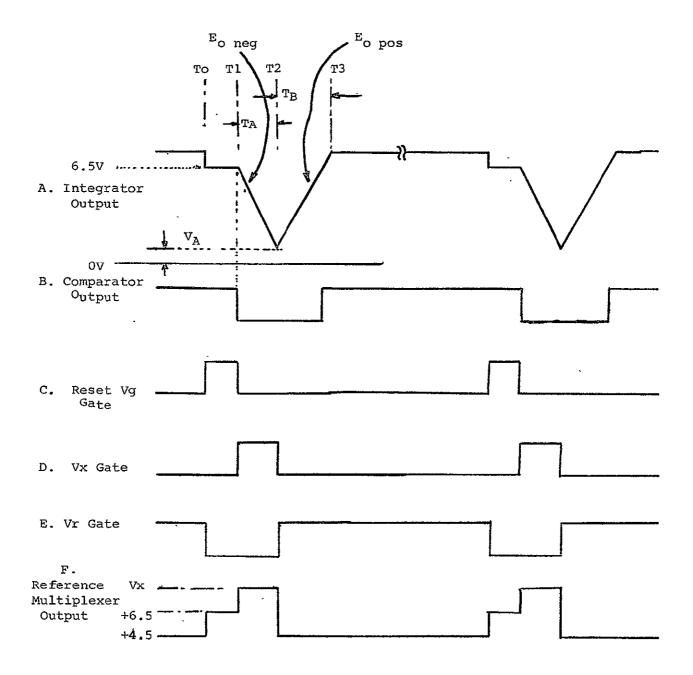

| 4-13            | A/D Converter, Timing Diagram                                            | 4-27   |

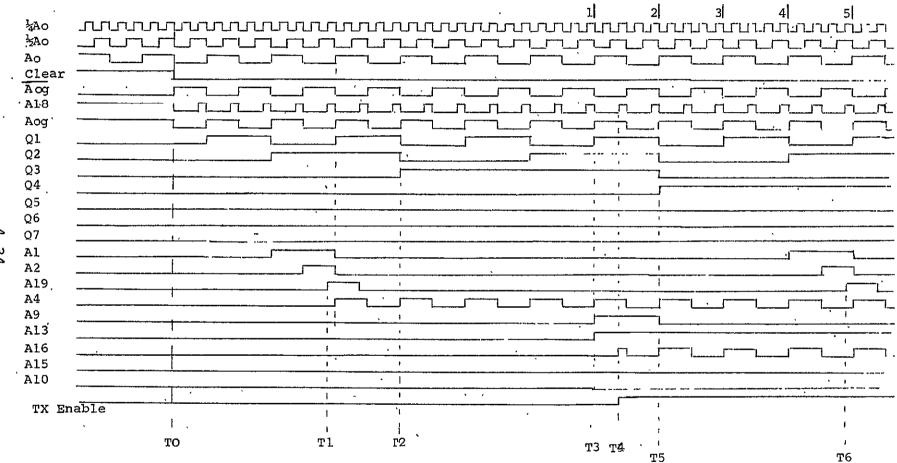

| 4-14            | Data Collection Platform, Timing Diagram,<br>(1st 5 Bits - Post Clear)   | 4-34   |

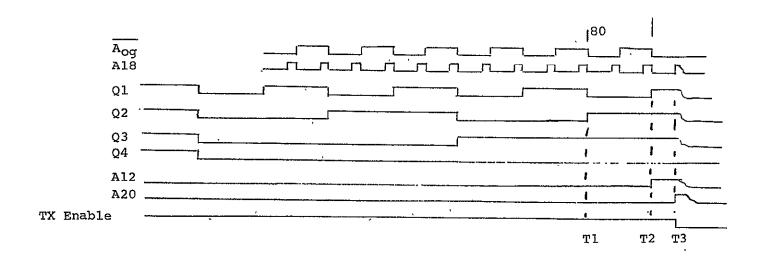

| 4-15            | Data Collection Platform, Timing Diagram,<br>End of Sequence             | 4-36   |

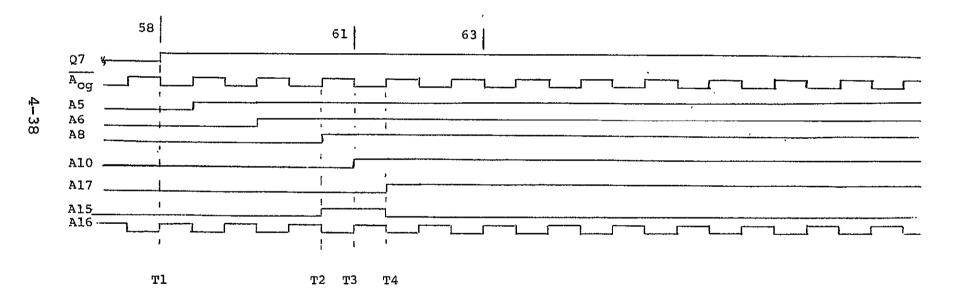

| 4-16            | Data Collection Platform, Timing Diagram<br>(Bits 58-63, AlO Generation) | 4-38   |

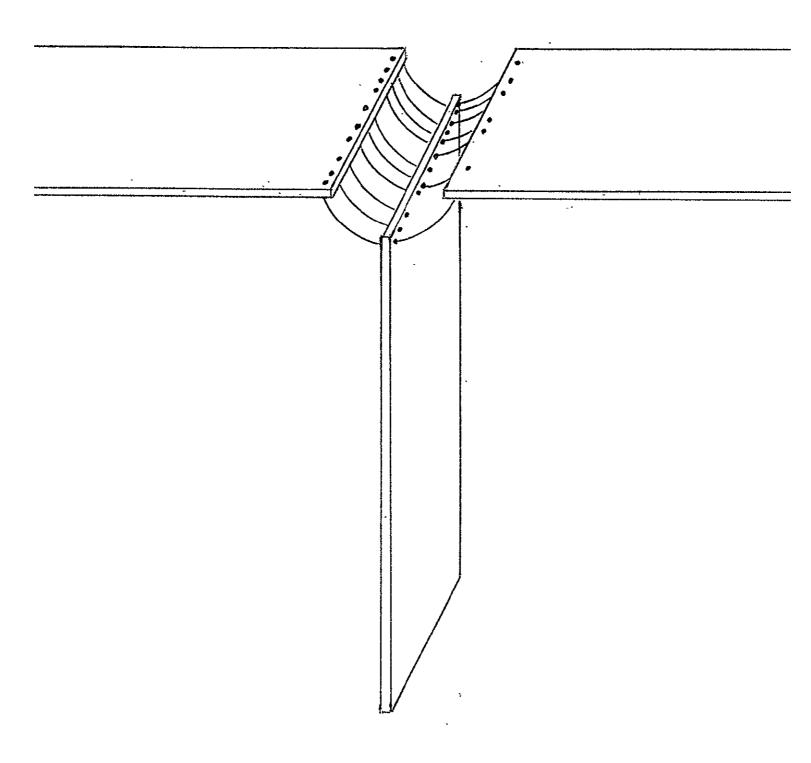

| 5-1             | Disposition of Logic Boards                                              | 5-2    |

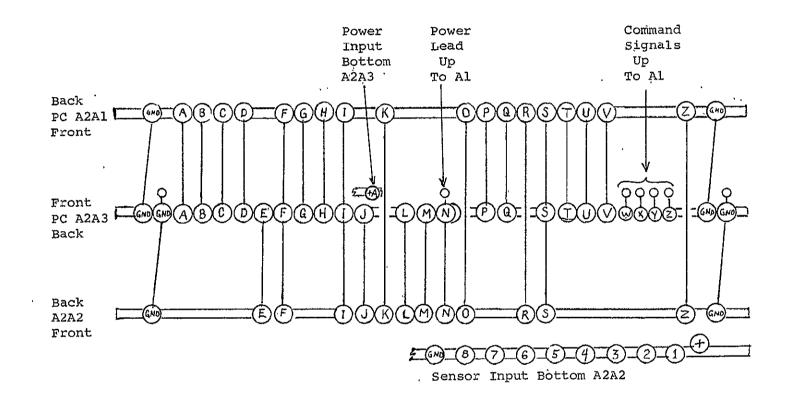

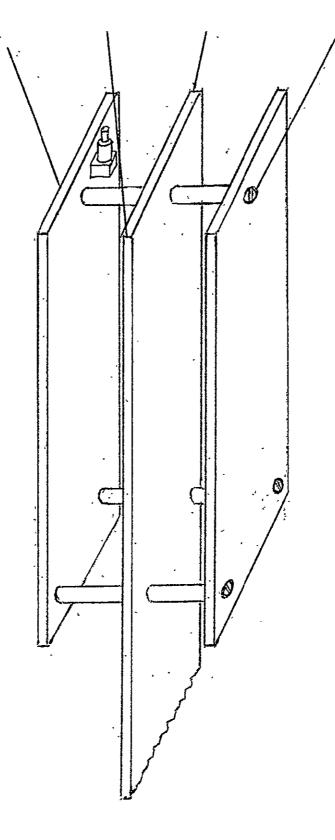

| 5-2             | Intraboard Connections                                                   | 5-3    |

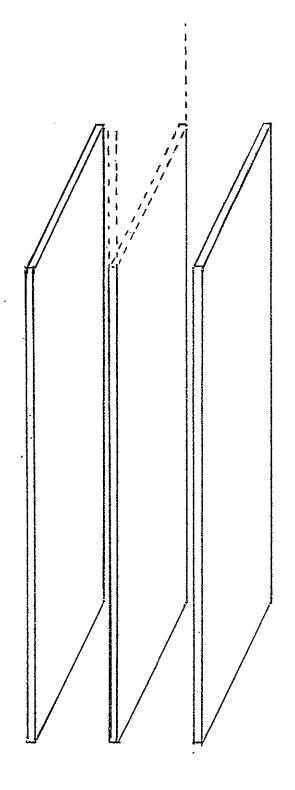

| 5-3             | Logic Boards in Position for Servicing                                   | 5–5    |

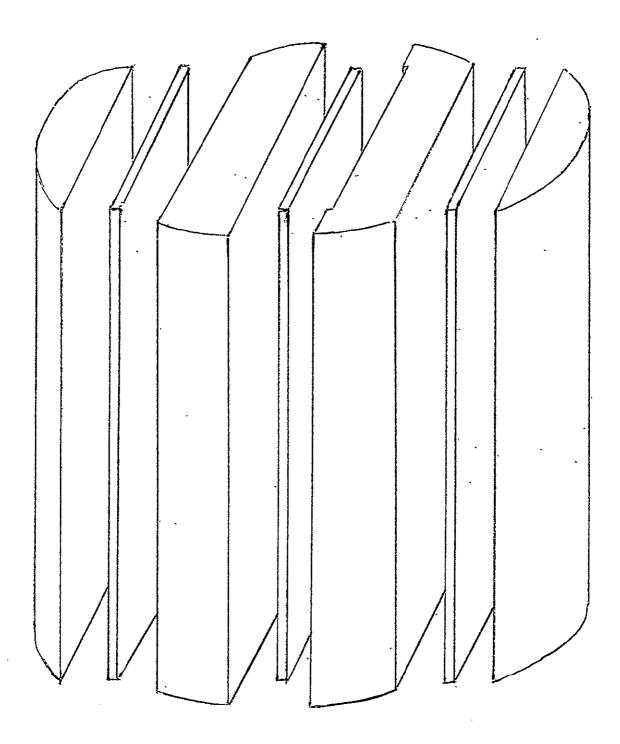

| 5-4             | Logic Boards and Foam Separators                                         | 5-6    |

| 5-5.            | RF Boards                                                                | 5-8    |

| 5-6             | Support Covering                                                         | 5-9    |

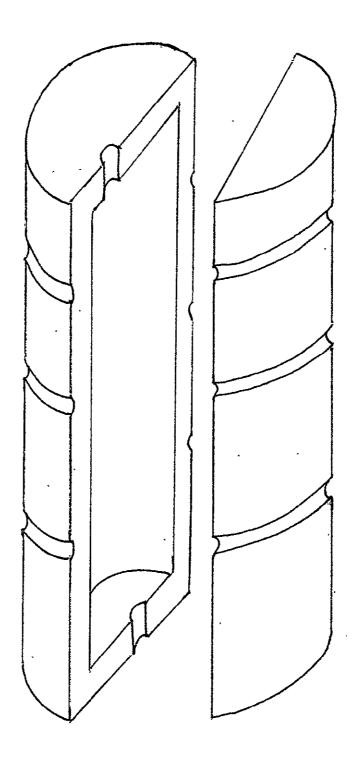

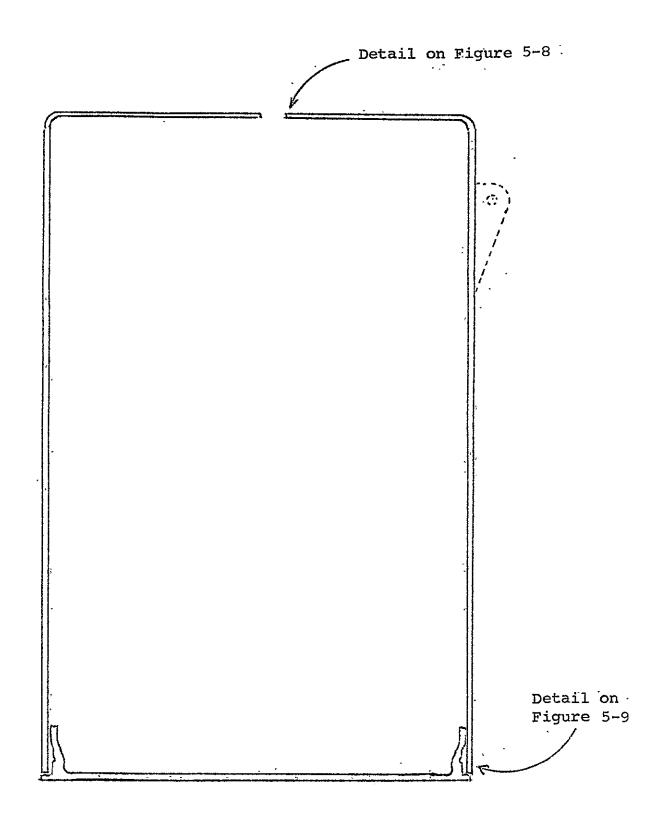

| 5-7             | Molded Waterproof Case                                                   | 5-10   |

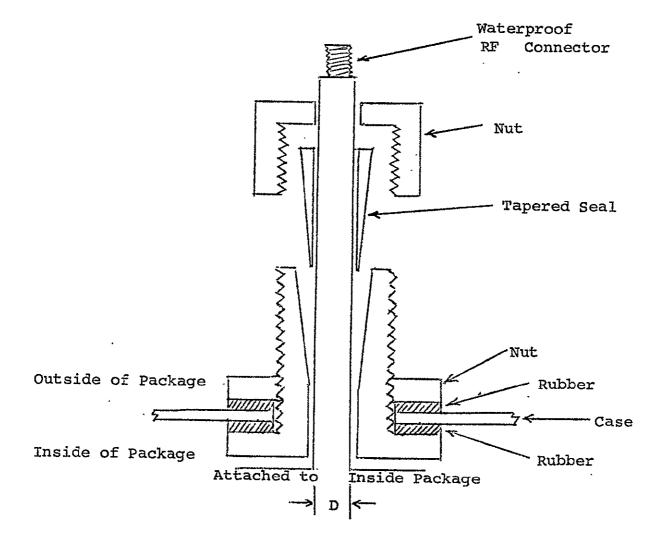

| 5-8             | Top òf Package, Waterproof Seal                                          | 5-11   |

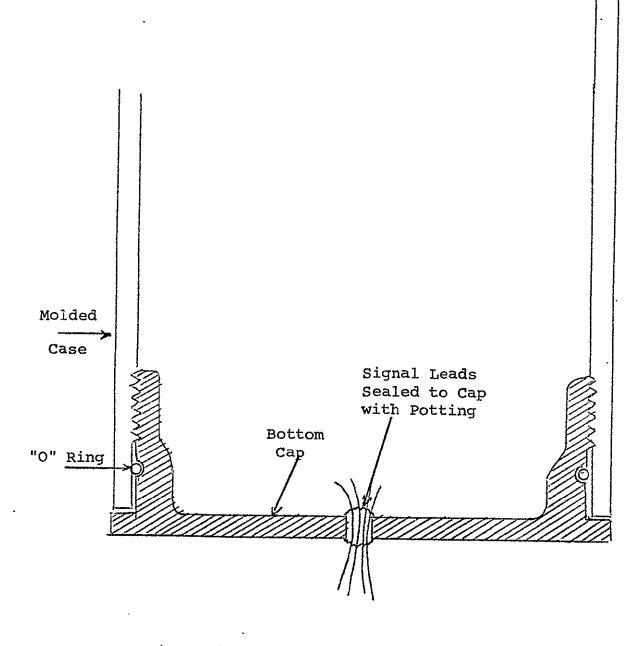

| 5-9             | Bottom of Package, Waterproof Seal                                       | 5-13   |

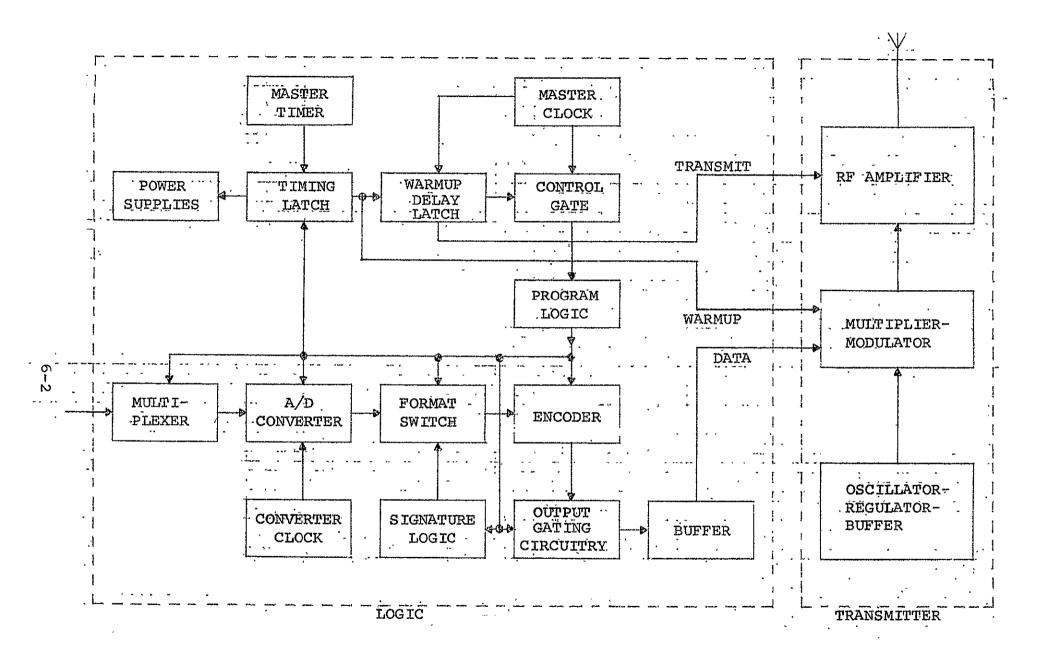

| 6-1             | Data Collection Platform, Functional<br>Block Diagram                    | 6-2    |

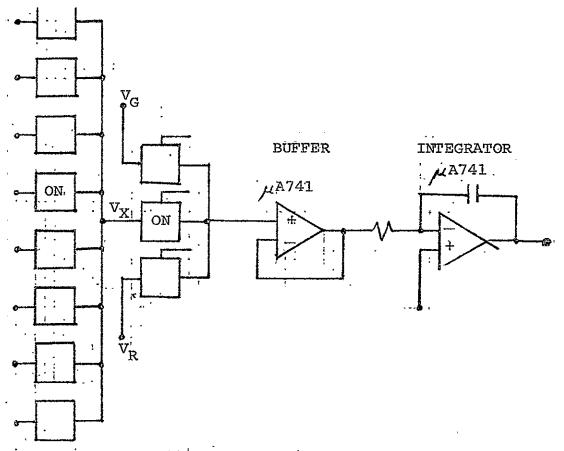

| 7-1 .           | A/D Converter-Multiplexer                                                | 7-8    |

| 7-2             | Buffer Amplifier                                                         | 7-8    |

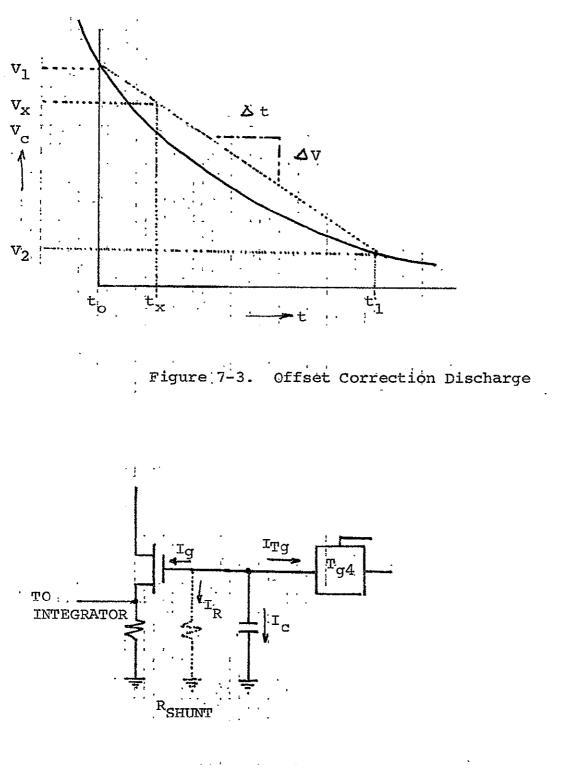

| 7-3             | Offset Correction Discharge                                              | 7-11   |

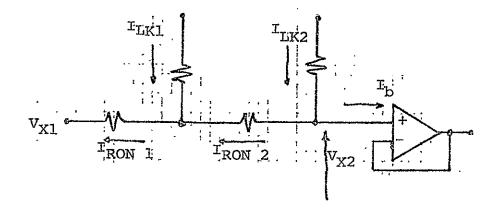

| 7-4             | Conversion Discharge Paths                                               | 7-11   |

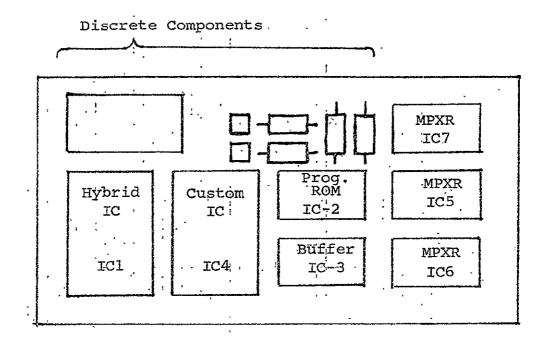

| 8-1             | Integrated Model No. 1                                                   | 8-4    |

| 8-2             | Multifunction Converter/Register                                         | 8-8    |

| 8-3             | Sensor Parallel Output                                                   | . 8-11 |

|                 |                                                                          |        |

## LIST OF TABLES.

| Table |                                            | Page             |

|-------|--------------------------------------------|------------------|

| 2-1   | Mobile Platform Results                    | 23               |

| 2-2   | Fixed Platform Results                     | 2-5              |

| · 3-1 | Transmitter Platform Différences           | 3-1              |

| 4-1   | Digital Platform Differences               | 4-1              |

| 4-2   | Warmup Delay Options                       | 4-14             |

| 4-3   | Program Logic Output Signals               | 4-32             |

| 5-1   | Frangibility                               | 5-15             |

| 5-2   | Weight, Size, and Density                  | 5-16             |

| 6-1   | Platform Estimated Costs (Quantity of 100) | 6-3 <sup>-</sup> |

| 6-2   | Platform Cost Evaluation                   | 6-3              |

|       |                                            |                  |

#### SECTION 1

#### INTRODUCTION

## 1.1 SYSTEM ASPECTS

Signals transmitted from data-collection platforms (DCP) in various parts of the world are received, processed, and stored by a low-orbit satellite on a one-way link. When the satellite is in view of a NASA ground station, the information is transmitted by the satellite to the ground.

The information obtained from the satellite is then processed at a data reduction center. Processing equipment detects each signal and extracts the frequency, time, platform signature, and sensor data. The extracted time information is referenced to the real time of receipt of the platform signals at the satellite. The signal-processing equipment is used to determine the position and/or velocity of each drifting platform as required.

#### 1.2 PLATFORMS

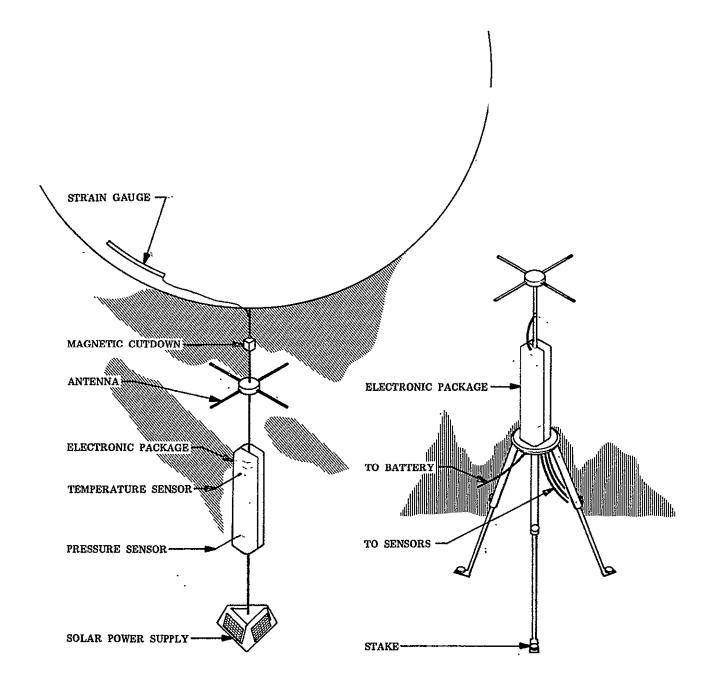

Two types of platforms (see Figure 1-1) have been developed:

- a. MOBILE DATA COLLECTION PLATFORM (MDCP) for use on constant level balloon vehicles.

- b. FIXED DATA COLLECTION PLATFORM (FDCP) for use at remote ground locations.

Figure 1-1. Data Collection Platform (Artist's Concept)

Those carried by balloons employ a highly stable oscillator to enable determination of platform position and/or velocity by use of Doppler techniques. An absolute a priori knowledge of the transmitted frequency is not required; what is important is that the frequency drift be controlled and small. Both types of platforms are randomly timed; their transmission of environmental data is independent of the receiving satellite. Since no satellite interrogation is necessary, no receiver or decoding equipment is required. As a result, low cost, reduced weight, and minimum power consumption are achieved.

Environmental information obtained by both types of platform sensors is sampled, converted to digital format, encoded, and used to phase-shift key an RF transmitter. The digital portion employs the latest COS/MOS technology to enhance low power dissipation and noise immunity. Exceptional transmission quality is attained through use of a sophisticated oscillator for high-stability, narrowband multipliers for spurious reduction; and stable high-Q amplifiers.

Since the demand for a large number of platforms are required, the electronic package costs should be minimum. Toward this end, American Electronic Laboratories, Inc. has developed an essentially common type of MDCP and FDCP to thus extend the low cost philosophy.

## SECTION 2

## SUMMARY

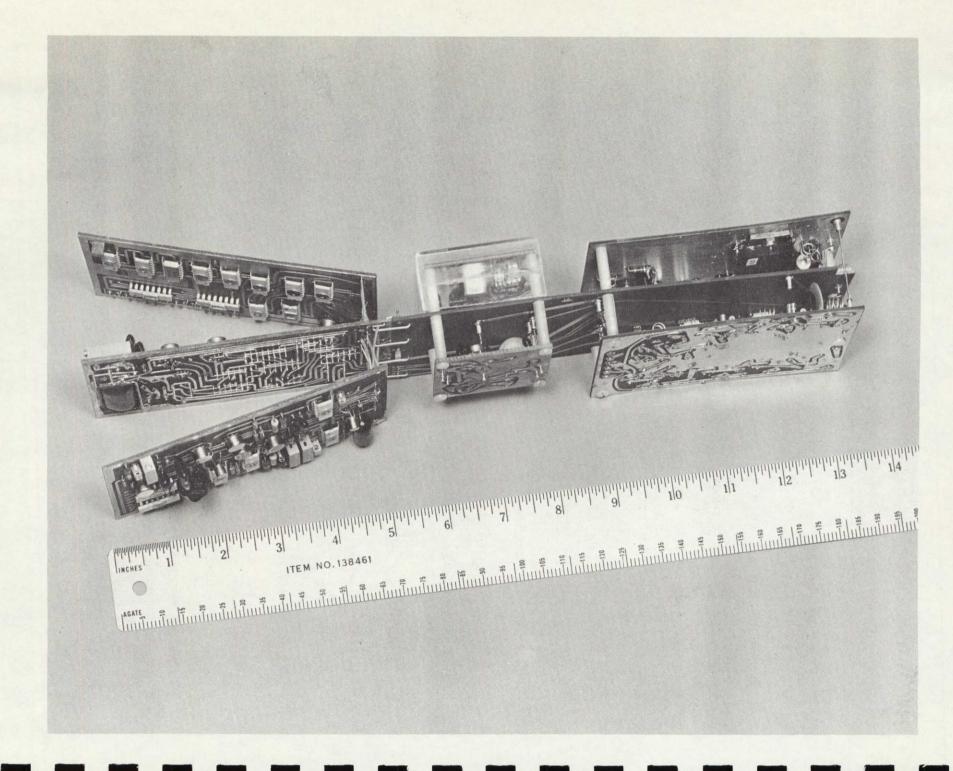

The DCP is shown in Figure 2-1. Because of the similarity between the mobile and fixed units, the layouts and components are essentially common. The three "spread" boards contain the digital logic sections; the oscillator assembly and buffers are in the center portion; and the RF assembly is at the end.

Examination of the specifications, on a line-by-line basis, indicates the successful performance of the platforms developed. A review of Section 8 further details how additional improvements can be incorporated to further reduce the overall cost of the lowcost high-quality data collection platform.

## 2.1 MOBILE PLATFORM

Table 2-1 indicates the specifications desired and the final performance criteria of the mobile platform. During the initial phases of this program, it was expected that the oscillator would require the greatest concentration of engineering expertise. Conferences were held with Fort Monmouth personnel and with leading crystal manufacturers in order to obtain technical and guideline information. As a result, an advanced oscillator assembly has been produced that features the essential component and technical qualities desired.

Figure 2-1. Data Collection Platform

## TABLE 2-1. MOBILE PLATFORM RESULTS

.

| PARAMETER                                                                                                               | CUSTOMER<br>SPECIFICATIONS          | TYPICAL PERFORMANCE<br>SPECIFICATIONS                 |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|--|

| Independent Sensor Inputs                                                                                               | 2 Channel                           | 3 Channel (Unused channels<br>wired for CW output)    |  |

| Symbol Rate                                                                                                             | 160 Symbol/sec <u>+0.125%</u>       | 160 Symbols/sec <u>+</u> 0.125%                       |  |

| Output Symbol Length                                                                                                    | 80 Symbols                          | 80 Symbols                                            |  |

| Total Transmission Format<br>Time                                                                                       | l Second                            | l Second                                              |  |

| CW Tone Interval                                                                                                        | 0.5 Second                          | 0.5 Second                                            |  |

| Bits/Data Word                                                                                                          | 8 Bits                              | 8 Bits                                                |  |

| Identification Sequence<br>Length                                                                                       | ll Bits                             | ll Bits                                               |  |

| Symc Code Sequence                                                                                                      | 5 Bits, at zero                     | 5 Bits, at zero                                       |  |

| Timer Repetition Interval                                                                                               | 60 <u>+</u> 4.5 Seconds             | 60 <u>+</u> 4.5 Seconds                               |  |

| Analog Data Inputs                                                                                                      | 7.5 - 9.5 VDC ( $\Delta = 2V$ )     | 7.5-9.5 VDC (△= 2V)                                   |  |

| Analog Input Z During Sample                                                                                            | > 100k                              | > 10M                                                 |  |

| Prime Power                                                                                                             | 12 VDC <u>+</u> 1 VDC               | 12 VDC <u>+</u> 1 VDC                                 |  |

| Prime Power Ripple<br>Idc Peak @ 12 VDC<br>Idc Ave. @ 12 VDC<br>Pdc Peak @ 12 VDC<br>Pdc Ave. @ 12 VDC<br>Pdc Quiescent | 1 mv RMS<br>1.0a<br>10 ma<br><br>   | 1 mv RMS<br>0.40a<br>10 ma<br>4.8W<br>120 mw<br>22 mw |  |

| Logic Noise Tolerance                                                                                                   | lV, either state                    | 4.4V min., either state                               |  |

| A/D Conversion Accuracy                                                                                                 | 7 Bit (~1%)                         | 7 Bit (>1%)                                           |  |

| Warmup Time                                                                                                             |                                     | 1.56 seconds                                          |  |

| Operating Temperature Range                                                                                             | 25°C <u>+</u> 5°C                   | 25°C <u>+</u> 5°C                                     |  |

| Storage Temperature Range                                                                                               | $-54^{\circ}$ C to $+49^{\circ}$ C  | -55°C to +80°C                                        |  |

| Weight                                                                                                                  | 550g                                | 614g incl. insulation                                 |  |

| Osc. Short Term Stability                                                                                               | 1 in 10 <sup>9</sup> (for 1/2 sec.) | < 1 in 10 <sup>9</sup>                                |  |

| Mean Drift                                                                                                              | 0.2 Hz/min. for 15 min.             | 3.56 Hz/15 min. isothermal best                       |  |

| Tx. Output Frequency                                                                                                    | 403.1 MHz <u>+</u> 0.005%           | 403.1 MHz <u>+</u> 0.005%                             |  |

| Tx. Output Spur Rejection                                                                                               | > 60 dB                             | > 55 dB @ 12V                                         |  |

| PSK Phase Shift                                                                                                         | 170° <u>+</u> 5°                    | 170° <u>+</u> 5°                                      |  |

| Transmitter Output Power                                                                                                | < 1 watt                            | 1 watt                                                |  |

| Total Volume                                                                                                            |                                     | 240 cu. in.                                           |  |

The logic section concentrated on using the latest COS/MOS components to thus reduce power consumption. A review of Table 2-1 indicates that the system peak current is 50 percent better than required in the specification. Further analysis is required in the A/D section to improve the temperature coefficient qualities in order to meet the bit tolerance over the environmental operating range.

The packaging technique employed features ease of assembly, interdependence of the RF and logic sections, and layouts compatible with frangability requirements.

## 2.2 FIXED PLATFORM

Table 2-2 indicates the applicable specifications and results obtained from the fixed platform. The same oscillator used in the mobile platform was utilized in this system. Because of the reduced symbol length (0.1 seconds) it is mandatory that the "turn on" stability be small to keep the variations in the transmit frequency at a minimum. The logic and transmitter assemblies are essentially identical with those of the mobile platform. This philosophy was utilized at the beginning of the program in order to plan and incorporate commonality factors.

## TABLE 2-2. FIXED PLATFORM RESULTS

| PARAMETER                                                                                                                 | CUSTOMER<br>SPECIFICATIONS               | TYPICAL PERFORMANCE<br>SPECIFICATIONS                     |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------|

| Independent Sensor Inputs                                                                                                 | 8 Channel                                | 8 Channel                                                 |

| Symbol Rate                                                                                                               | 1600 Symbols/sec <u>+</u> 0.125%         | 1600 Symbols/sec <u>+</u> 0.125%                          |

| Output Symbol Length                                                                                                      | 160 Symbols                              | 160 Symbols                                               |

| Total Transmission Format<br>Time                                                                                         | 0.1 Second                               | 0.1 Second                                                |

| CW Tone Interval                                                                                                          |                                          | ,                                                         |

| Bits/Data Word                                                                                                            | 8 Bits                                   | 8 Bits                                                    |

| Identification Sequence<br>Length                                                                                         | 11 Bits                                  | 11 Bits                                                   |

| Sync Code Sequence                                                                                                        | 5 Bits, at zero                          | 5 Bits, at zero                                           |

| Timer Repetition Interval                                                                                                 | 120 <u>+</u> 10 sec.                     | 120 <u>+</u> 10 sec.                                      |

| Analog Data Inputs                                                                                                        | 7.5 - 12.5 VDC ( $\Delta = 5.0V$ )       | 7.5 - 9.5 VDC ( $\Delta = 2.0V$ )                         |

| Analog Input Z During Sample                                                                                              | > 100k                                   | -> 10M .                                                  |

| Prime Power                                                                                                               | 12 VDC <u>+</u> 1 VDC                    | 12 VDC <u>+1</u> VDC                                      |

| Prime Power Ripple<br>Idc Peak @ 12 VDC<br>Idc Ave. @ 12 VDC<br>Pdc Peak @ 12 VDC<br>'Pdc Ave. @ 12 VDC<br>:Pdc Quiescent | 1 mv RMS<br>3.0a<br>4.0 ma<br>           | 1 mv RMS<br>1.3a<br>2.12 ma<br>15.6W<br>25.5 mw<br>< 1 mw |

| Logic Noise Tolerance                                                                                                     | lv, either state                         | 4.4V min., either state                                   |

| A/D Conversion Accuracy                                                                                                   | 7 Bit (> 1%)                             | 7 Bit (>1%)                                               |

| Warmup Time                                                                                                               |                                          | 1.248 Seconds                                             |

| Operating Temperature Range                                                                                               | -54 <sup>0</sup> C to +49 <sup>0</sup> C | Unit designed for, but not tested from -54°C to +49°C     |

| Storage Temperature Range                                                                                                 | $-54^{\circ}$ C to $+49^{\circ}$ C       | -55°C to +80°C                                            |

| Weight                                                                                                                    | 4082g                                    | 614g incl. insulation                                     |

| Osc. Short Term Stability                                                                                                 | 1 in 10 <sup>9</sup>                     | <li>&lt; 1 in 10<sup>9</sup></li>                         |

| Mean Drift                                                                                                                | <u>+</u> 0.005%                          | <u>+</u> 0.005%                                           |

| Tx. Output Frequency                                                                                                      | 402.1 MHz <u>+</u> 0.005%                | 402.1 MHz <u>+</u> 0.005%                                 |

| Tx. Output Spur Rejection                                                                                                 | > 60 dB                                  | > 60 dB                                                   |

| PSK Phase Shift                                                                                                           | 170° <u>+</u> 5°                         | 170° <u>+</u> 5°                                          |

| Transmitter Output Power                                                                                                  | < 5 watts                                | 5 watts                                                   |

| Total Volume                                                                                                              | < 330 cu. in.                            | 240 cu. in.                                               |

.

#### SECTION 3

#### PLATFORM TRANSMITTER SYSTEM DESCRIPTION

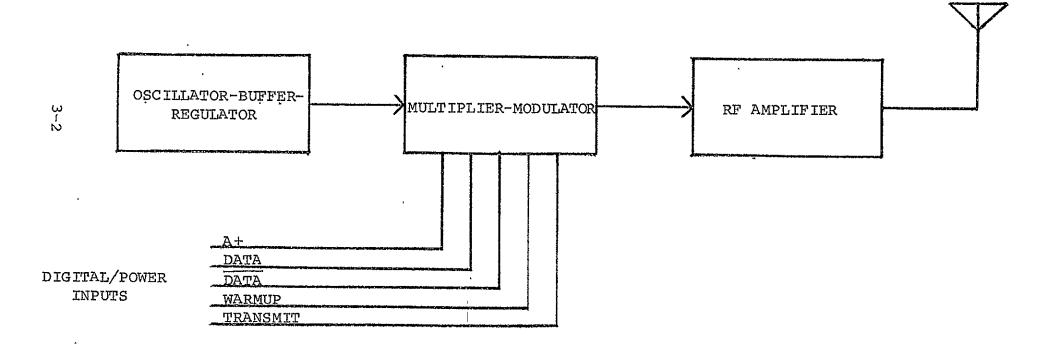

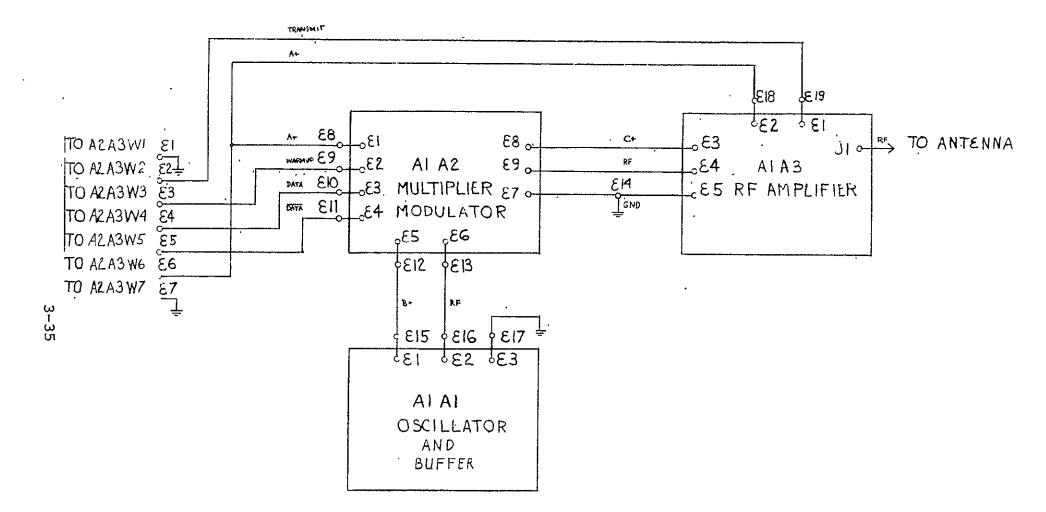

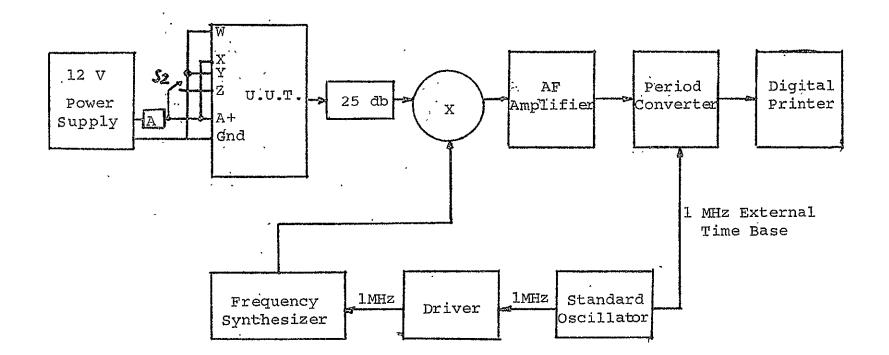

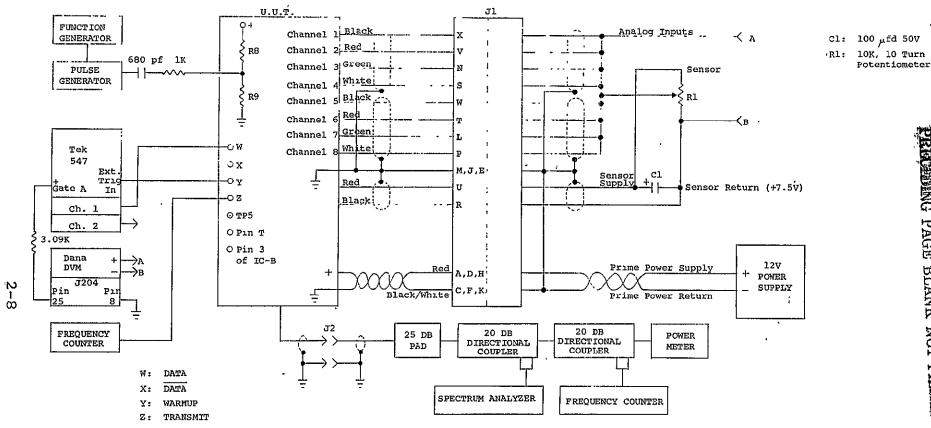

The transmitter assembly of the Data Collection Platform (DCP) shown in Figure 3-1 consists of an oscillator-buffer regulator, a multiplier modulator, and a RF amplifier. This functional block diagram suffices for the mobile and fixed platforms because of the commonality qualities of the platforms. The essential différences pertain only to their stability output power capability and the final transmitted frequency, as detailed in Table 3-1. From a circuit and theoretical standpoint, the two units can be considered identical. Therefore, this report will differentiate between the two types of platforms only where further clarification is necessary.

#### TABLE 3-1.

| FUNCTION                         | FIXED<br>PLATFORM | MOBILE<br>PLATFORM        |

|----------------------------------|-------------------|---------------------------|

| Fundamental Oscillator Frequency | 50.2625 MHz       | 50.3875 MHz               |

| Final Transmitter Frequency      | 402.1 MHz         | 403.1 MHz                 |

| Power Output                     | 5 watts ·         | l watt                    |

| Short-Term Stability             |                   | l part in 10 <sup>9</sup> |

#### TRANSMITTER PLATFORM DIFFERENCES

,

The oscillator subassembly generates the highly stable frequency; the multiplier-modulator subassembly increases the frequency by a factor of eight and phase modulates the signal (phase states differ by 170 degrees <u>+5</u> degrees); an RF amplifier subassembly increases the power output level to the specified level.

The oscillator assembly exhibits a one-half-second, short-term stability of better than 1 part in 10<sup>9</sup>, and has exhibited a drift rate (isothermal best) of 3.56 Hz in a 15-minute interval. The oscillator-buffer-regulator is designed to maintain 0.005 percent frequency tolerance from -54 degrees to +49 degrees C. A buffer amplifier prevents load variations from affecting the oscillator frequency. A separate regulator is used to control the oscillator voltage. The multiplier-modulator and RF amplifier and phase modulator is designed to increase the power level of the oscillator without degrading the short-term stability or generating spurious signals.

#### 3.1 GENERAL DESCRIPTION

3.1.1 Oscillator-Buffer

#### 3.1.1.1 Crystal Oscillator Loop

The crystal oscillator in the Mobile Data Collection Platform (MDCP) must exhibit a frequency jitter of better than 1 part in  $10^9$

for a one-half-second sampling interval with an average drift rate in a 15-minute period of 0.2 Hz/minute. Both the fixed and the mobile platforms must have an overall frequency tolerance of  $\pm 0.005$  percent; the environmental operating range of the fixed platform is -54 degrees C to  $\pm 49$  degrees C; the mobile platform must operate from  $\pm 20$  degrees C to  $\pm 30$  degrees C.

The oscillator-buffer-regulator subassembly is shown in Figure 3-2. The condition for oscillation for the crystal oscillator loop shown in detail in Figure 3-3, is that the component of loss with zero phase shift in the crystal be offset by the zero phase shift component of amplifier gain. If a phase shift occurs in the amplifier, the oscillator loop must change frequency until the crystal provides a phase shift opposite to that of the amplifier. The less the oscillator loop changes in frequency to compensate for amplifier phase variations, the better the crystal. It can be shown that the fractional frequency shift caused by a phase shift in the amplifier is equal to the phase shift in radians divided by twice the effective Q of the crystal.

The effective Q of the crystal in the aforementioned relationship is determined not only by the unloaded Q of the crystal itself but also by the effective source and load impedances presented by the amplifier. Reducing the source and load impedances of the

.

Condition for Oscillation  $C( \ge 1)$  $\Theta_{\rm A} + \Theta_{\rm B} = n(360^{\circ})$

Figure 3-3. Oscillator Loop

crystal to as small a level as possible will provide the greatest fractional frequency stability. However, reducing the input and output impedances of the amplifier either reduces the gain or causes increased phase shift within the amplifier. A tradeoff must be made between the effective Q of the crystal and the gain of the phase shift of the amplifier to produce the best overall results.

The level of operation of the oscillator loop must also be chosen on the basis of conflicting requirements. The short-term stability is inversely related to the signal-to-noise ratio of the oscillator loop. This can be conceived as noise in the loop combining with the sinusoidal oscillation to slightly shift the positions of the zero crossings. Hence, on a short-time scale, noise causes a slight frequency jitter. Since the noise produced in any given amplifier is at some constant absolute level, the greater the level of oscillation the better the signal-to-noise ratio and the better the noise performance of the oscillator.

The crystal itself presents the conflicting requirement because the series resonant frequency of the crystal is related to the drive level. As a rule of thumb, the frequency-drive sensitivity is one part per million per milliwatt. If the crystal were operating at the one milliwatt level and the drive increased

by one hundred percent, the resonant frequency of the crystals would change by one part per million. If the crystal were operating at the microwatt level and the drive increased one hundred percent, the resonant frequency would change by one part per billion. The lower the operation level the better. A level of operation must be chosen that is low enough to minimize the amplitude effect while not requiring a costly low noise figure amplifier.

Often, oscillator circuits are designed with the level of oscillation being determined by the saturation level of one of the stages in the oscillator. Since this level is temperature dependent, it causes amplitude and hence frequency variations with changes in the ambient temperature; in addition, it requires that the circuit be allowed considerable time to warm up after initial turn-on. If, however, an amplitude limiter is included in the oscillator loop (see Figure 3-3) amplitude variations can be greatly limited and the absolute level of limiting can be made almost constant. Higher levels of operation with the associated improvement in short-term performance can be achieved without the amplitude frequency effect becoming the main source of oscillator degradation. Limiters are being utilized which require very little warmup and hence add greatly to the pulsed performance of the oscillators in the DCP.

Because of the direct relationship of the phase shift in the amplifier to the output frequency of the oscillator, the devices used in the oscillator loop must be biased as stably as possible. Devices self-biased with voltage feedback are utilized. This is the most stable form of self-bias.

### 3.1.1.2 Buffer Amplifier

It is important that the loading of the buffer amplifier on the oscillator loop does not change and thereby cause phase shifts in the loop. This requirement is met by designing the buffer amplifier to lightly load the oscillator, and designing the input impedance of the buffer amplifier to be constant. The input impedance is dependent upon biasing or supply effect, and the effect of reverse gain reflecting changes of load impedance to the input. This is necessary because the multipliers which load the buffer amplifier are operated in Class C and have wide variations in input impedance with supply voltage, temperature, and level of operation.

The RF/IF cascode amplifier configuration chosen has bias circuitry internally provided to maintain a set bias level and hence a very constant input impedance and an extremely low reverse transfer coefficient. The cascode configuration also has the gain of two cascaded stages in a single package. The output stage of the oscillator assembly is designed with a level of gain compression

to maintain constant output power over the temperature range of the fixed platform.

#### 3.1.1.3 Regulator

The devices in the oscillator-buffer-regulator assembly must be biased in the most stable self-bias configuration so that the supply voltage variations do not effect the frequency of oscillation. An integrated circuit voltage regulator is used in lieu of a zener diode because of the improved ripple rejection ratio and DC stability. An IC regulator also has a shorter warmup period because a lower current flows through the internal reference element. The IC voltage regulator yields the additional advantage of short circuit and overvoltage protection.

#### 3.1.2 Multiplier Modulator

## 3.1.2.1 Multipliers

The multiplier-modulator subassembly, shown in Figure 3-4, consists of six functional units: the multipliers, the premodulator linear amplifier, the phase-modulator driver, the C+ control, the postmodulator linear amplifiers, and the modulator driver.

The multipliers increase the frequency of the signal produced by the oscillator by a factor of eight. To minimize the total number of stages in the transmitter, each stage in the multipliers

Figure 3-4. Multiplier-Modulator

must be designed for maximum power gain while maintaining absolute stability.

Harmonic rejection can be achieved by designing bandpass filters between the multipliers, at the expense of increased complexity and insertion loss. An alternate approach to suppressing the harmonics is to design narrowband matching networks between the multiplier sections and thus reject undesirable frequencies. The interstage matching thus becomes a tradeoff between power gain, harmonic rejection, and complexity (cost).

The multiplier chain must also be designed so that it does not degradate the carrier-to-noise ratio, and hence, the shortterm (one-half-second) stability of the oscillator carrier. Maintaining the carrier-to-noise ratio, the short-term stability below 1 part in  $10^9$ , for a one-half-second integration period, must be a prime consideration in the design of every stage in the amplifier. The multiplication process itself amplifies the noise of the frequency-modulated correlated noise component of the input oscillator signal. An "ideal" noiseless multiplier decreases the carrier-tonoise ratio by 20 log n (dB), where n is the frequency multiplication factor<sup>1</sup>.

Power Stabilization of Microwave and Millimeter Wave Sources; Louis C. Cuccia, James Coogan; Microwave, February 1970.

Additional phase-modulated noise is generated when the amplitude-modulated noise of the oscillator is converted to phase modulation by phase shifting of the amplitude modulation side-bands in the multiplier sections. Thermal noise is contributed by the devices and components in the multiplier circuits. A well-designed multiplier chain minimizes contributions of all but the noise due to multiplication.

The two practical circuit configurations for the multiplier stages are common-base and common-emitter. For the same device, common-base will provide higher frequencies of operation, but since the input is in phase with the output, stabilizing a common-base stage is more difficult. A common-base stage will have greater power gain only if series-resonant idlers are provided for the intended harmonic and all the subharmonics generated. In comparison, a common-emitter needs an idler for only the harmonic frequency desired. The increased power gain obtainable from idler circuits and the increased alignment time they add must be compared against the cost of a corresponding amount of amplifier gain later in the circuit. Common-emitter multipliers are utilized in the DCP to minimize the number of tuning adjustments and overall component cost.

## 3.1.2.2 Premodulator Linear Amplifier

The premodulator amplifier is a common-emitter linear amplifier that provides power gain of the signal at the final output frequency. This stage must also provide harmonic rejection since it follows the harmonically rich multiplier section.

For the modulator following this section to maintain the phase shift of 170 degrees (±5 degrees), it is required that the source and load impedances presented to the modulator remain constant. This is the main reason for using linear amplifiers before and after the modulator. Some compression of the signal from the multiplier is desirable to limit the amplitude excursions inherent in the Class C multipliers.

3.1.2.3 Phase Modulator and Driver

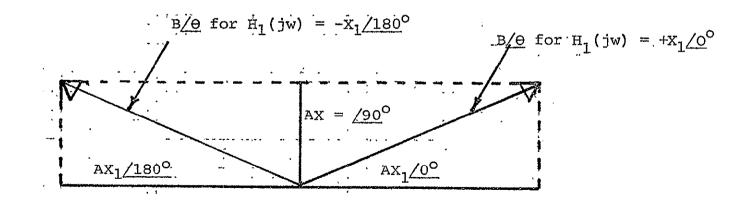

The phase modulator must develop two equal amplitude phase states for the signal that are electrically 170 degrees (±5 degrees) apart from each other. The modulator must be able to be operated at a maximum rate of 1600 symbols per second and present no source or load impedance during the switching period that causes any instability in the amplifiers preceding or following the modulator. The operation of the modulator is shown in Figure 3-5.

The driver circuitry for the phase modulator must drive the phase modulator at a maximum of 1600 symbols per second. The

Figure 3-5. Phase Modulator

digital data from the digital section of the DCP is carried to the transmitter as a balanced pair to provide noise immunity. The design of the balanced input circuitry of the phase modulator driver must take into consideration the fact that the pull-down current in the C-MOS drivers is much greater than the source current.

#### 3.1.2.4 Postmodulator Linear Amplifier

The postmodulator linear amplifiers are a series of commonemitter linear amplifiers that provide power gain for the signal at the final output frequency. This chain of linear amplifiers are designed to have sufficient bandwidth so that no tuning adjustments are required. The common-emitter configuration is utilized because of the inherent stability available in this configuration.

The input impedance of the amplifier chain is designed to be stable so as to keep the phase shift produced by the modulator at 170 degrees (<u>+</u>5 degrees) over all operating conditions. The output impedance of this chain must be designed to transfer maximum power into the RF amplifier subassembly while maintaining absolute stability at all frequencies.

## 3.1.2.5 C+ Control

The C+ control section of the multiplier-modulator assembly

provides switching between the prime power, A+, and the Class A circuits of the multiplier-modulator subassembly and the RF amplifier subassembly. This switching section prevents the Class A stages from dissipating power until control signals from the digital section signal the start of a transmission period. The design of this circuitry must take into account that the pull-down capability of the C-MOS is greater than the source current capability.

3.1.3 RF Amplifier

#### 3.1.3.1 Linear Amplifier

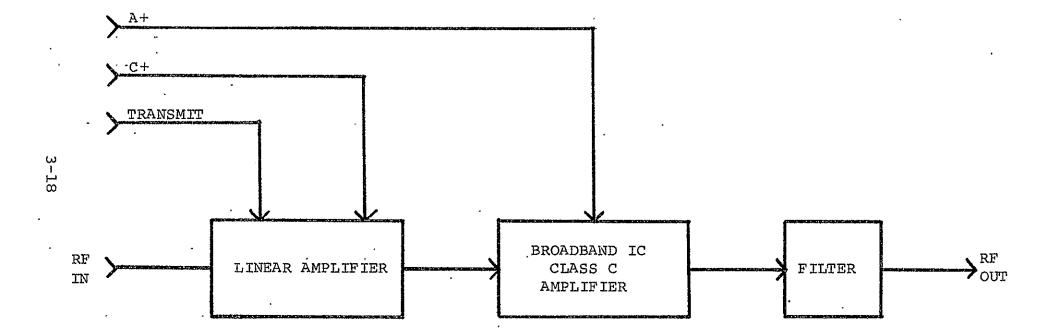

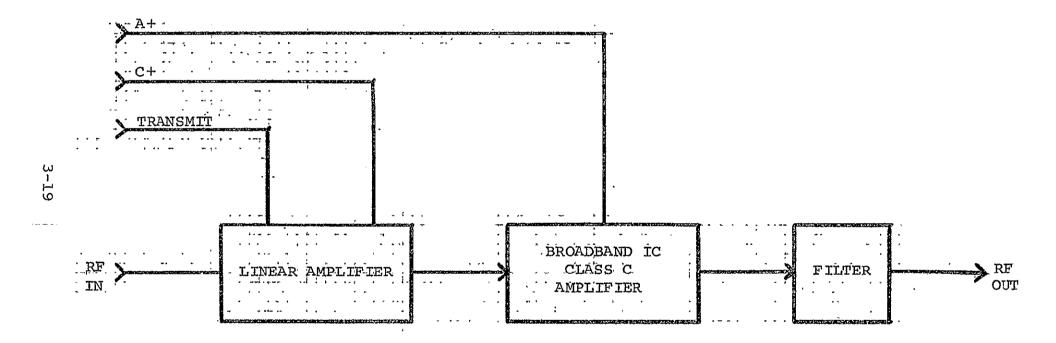

The RF amplifier subassembly (see Figure 3-6) in the mobile version of the DCP consists of a linear amplifier, followed by a broadband microelectronic Class C IC amplifier with a low-pass filter. The fixed version differs from the mobile unit (Figure 3-7) in that the IC amplifier and associated component values are rated for a higher power of five watts.

The linear amplifier utilized in the mobile and fixed versions provides power gain. This amplifier must be designed to remain stable during bi-phase modulation of the carrier. This corresponds to remaining stable under pulsed conditions because, as the phase of the carrier is switched, the amplitude of the carrier during the switching period becomes in excess of 30 dB below the amplitude of the carrier in either phase state. The linear amplifier also

Figure 3-6. RF Amplifier, Mobile

Figure 3-7. RF Amplifier, Fixed

functions as an RF switch and inhibits operation of the Class C amplifier when the base driver is removed. It must also be designed so that the bias can be controlled by the digital logic.

## 3.1.3.2 Broadband Power Module

A TRW broadband Class C integrated circuit (IC) is utilized to provide the large signal gain in the final output stage. It is not necessary that the IC be unconditionally stable, only that it be stable at all levels of drive within the range of source and load impedances presented by the linear-driving circuitry and the output filter, respectively.

The broadband, Class C, integrated circuit of the fixed platform differs from the mobile platform in that increased power output is required by the former. An IC with a correspondingly larger output power rating is used in place of the IC needed in the mobile platform. This approach maximizes the commonality between the mobile and fixed platforms.

3.1.3.3 Output Filter

The output filter is a three-element, T section, low-pass filter. This filter provides 18 dB/octave attenuation to the harmonics generated in the final amplifier. This filter not only provides the suppression specified but also demonstrates that a low-pass filter

of this form is compatible with the TRW output module. This indicates that additional harmonic rejection could be obtained simply by adding more elements to the filter without introducing any new considerations with regard to output stability.

#### 3.2 <u>DETAILED DESCRIPTION</u>

### 3.2.1 Circuit Operation

### 3.2.1.1 Oscillator-Buffer-Regulator

The block diagrams of the transmitter section of the DCP's are shown in Figures 3-2, 3-3, 3-4, 3-5, and 3-6. The interwiring diagram of the transmitter assembly is shown in Figure 3-9. The circuit diagram of the oscillator-buffer is shown in Figure 3-10. Figure 3-11 is the circuit diagram of the multiplier-modulator subassembly. Figures 3-12 and 3-13 are the circuit diagrams of the RF amplifier mobile unit and the RF amplifier fixed unit.

The B+ line, as shown in Figure 3-2, carries power from the control circuitry on the multiplier-modulator subassembly to the oscillator-buffer subassembly. In the mobile DCP, this line can always be energized or energized only during the warmup and transmission period. The length of the warmup period can be varied from 1.56 seconds to 24.9 seconds in the mobile platform.

In the fixed form of the Data Collection Platform, the B+ line is energized during the transmission period and for a warmup period before the transmission period. The warmup period can be varied from 0.156 seconds to 2.496 seconds by moving a jumper wire on the multiplier-modulator subassembly. The longer the warmup period, the less warmup drift the oscillator will exhibit.

The voltage regulator limits the B+ to the DC level needed by the oscillator and the buffer amplifier. It also provides transient suppression of the AC components of the B+. The regulator is designed to provide short circuit and over voltage protection. The oscillator section is protected in this fashion because of the considerable time required to align the oscillator loop. Significant changes of device parameters in the oscillator loop would result from a voltage overload of even a very short duration. The cost of protection is much less than that of realigning the oscillator loop. The short circuit capability also protects the voltage regulator itself from a failure of a device or component within the oscillator buffer subassembly or from an unintentional grounding of the DC line during initial testing or troubleshooting.

The crystal oscillator loop of the oscillator-buffer-regulator subassembly is shown in Figure 3-3. The crystal is characterized at a given frequency and drive level as having an insertion gain

of  $\beta$  and a phase shift of  $\Theta_B$  degrees. The series resonant frequency of the crystal in the mobile platform is 50.3875 MHz and the frequency of the fixed platform is 50.2625 MHz. The amplifier block shown in Figure 3-3 consists of a bipolar amplifier and a fet amplifier-limiter. The amplifier is characterized with respect to frequency and drive level as having an insertion gain of  $\alpha$  and a phase shift of  $\Theta_A$  degrees at the operating level.

The conditions for series oscillation are that the sum of the phase shifts of the amplifier and the resonator is an integer multiple of 360 degrees and the gain of the amplifiers be greater than or equal to the loss of the resonator. It is also required that the oscillation criteria be met by the oscillator loop only at the intended frequency. Tuning adjustments are provided to adjust the phase shift and the level of the crystal oscillator. When the phase shift of the amplifier is adjusted to zero degrees, the crystal will oscillate at the series resonant frequency. A variable temperature coefficient capacitor is provided within the oscillator loop to adjust the overall temperature coefficient of the amplifier. By this means the frequency-temperature coefficient of the oscillator can be changed without changing parts in the circuit.

A portion of the signal within the oscillator loop is sampled and amplified by the buffer-amplifier. The buffer is a cascode circuit that amplifies the oscillator signal to the level required by the multiplier circuits. Any change in input impedance of the buffer-amplifier will affect the phase shift in the oscillator loop, and hence the frequency of oscillation. The reverse transfer characteristics of the buffer-amplifier reflects changes in the load impedance to the input circuit. Since the input impedance of a transistor is related to the collector current, changes in bias will cause changes in the input impedance.

To minimize changes of these effects, a cascode RF/IF amplifier with constant current biasing is used as the buffer-amplifier. The internal constant current source maintains a constant bias, and the cascode configuration has an extremely low reverse feedback term. A tuning element is provided on the output of the cascode buffer-amplifier to adjust the output loading.

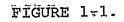

### 3.2.1.1.1 Frequency Stability Tests

Figure 1-2 of Appendix A is a block diagram of the test setup for measuring short-term stability. The oscillator under test is frequency mixed with the output of a Hewlett-Packard standard oscillator (Model 106B). The standard oscillator has a short-term stability of 1.5 parts in  $10^{11}$  for sample periods as short as 0.1

second. The signal out of the mixer is then passed through a lowpass amplifier/filter which rejects the sum frequency and other harmonics from the mixer and passes the difference frequency to the counter. The period of successive 0.5 second count intervals are then recorded on the digital printer. The short-term stability is calculated as an average over one hundred of the 0.5 second count intervals.

The test setup for the 15 minute stability test is the same as that used in the short-term stability test and the same basic principles apply. The output of the amplifier/filter was recorded (to the nearest 0.1 Hz) every 10 seconds. This data taken over a 15 minute interval was used to compute the drift rate.

Typical data of a 15 minute sector taken from a 15 hour stability measurement are shown in Figure 3-8. In order to record tenths of a hertz the two most significant digits have been displaced and therefore are not shown in the print out. For example, Figure 3-8 has as the first reading 99999798 which in reality is 399,999,979.8 Hz; this reading is 0.2 Hz higher than the next frequency measurement. There are a total of 90 samples, each are separated by 10 seconds (total of 15 minutes). The standard deviation is used to compute the statistical inference of frequency stability from the 90 samples. The standard deviation, s, is then

| с      | o      | С          | 0      | 9      | 9      | 9        | . 9    | 7      | 7      | 4       |   |   | ~ | ~ | ~ | _      | ~      | ~      | ~      | -      | 9       | ~          |   |

|--------|--------|------------|--------|--------|--------|----------|--------|--------|--------|---------|---|---|---|---|---|--------|--------|--------|--------|--------|---------|------------|---|

| 0      | ō      | 0          | 9      |        |        |          |        |        |        | •       |   |   | 0 | 0 | 9 | 9      | 9      | 9<br>9 | อ<br>១ | 7      | 9<br>9  | ย<br>6     |   |

| 0      | 0      | 0          | 9      |        |        |          |        |        |        |         |   | 0 | 0 | 0 | 9 | 9<br>9 | 9      | 9      | 9<br>9 | 7      | ย       | 6          | - |

| ŏ      | 0      | 0          |        | .9     |        |          |        | -      |        |         |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 7      | 9       | 5          |   |

| _      | ō ō    |            | 9      |        | ้อ     |          |        |        |        |         |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 7      | 9       | 4.         |   |

|        | ō      |            | 9      |        |        |          |        | - 8    |        |         |   | õ | 0 | õ | 9 | 9      | 9      | 9      | 9      | 7      | 9       | 7          |   |

| ō      | ō      | 0          | 9      | - 9    | 9      |          |        |        |        | - 8     |   | 0 | õ | ŏ | 9 | 9      | 9      | 9      | อ      | 7      | ้อ      | 4          |   |

| 0      | 0      | 0          | 9      | 9      | 9      | 9        | 9      | 8      | o      | 2       |   | 0 | 0 | 0 | 9 | ๑      | 9      | 9      | 9      | 7      | 8       | 8          |   |

| o      | 0      | 0          | 9      | 9      | 9      | 9        | 9      | 8      | 0      | 2       |   | 0 | 0 | 0 | 9 | 9      | ้อ     | 9      | 9      | 7      | 8       | 4          |   |

| 0      | 0      | <b>.</b> 0 | 9      | 9      | 9      | 9        | 9      | 8      | ·0     | ٥       |   | ō | 0 | 0 |   | -9     | 9      | 9      | 9      | 7      | 9       | c          |   |

| o      | 0      | 0          | 9      | 9      | 9      | ๑        | ໑      | 7      | 9      | 8       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | ງ      | 7      | 9       | 4          |   |

| 0      | 0,     | 0          | 9      | 9      | 9      | 9        | 9      | 8      | о      | 0       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 7      | а,      | 9          |   |

| o      | 0      | o          | ໑      | S      | 9      | 9        | Э      | 8      | 0      | 3       |   | 0 | o | o | 9 | ອ      | 9      | 9      | 9      | 7      | 8       | Ð          |   |

| 0      | о      | 0          | 9      | 9      | 9      | 9        | 9      | 9      | 0      | 4       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 7      | 8       | s          |   |

| ò      | 0      | 0          | 9      | 9      | 9      | 9        | 9      | c      | 0      | ł       |   | 0 | 0 | o | 9 | 9      | 9      | э      | 9      | 7      | ŋ       | 9.         |   |

| 0      | ò      | o          | 9      | ១      | 9      | 9        | 9      | 8      | ŋ      | 3       |   | 0 | 0 | 0 | 9 | э      | Э      | .9     | e      | 7      | э ́     | 3          |   |

| o      | 0      | 0          | 9      | c      | 9      | 9        | 9      | 8      | 0      | 2       |   | 0 | 0 | o | 9 | 9      | 9      | э      | 8      | 7      | 9       | 4          |   |

| Q      | 0      | 0          | 9      | â      | 9      | 9        | С      | з      | С      | 2       |   | 0 | 0 | o | ອ | 9      | 9      | 9      | 9      | 3      | 0       | 4          |   |

| 0      | 0      | o          | 9      | 9      | 9      | 9        | 9      | 7      | Э      | 7       |   | 0 | 0 | 0 | с | ŝ      | อ      | 9      | 9      | 8      | 0-      | 3          |   |

| 0      | ٥      | 0          | 9      | Э      | 9      | 9        | Э      | 8      | 0      | 0       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 8      | 0       | 5          |   |

| 0      | 0      | 0          | ອ      | 9      | ?      | 9        | 9      | 7      | 9      | 7       | : | 0 | 0 | 0 | 9 | 9      | 9      | 9      | າ      | 31     | 0       | 3          |   |

| 0      | 0      | 0          | 9      | 9      | 9      | Э        | С      | 8      | c      | 1       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | С      | 8      | 0       | 0          |   |

| 0      | 0      | 0          | 9      | 9      | 9      | 9        | 9      | 8      | o      | 0       |   | 0 | 0 | 0 | Ð | э      | 9      | 9      | S      | 3      | 0       | 2          |   |

| 0      | 0      | 0          | ŋ      | 9      | ອ      | 9        | 9      | 7      | 9      | 5       |   | 0 | 0 | 0 | ອ | 9      | 9      | Э      | 2      | 7      | ອ       | 7          |   |

| Ō.     | 0      | 0          | 9      | Э      | 9      | 9        | 9      | 7      | 9      | 0       |   | Ö | 0 | 0 | 9 | 9      | 9      | 9      | 9      | 7      | 8       | 9          |   |

| 0      | 0      | 0          | 9      | 9      | э      | Э        | 9      | 7      | 8      | 5       |   | 0 | 0 | ٥ | 9 | ១      | 9      | з      | 9      | 7      | э       | 1          |   |

| 0      |        | 0          | Э      | S      | 9      | ?        | 9      | 7      | 8      | 6       |   | 0 | 0 | 0 | 9 | 9      | 9      | 9      | Э      | 7      | 7       | 2          |   |

| 0      | 0      | 0          | 0      | c      | 2      | c        | 9      | 7      | 5      | 5       |   | 0 | 0 | 0 | ອ | 9      | 9      | 9      | ອ      | 7      | 7       | 3          |   |

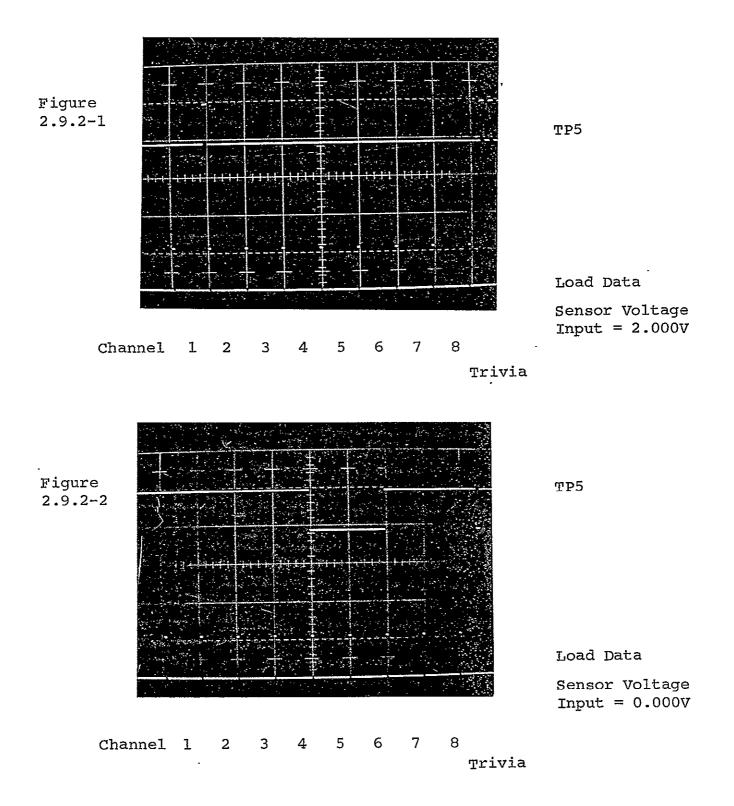

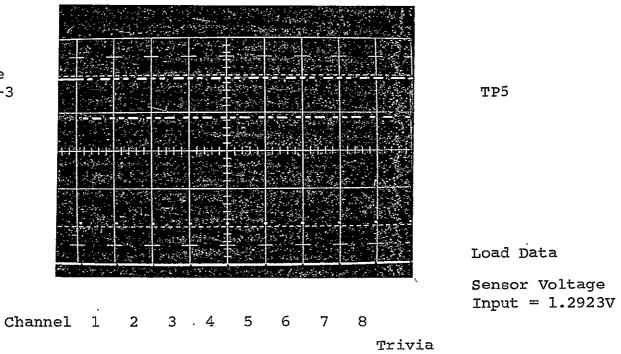

| 0      | 0      | 0          | 0      | Э      | 9      | 9        | Э      | 7      | 8      | 9       |   | 0 | 0 | 0 | 9 | 9      | э      | 9      | 3      | 7      | G       | 6          |   |