# Advanced Router Architectures

Axel K. Kloth

Boca Raton London New York

A CRC title, part of the Taylor & Francis imprint, a member of the Taylor & Francis Group, the academic division of T&F Informa plc.

Published in 2006 by CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2006 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-10: 0-8493-3550-7 (Hardcover) International Standard Book Number-13: 978-0-8493-3550-1 (Hardcover) Library of Congress Card Number 2005052895

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

No part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC) 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

Trademark Notice: Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

#### Library of Congress Cataloging-in-Publication Data

Kloth, Axel K.

Advanced router architectures / Axel K. Kloth.

p. cm.

Includes bibliographical references and index.

ISBN 0-8493-3550-7 (alk. paper)

1. Routers (Computer networks) 2. Computer network architectures. I. Title.

TK5105.543.K57 2006 004.6--dc22

2005052895

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### Preface

The Internet has become a part of our daily lives. Routers, switches and transmission equipment make up the backbone of the Internet—yet many users and even data communications and telecommunications service technicians do not understand how these nodes really work.

This book addresses everyone who is generally interested in advanced router architectures, and in particular, how the components of advanced routers work together and how they are integrated with each other. It also explains the background behind why these building blocks perform certain functions, and how the function is implemented in general.

It does not replace the wide variety of very good books that exist today and address each of the items in much more depth, but lack the "glue" to fit them all together. While this book tries to tie it all together, it does not go into particular depths in any of the chapters. This is intended to be an introduction that triggers a deeper interest towards the subject matter and hopefully leads to a more in-depth interest by the reader. While this book aims at a general understanding of the issues, it is not intended to provide a register- or bit-level discussion of functions. An indepth analysis of the enqueuing and dequeuing algorithms in a traffic manager can be found in books that specialize on schedulers for traffic management. This book explains why traffic management may be important in certain applications, what the traffic manager does, and how it connects to the rest of the router. It also explains what some implications are of the introduction or omission of a traffic manager into an advanced router, but it will not provide guidance as to what the memory sizes, the latency or the word lengths should be. The same is true for any other subject, be it switch fabrics, network processors on the line cards, or framers and MACs on the port cards; this book presents an overview of the functions, why they are performed, and how in general they are implemented. It does not discuss the issue of the optimum scheduler, the ultimate fairness in scheduling, or the frame format of T3/E3/J3. This can be found elsewhere, either in the ITU-T standards or in the many good books describing these formats.

This book, however, will in general explain which mandatory and which optional building blocks can be found in an advanced router, and how these building blocks work in conjunction to ensure that the Internet works in the way we have come to expect it.

### The Author

**Axel Kloth** is the founder and CTO of Parimics, Inc., a fabless semiconductor manufacturer focused on chipset architectures for image analysis. Axel has more than 12 years of experience in high performance computing, networking, and low latency switching as well as experience in architecting and implementing large chips. He has authored or coauthored multiple patents. Prior to Parimics, he worked for Siemens' Public Networks Group and Siemens Microelectronics — later Infineon Technologies — and HotRail and subsequently Conexant and Mindspeed Technologies.

Additionally, he has written several books and technical articles, covering basic technologies and applications and deployments of these. Axel was on the technical advisory boards of HotRail, Z-Force, and Zedix. Axel finished his post-graduate studies in physics and information technologies at CAU Kiel in Germany. His diploma thesis covered what has become the basic technology in Xenon (HID) headlights, and short pulse as well as high energy laser physics. High performance computing, especially MPP SIMD architectures, combined with the low latency switching and interconnect knowledge, contributed to the unique technology behind Parimics' chipset.

### Table of Contents

| Chapter | <b>1</b> Introduction 1                            | l |

|---------|----------------------------------------------------|---|

|         | Conclusion                                         | 5 |

|         |                                                    |   |

| Chapter | 2 Internet Topology Change                         | 7 |

|         | Overview                                           | 7 |

|         | Current Status                                     | 1 |

|         | Traffic and Traffic Growth10                       | ) |

|         | Conclusion                                         | 1 |

| Chapter | <b>3</b> The Carrier Business Model                | 5 |

| Chapter |                                                    |   |

|         | Overview                                           |   |

|         | Service Level Agreements (SLAs)                    |   |

|         | The VoIP Business Model                            | 3 |

|         | Internal Corporate Accounting                      | ) |

|         | Conclusion                                         | ) |

| Chapter | 4 Advanced Routers in                              |   |

| •       | Central Office Applications                        | l |

|         | Overview                                           | l |

|         | Central Office (CO) Colocation                     |   |

|         | Conclusion                                         |   |

|         |                                                    |   |

| Chapter | <b>5</b> Function Split                            | 7 |

|         | Overview                                           | 7 |

|         | Traditional System Partitioning and Function Split | ) |

|         | Functions within the Port Card                     |   |

|         | Functions within the Processor Card                |   |

|         | Functions within the Switch Card                   |   |

|         | Functions within the OAM&P Card                    |   |

|         | Conclusion                                         |   |

|         |                                                    |   |

| Chapter 6 High Availability                       |            |

|---------------------------------------------------|------------|

| Overview                                          |            |

| Definition                                        |            |

| Implications                                      |            |

| Network View of Redundancy and Failsafe Operation |            |

| Example                                           |            |

| Design Life Time and Single Point of              |            |

| Failure Impact                                    |            |

| Definition of Availability                        |            |

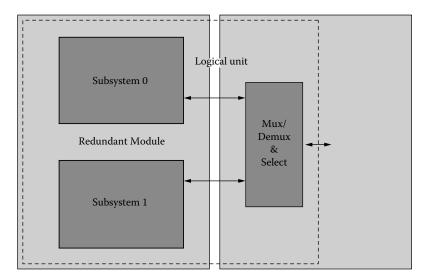

| 1+1 Redundancy                                    |            |

| 1:1 Redundancy                                    |            |

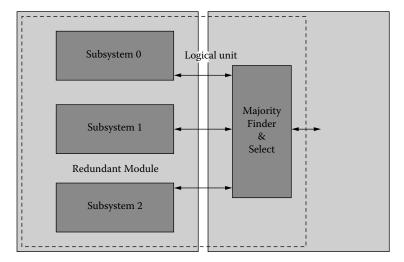

| 2 out of 3 (or N out of N+1) Redundancy           |            |

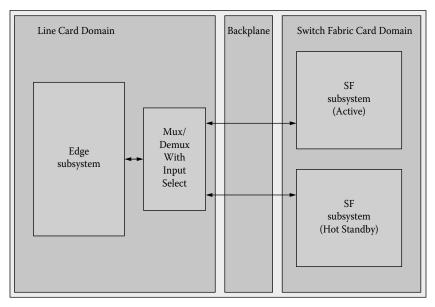

| Redundant Switch Fabric Cards                     |            |

| Redundant Line Cards.                             |            |

| Redundant Links                                   |            |

| Redundant Power Supplies                          |            |

| Software Robustness                               |            |

| OAM&P Control over Redundant Subsystems           |            |

| Timed Switchover                                  |            |

| Switchover on Demand.                             |            |

| Reducing Human Error Probability                  |            |

| Conclusion                                        |            |

|                                                   |            |

| Chapter 7 The Chassis                             |            |

| Overview                                          |            |

| Single-board versus Modular Designs               |            |

| Modular Designs                                   |            |

| Power Supply Considerations                       |            |

| Single-board Designs.                             |            |

| Midplane Designs                                  |            |

| The Card Cage                                     |            |

| Power Supply Unit.                                |            |

| Fan Trays                                         |            |

| Backplane Designs                                 |            |

| The Card Cage                                     |            |

| Power Supply Unit                                 |            |

| Fan Trays                                         |            |

| Conclusion                                        |            |

|                                                   |            |

| Chapter 8 Line Cards                              |            |

| Overview                                          | <b>Q</b> 1 |

| Line Card Functions in IPv6 Routers               |            |

| Definitions                                       |            |

| Definition of a Line Card                         |            |

|                                                   |            |

|         | Definition of a Port Card                                         | 87    |

|---------|-------------------------------------------------------------------|-------|

|         | Definition of a Processor Card                                    | 87    |

|         | Functional Requirements                                           | 88    |

|         | Data Loss and Higher Layers                                       |       |

|         | Distribution of Traffic                                           |       |

|         | Traffic Manager Functions versus Queue                            |       |

|         | Manager Functions                                                 | 110   |

|         | Ingress-side Traffic Management                                   |       |

|         | Further Impact of Advanced Router Architectures                   |       |

|         | Line Cards as Server NICs                                         |       |

|         | Scalability                                                       | 117   |

|         | Differentiation of Functions                                      |       |

|         | Line Card Implementation in Single-board Designs                  |       |

|         | Line Card Implementation in Midplane Designs                      |       |

|         | Line Card Implementation in Backplane Designs                     |       |

|         | Line Card Messaging and Communications                            |       |

|         | Internal Line Card to Line Card Communication                     |       |

|         | Internal Line Card to Switch Fabric Communication                 |       |

|         | Line Card to Switch Fabric Queue Manager Communication            |       |

|         | Line Card to External Resources Communication                     |       |

|         | Interior and Exterior Border Gateway Protocols                    | 125   |

|         | Line Card Functions for PSTN Internetworking                      |       |

|         | Port Card Functions                                               |       |

|         | Definitions                                                       | 127   |

|         | Network Processor and Traffic Manager Software Implications       | 127   |

|         | Local Control Processors for Line or Processor Cards              |       |

|         | Compute Efficiency                                                | 129   |

|         | Conclusion                                                        | . 130 |

|         |                                                                   |       |

| Chapter | • 9 Switch Fabric Cards                                           | 133   |

| Chapter |                                                                   |       |

|         | Overview                                                          | 133   |

|         | Functional Requirements for an                                    |       |

|         | Advanced Router's Core                                            |       |

|         | History of Router-internal Interconnects                          |       |

|         | Basics                                                            |       |

|         | Externally Controlled Switches                                    |       |

|         | The Scheduling Challenge                                          |       |

|         | Crosspoint Switches and Crossbar Switches                         |       |

|         | Self-routing Switches                                             |       |

|         | LCI                                                               |       |

|         | Shared Memory Switches                                            |       |

|         | Non-buffered, Non-queued Switch Fabrics                           |       |

|         | Buffered and Queued Switch Fabrics                                |       |

|         | Combined Virtually Output Queued (CVOQ) Switch Fabrics $\ldots$ . |       |

|         | Cleaner and Easier Logical and Functional Partitioning            | 144   |

|         | Easier Routing of Traces on the Backplane                    | 145 |

|---------|--------------------------------------------------------------|-----|

|         | Higher Throughput of the Switch Fabric                       | 145 |

|         | Less Incremental Cost for Upgrades                           | 146 |

|         | Metrics of Switch Fabrics                                    |     |

|         | Net Bit Rate or Link Rate Utilization (Minimum,              |     |

|         | Maximum, Average)                                            | 147 |

|         | Throughput (Total and on a per-Link Basis)                   |     |

|         | System Availability (Minimum)                                |     |

|         | System Uptime (Minimum)                                      |     |

|         | Reliability (Error Rate)                                     |     |

|         | Logical Connection Setup Time (Minimum,                      |     |

|         | Maximum, Average)                                            | 151 |

|         | Logical Connection Teardown Time (Minimum,                   |     |

|         | Maximum, Average)                                            | 151 |

|         | Delay and Latency                                            |     |

|         | Round-Trip Delay (Minimum, Maximum, Average)                 |     |

|         | Cell Delay Variation (CDV) (Minimum, Maximum, Average)       |     |

|         | Scalability                                                  |     |

|         | Field Upgradability                                          |     |

|         | Resource Utilization on the Network Processor                |     |

|         | Cost Structure                                               |     |

|         | Feasibility                                                  |     |

|         |                                                              |     |

|         | Performance Extension                                        |     |

|         | Blocking Multi-stage Switches                                |     |

|         | Non-blocking Multi-stage Switches                            |     |

|         | Bit Slicing                                                  |     |

|         | Cell Slicing                                                 |     |

|         | Load Sharing across N Planes                                 | 160 |

|         | Master/Slave or "Performance Extension                       |     |

|         | Architectures"                                               |     |

|         | Alternative Solutions                                        |     |

|         | "Pay-as-you-grow Solutions"                                  |     |

|         | The "Switchless Switch"                                      |     |

|         | Multicast and Broadcast                                      |     |

|         | Bandwidth Overprovisioning                                   | 168 |

|         | Traffic Manager Functions versus Queue Manager Functions     | 169 |

|         | Switch Fabric Queue Manager                                  | 169 |

|         | Deterministic Behavior                                       | 170 |

|         | Switch Fabric I/O                                            | 170 |

|         | Software Function Set in Local Switch Fabric Control         | 172 |

|         | Conclusion                                                   | 175 |

|         |                                                              |     |

| Chapter | • 10 Operation, Administration, Maintenance and Provisioning | 177 |

| Juapter | To operation, Auministration, Maintenance and Flovisioning   | 1// |

|         | Overview                                                     |     |

|         | Definition of OAM&P                                          | 178 |

|         |                                                              |     |

| Functions of the OAM&P entity            | 179 |

|------------------------------------------|-----|

| Operational Statuses                     | 181 |

| Status Transitions                       | 182 |

| Example 1 for Status Transitions         | 182 |

| Example 2 for Status Transitions         | 183 |

| Relationship with NMC                    | 183 |

| Implementation                           |     |

| Fail-safe and Fault-tolerant OAM&P       |     |

| Entity Operation                         | 185 |

| OAM&P Entity Internal Communication      | 185 |

| Software Implications                    | 186 |

| Encryption for NMC-to-OAM&P Traffic      | 189 |

| Examples of Failure Modes of             |     |

| Managed Entities                         | 190 |

| The Necessity for the Device-Global View | 192 |

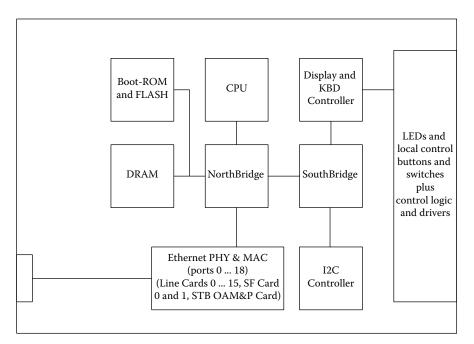

| Sample OAM&P Card Schematic              | 193 |

| Conclusion                               | 194 |

| Glossary                                 | 195 |

| References                               | 213 |

### 1 Introduction

The basic Internet Protocol version 4 (IPv4) router described in RFC1812 has performed well so far, and survived much longer than its estimated lifetime. The initial drafts of the Internet assumed a maximum of around 20,000 nodes, and it was never intended to exceed that number. The basic premise for the Internet was to survive a massive nuclear attack, and therefore the topology of the Internet was planned to be a mesh of nodes. All of these nodes were intended to be separate and independent, serving only a few users each. Cost of operation and cost per bit transmitted were not an issue, because the Department of Defense (DoD) ran it.

Then the Internet was opened to government agencies, to schools and universities, and finally to the public. Internet Service Providers (ISPs) offered access to the Internet, and the various users generated increasing amounts of traffic. This was becoming too expensive to be operated by the DoD, and therefore it was privatized. All of a sudden, the rules changed. The Internet was subject to the basic logic of demand and supply, to economic requirements. It needed to provide revenue and generate enough profit by itself to run and upgrade the network.

The Internet therefore has changed dramatically, and so have its requirements. Not only are there more nodes, servers, and clients, but more importantly, the Internet has become an integral part of data communications. It now is used to run even mission-critical applications across it. Customers have grown used to it, and now all of a sudden they request Service Level Agreements (SLAs). These SLAs define a minimum System Uptime, Accessibility, Availability, and guaranteed throughput in terms of bits per second and maximum latency for certain traffic classes that may or may not be associated with certain customers or customer groups. While in the beginning only the US and Europe participated in the Internet, now China and India have joined the ranks. This larger number of simultaneous users calls for sustained address uniqueness, therefore requiring a larger address space. This has led the architects of the Internet to rethink a few items, and the outcome was Internet Protocol next generation (IPng), later renamed to Internet Protocol version 6 (IPv6).

To make it perfectly clear, based on the assumptions the architects made for the Internet, there was nothing wrong with the Internet. Based on that, the first routers were built using current and obsolete computers; there was nothing wrong with that approach, either. All devices fulfilled what they were intended to do. Since the very first routers used the telephony network (Plain Old Telephony Services, POTS) as a backbone and for the access to the data network, their data rates and throughput were limited by the capabilities of the modems to which they were connected. The first modems did not deliver more than 1200 bit/s unidirectional. Therefore, the routers had to deal with a maximum throughput of 150 byte/s; they were clearly neither input/output (I/O)- nor compute-bound. That changed over time since increasing processing of packets was required. Encapsulation, translation, routing, and access control became part of the feature set, and later information was added about routing tables and their mutual updates. All these features required more compute power, but since they were internal, they seemed not to impact the router itself. That was and is not entirely true. In spite of limited processing power in the first Central Processing Units (CPUs), the very first routers were I/O bound; whereas the later generations of routers became compute-bound because of the growth of the number of protocols that had to be supported, and because of a very limited increase in line rates-due to the fact that the Time Division Multiplex (TDM)-based backbone of communications was only capable of supporting DS0 and T1/E1 line rates. Routers always have had a line-specific logic part, an adaptation layer between the line-specific logic and the core, higher layer processing and routing code, some switching logic in the core, and a generic control unit for administration. These functions can be implemented and built separately and then integrated into a chassis, or they can be integrated into a single board. They can be implemented in hardware, in software, or in a mixture of both. More so, the new generation of IPv4 routers was built to the then-current expectations and requirements. The newer routers were built around a bus or a simple crosspoint switch with a centralized arbiter to interconnect the line cards, and had a very basic Operation, Administration, Maintenance and Provisioning (OAM&P) software running somewhere in the centralized Operating System (OS). These routers were either single board ("Pizza Box") or modular designs housed in a chassis with either a backplane or a midplane.

However, since the Internet and its use has changed so dramatically, the old IPv4 routers just do not fulfill the requirements any more—even if they were architected today. This book will explain what changed, what the impact on the router's internal architecture is, and what needs to be changed to overcome that problem. Since the prerequisites have changed, the new generation of routers for IPv6 must be different from the old routers.

A huge change has started to take place already. While in the beginning the Internet used the Public Switched Telephony Network (PSTN) Tele Communications (TelCo) infrastructure, now the TelCo industry has started to use the Internet infrastructure as a backbone. This change is fundamental. In the early days, Class 5 Central Office (CO) switches were the concentrators for end users with dial-up ports and modems, and they connected to a hierarchy of Class 4 CO switches through T1/E1 or higher multiplexed digital hierarchies (Plesiochronous Digital Hierarchy, PDH). In fact, the Class 4 switches were the backbone of the Internet. Now the Internet is the backbone for the TelCo industry, the carriers, the Regional Bell Operating Companies (RBOCs) and Competitive Local Exchange Carriers (CLECs), and the datacom industry. It is the core of the integrated, unified, and converged network. The Class 5 CO switches are not the concentrators any more-they have to provide Digital Susbscriber Line (DSL) ports for high-bandwidth users, and the DSL ports are not routed to the Class 5 switch core anymore. They are physically and logically separated and connected to Asynchronous Transfer Mode (ATM) switches or Digital Subscriber Line Access Multiplexers (DSLAMs). Both the PDH uplinks from the Class 5 switch and the DSLAM ports now connect to carrier-grade routers instead of Class 4 CO switches.

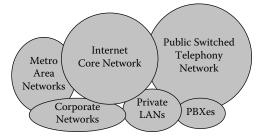

Current IPv4 routers deal with IPv4 packets. An IPv4 packet is a datagram of variable length between 40 byte long for Packet over SONET (PoS) and 1518 byte long; for the so-called jumbo frames it may even be 9018 bytes long. Additionally, the line rates are not very high in typical IPv4 routers. Most IPv4 routers top out at 1 Gigabit per second (Gbit/s) per port. Achieving a port throughput of 1 Gbit/s is not too complicated today, neither on the line card, nor within the switch. If additionally averaging the size of the packet, and not considering the worst-case scenario can limit the packet rate, then it is fairly simple. Assuming the average packet size exceeds 1000 bit (125 byte), then the router's ports will have to deal with one million packets per second. If one lookup per packet must be performed because the destination IP address can directly be mapped to an egress port, then the port card must perform one million lookups per second. Content Addressable Memory (CAMs) that achieve these lookup speeds are readily available and cheap. However, current routers are not optimized to deal with different traffic types that may have different real-time requirements or limits of the latency or delay variation. That leaves us with the necessity of modern, advanced routers, even if ATM switching may be the underlying technology in the network or the router itself. With GbE and 10GbE over "dark fiber" catching up, some of the ATM and Synchronous Digital Hierarchy and Synchronous Optical Network (SDH/SONET) infrastructure in the Access and the Metropolitan Area Network (MAN) rings may become obsolete, but in the Wide Area Network (WAN), SDH/SONET will continue to dominate the transport infrastructure, on top of Dense Wavelength Division Multiplex (DWDM) or other technologies to increase the throughput though and over individual fibers. I assume DWDM is not the end of the effort to squeeze in more transport capacity. I assume Quad Phase Shift Keying (QPSK) or Quaternary or Quadrature Amplitude Modulation (QAM) or additional new technologies will come up there. More importantly, these transport infrastructures will change in a way that allows the provider of these services to set up connections fast-basically on demand. Now that raw bandwidth is rather cheap, the most important issue the backbone and service providers face is to provision these fat pipes. Assume there will be a signal-either directly originating from the customer or from the customer to the Network Management Server (NMS) in the Network Management Center (NMC) and then into the providing nodes-to set up connections as needed. Add-Drop-Multiplexers (ADMs) will have to be able to understand that kind of signaling. That will impact routers and ATM switches as well. While the RBOCs and CLECs will be able to make use of this new, cheaper infrastructure in the backbone, cell phone providers especially will benefit from a conversion of the backbone based on Class 4 CO switches into a packet-based network backbone. The cell phone providers' signaling traffic (from roaming and other metadata provided for the cell phone infrastructure) desperately needs an infrastructure that is more cost-effective than the current one (see Figure 1.1)

The cell phone network currently is a portion of the PSTN, but the transition that the cell phone network undergoes—with EDGE and General Packet Radio Service (GPRS), and with 3G—is so tremendous that it will be using the Internet Core Network as a backbone even before the long-distance providers will adopt that same transition.

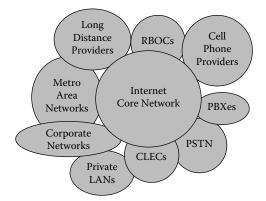

As a result, routers deployed in the core network today will have to be able to transport PSTN and cell phone traffic tomorrow. Extending existing networks with the same equipment used years ago, therefore, is not good enough. The new situation will look much closer to Figure 1.2.

In short, we can say that the Internet was fine the way it was first conceived and implemented. The requirements changed with more users and different traffic types. Privatization of the Internet core led to another set of new requirements. With the carriers taking over again and a consolidation of carriers and ISPs, a convergence of the separate networks towards one unified network was inevitable. The necessity to make a profit off the Internet and all related and connected networks added the necessity to be able to bill for services depending on their Service Level Agreement (SLA). This had a profound impact on routers, ATM switches, and all other networking gear. The most fundamental impact was on the router design criteria, since best-effort approaches were replaced by SLA guarantees, and the lack of policing and billing was replaced by per-connection policing and billing. Internetworking with other networks was ignored before, and in the future advanced routers will have to be able to interconnect and communicate with all networks in existence

FIGURE 1.1 Current network interconnects.

FIGURE 1.2 Future network interconnects.

today. The more protocols are supported by advanced routers or their gateways, the broader the deployment range of these routers and gateways.

#### CONCLUSION

As a summary, we can safely say that the Internet—as originally described, conceived and implemented—performed its function perfectly. The growing number of users and the requirement to carry different traffic types led to the privatization of the Internet, which in turn meant that it had to be made profitable. With the carriers initially only taking over parts of the backbone of the Internet, and with consolidation in the industry, convergence became a requirement of the operators of the Internet, not only for the users. The impact on routers, ATM switches, and all other networking gear was tremendous. As a result, the design criteria for routers have changed significantly. As a side note, it is important to stress that the need for interconnectivity has reached servers; blade servers now incorporate router blades.

We can conclude that a modern router will have to seamlessly and reliably do the following:

- · Losslessly switch and route datagrams

- Be able to perform Segmentation And Reassembly (SAR)

- Perform policing at line speed for thousands of virtual connections simultaneously and thereby enforce and support SLAs

- Perform Traffic Management by queuing and buffering traffic according to SLAs, and drop excess traffic

- Support Traffic Engineering by means of collecting Statistic Traffic Data

- Support a mixture of hierarchical and mesh interconnect infrastructure in terms of data traffic

- · Support an overlay network for metadata and signaling data

- Enable traffic rerouting at the edge and provide redundant fail-safe systems towards the core

- · Communicate securely within the components of the router

- Communicate securely between the OAM&P card and a Billing Center

- Communicate securely between the OAM&P card and a PKI Center for authentication

- Communicate securely between the OAM&P card and a Network Management Center

- Communicate with the PSTN infrastructure

This will enable the Internet to continue to grow, and the nodes to scale near-linearly.

The components and their interactions determine the routers' deployment range, and price range. We will see in this book which components of a router impact the desired functions.

Specifically, the components and the interaction between the components of a router can be understood as a complex system that, by itself, can perform a wide variety of datapath functions, but must be seen as part of a larger system—the network itself.

The chapters are arranged such that they follow the train of thought as to why the requirements for routers changed, and what had to be done to make them compliant with current necessities. They are ordered as follows:

- Internet Topology Change

- The Carrier Business Model

- Advanced Routers in Central Office Applications

- Function Split

- High Availability (HA)

- The Chassis

- Line Card Functions

- Switch Fabrics

- Operation, Administration, Maintenance and Provisioning (OAM&P)

- Glossary

- Literature

## 2 Internet Topology Change

#### **OVERVIEW**

When the Internet was conceived—then as the ARPAnet—it was intentionally set up to support a mesh interconnect infrastructure with a very flat hierarchy. This was very advantageous for what it was intended to do: survive the outage of a significant number of nodes in case of a nuclear attack. As a result, everything was set up to be "self-routing," and a centralized NMC was not only undesirable, it was unwanted. A centralized Network Management Center (NMC) for signaling and call and transmittal routing would have made ARPAnet vulnerable even if the router network were distributed. Therefore, even if the transport network had been able to transmit datagrams, an outage of the centralized NMC would have rendered useless the transport network's distributed nature and its virtual invulnerability.

As a result, ARPAnet—and consequentially the Internet—has no centralized NMC. However, one has to take into account that ARPAnet was designed to support a maximum of about 20,000 nodes. The architects of ARPAnet never took into consideration such a growth in numbers of nodes, and it is a testament to the genius of the Internet's inventors that it still works. While some of the original design flaws have been fixed, the Internet as of today still does not have a structure that can guarantee fulfillment of future requirements of Internet users. Today, the Internet is a mixture of a mesh and a partially hierarchical structure. In effect, the path of any given packet cannot be predicted. As a result, cell or packet delay variation cannot be predicted, either.

#### CURRENT STATUS

One of the many implications of the Internet's growth was its conversion from a mesh to a mixture between a mesh and a hierarchical architecture with super-nodes. Although not many people want to hear this, everyone involved in network topologies has to acknowledge that the Internet evolved into an architecture that is very similar to the "old" telephony architecture of the PSTN. For cost reasons, the full mesh was abandoned. The mesh is too expensive for large numbers of users and nodes, and it requires routers with very large numbers of interfaces. A router with large numbers of interfaces and rather low throughput on each of these interfaces is expensive to maintain and requires large routing tables. On top of that, it will require a lot of signaling information to continuously update its routing tables. Therefore, a significant portion of the available bandwidth will be consumed for signaling information and network internal data. This problem is only going to get worse, since the number of interconnects N—logical or physical—goes with  $N^*(N-1)/2$ , and therefore is an  $N^2$  problem. No network operator can afford an  $N^2$  communications protocol on a

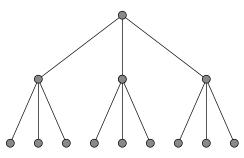

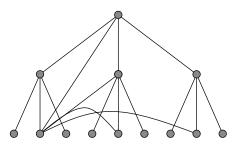

large number of users or nodes, and therefore the Internet topology had to evolve into a hierarchical structure (see Figure 2.1) with super-nodes. This is not bad news, but it has profound implications of routers or nodes.

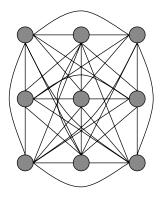

While the full mesh very apparently has no overhead in the network and no layers of switches to forward data from the source to the destination, we can see that each node has a large number of interconnects that must be served (see Figure 2.2). This must be done within the node. The number of interconnects is a function of the number of nodes.

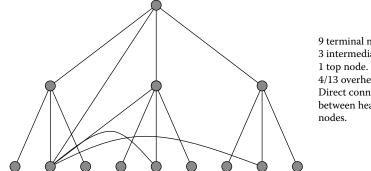

The hierarchical topology requires the highest number of non-terminal device nodes. However, it also offers the lowest number of interconnects on each terminal device. This makes the terminal devices easy to manage and operate. The number of non-terminal device nodes can be reduced by increasing the degree of concentration on each node. Full mesh topology has the lowest number of non-terminal nodes, but all devices have a large number of interconnects they must serve. The hierarchical topology with a partial mesh overlay is a compromise (see Figure 2.3). In that topology, there are fewer ports per terminal device than in the full mesh scenario, and fewer interconnects to serve, but there are still hierarchical paths and direct interconnects between nodes and high-traffic node terminal devices. As a result, these nodes and terminal devices are manageable but reduce the need for a hierarchy of all traffic to the directly interconnected devices.

9 terminal nodes, 3 intermediate nodes, 1 top node. Result is 4/13 overhead.

FIGURE 2.1 Hierarchical network with three layers.

FIGURE 2.2 Nine-node full mesh.

8

9 terminal nodes, 3 intermediate nodes, 1 top node. Result is 4/13 overhead. Direct connections between heavy traffic

FIGURE 2.3 Hierarchical network with partial mesh overlay.

Reliability, availability, and serviceability suddenly become important for the routers and the Domain Name Service (DNS) servers to resolve names to IP addresses. Since virtual connections are now set up, tunnels are set up, bandwidth assigned and reserved with the setup and rerouting on a per-packet basis is not feasible anymore. The routers themselves must be built such that they have redundancy provisions. Whereas in the early days of the Internet, every packet could find its way from the source to the destination on a hop-by-hop basis and every packet could indeed take a different path, this is not true any more. With "Quality of Service" (QoS) requirements for the Service Level Agreements (SLAs), latency and delay must be not only closely monitored, they must be controlled and maintained. Rerouting a packet therefore is not a solution anymore, and the entire path to which a transmittal of data has been assigned must be maintained for its duration. This means that the routers must provide redundancy.

This directly affects the line card with line-specific logic and the higher layer processing, as well as the switch fabric cards.

Additionally, Advanced Intelligent Network (AIN) services and Domain Name Service (DNS) lookup require a much more centralized IP signaling network than ever conceived before. The cost of running a DNS lookup engine or center and keeping it current is not negligible. Therefore, network nodes will grow bigger and bigger, and the DNS root servers will also grow in size and complexity. This means that more and more traffic will pass through a decreasing number of very heavily utilized nodes. These nodes will make the Internet increasingly vulnerable and be in absolute opposition to the original idea of the distributed and fail-safe Internet. In essence, the Internet will look like the Telephony Network today, with multiple layers of aggregation hierarchy, local switching and routing, and global switching and routing. DNS lookups will be very much similar to what today is the Intelligent Network (IN) or Advanced Intelligent Network (AIN) lookup in the Public Switched Telephony Network (PSTN) Plain Old Telephony Service (POTS) Time Division Multiplex (TDM) world for 800 numbers, as well as for number portability; Route Planning and Traffic Engineering will make the Internet look a lot more like today's POTS PSTN than the current Internet. We can see first indications of this in Internet2.

DoS and DDoS (Distributed Denial of Service) attacks will be more and more common, and therefore, all crucial network resources will require more and more protection. The Root DNS Servers will have to be faster, will enable more lookups per second, will require a protocol that is secure by means of authenticity verification and data integrity, and encrypt signaling metadata. The routers that communicate with these Root DNS Servers must be able to support this. Therefore, not only the OAM&P cards in future IPv6 routers will have to be able to communicate using the Public Key Infrastructure (PKI), but also Border Gateway Protocol (BGP), Exterior Gateway Protocol (EGP), Classless Inter-Domain Routing (CIDR), or Routing Information Protocol (RIP) might have to use it. They will have to do this within the network, and from the router towards the Root DNS Lookup Center. Messages, commands, and status information will be sent out-of-band as well as in-band, and Service Level Agreements will dominate not only the contracts between end users and carriers or ISPs, they will be prevalent in inter-carrier and inter-ISP contracts. Because of these and because of unification of traffic carried through the backbones, SLAs and QoS will become commonplace.

#### TRAFFIC AND TRAFFIC GROWTH

The Internet has grown quite dramatically since its inception. Although the predicted traffic growth numbers presented by Vint Cerf never really materialized, the growth of the Internet and the traffic that traverses the Internet on a daily basis is tremendous. Just to put a few throughput numbers into perspective, if every person living in the US is using the Internet via a modem and consumes the available baudrate of 56 Kbits/s, then the grand total bandwidth consumption for all of the US is 300M \* 56 Kbps =  $16.8 \times 10^{12}$  bit/s, or around 17 Tbit/s. To up the numbers slightly, I will assume that every person is using the Internet via ADSL and consumes the available downlink baudrate of 1500 Kbit/s, then the grand total bandwidth for all of the US is 300M \* 1500 Kbps =  $450 \times 10^{12}$  bit/s, or 450 Tbit/s. Even if everyone is online all the time via Symmetric High Speed DSL (G.SHDSL) with symmetric 44 Mbit/s, then the total bandwidth consumption is only 300M \* 44000 Kbit/s =  $13.2 \times 10^{15}$  bit/s, or 13.2 Pbit/s.

Realistically, if the service penetration is lower than 100%, and not everyone is using the Internet, and even if they are, they do not use it 24 hours a day. As a result, we have to significantly decrease the upper limit for expected traffic. If service penetration is 10%, and 1% of the time of the day is spent using the Internet, then we have to take 1/1000 of the numbers we calculated above to get a realistic current traffic upper limit.

As a result, we can assume the upper limit of the bandwidth consumption to be in the range of 10–15 Tbit/s during the highest load period of the day for all of the US. In 1985, a few hundred thousand Kbytes were transferred per day, with peak consumption of a few Mbit/s. Therefore, we can assume that over the last 20 years, traffic increased by a factor of about one million. This is roughly equivalent to doubling the traffic each year over a period of 20 years. Doubling the traffic annually means a Compound Annual Growth Rate (CAGR) of 100%. No technology has withstood a prolonged period of time of hypergrowth. The basic IPv4 router described was intended to route traffic at speeds between modem lines (then 1200 bit/s), and 10Base2 (10 Mbit/s Carrier Sense Media Access with Collision Detection (CSMA/CD)) at maximum. For the most part, even servers could not load a 10 Mbit/s line, and therefore the requirements were not yet able to sustain a line rate at minimum packet size. The requirement was to support it somewhat, to the best of its abilities—best effort. This is not an option in a 16- or 32-port 10 Gbit/s per port core IPv6 router anymore. As a result, the implementations of the new architectures can be expected to differ significantly.

No matter how good the original design was, after 20 consecutive years of consistent doubling of traffic, the infrastructure of the Internet must be different from how it began.

These numbers are consistent with the starting numbers and the growth rates that MCI published after their "irregularities" were removed, and have roughly been confirmed by Sprint and other carriers that operate data network backbones or the central nodes MAE West and East.

Even if we assume a different distribution of data consumption, and mix services and service requirements as shown in the table below, the total consumption of bandwidth is significantly lower than many experts had anticipated. Even if High Quality or High Definition Television (HDTV) is added to the mix, the total required bandwidth is in the range of 4 Terabit/s for all of the US combined. With routing inefficiencies of a factor of 10—which accounts for signaling and, more importantly, for hierarchical traffic—the required bandwidth grows to 40 Terabit/s. Even if only routers with an aggregate throughput of 1 Gigabit/s were considered, then 4,000 of those would fulfill the needs. (See Table 2.1.)

Additional bandwidth-consuming services will be emerging very soon, and occupy dramatic bandwidth throughout the network. Fleet management in railways

| Traffic Volume Estimate (in bit/s) |                      |             |                 |                   |

|------------------------------------|----------------------|-------------|-----------------|-------------------|

| Traffic Type                       | Bandwidth (in bit/s) | Penetration | Usage (sec/day) | Total Data Volume |

| POTS                               | 9600                 | 0.90        | 3600            | 9.331E+15         |

| Cell phone                         | 9600                 | 0.50        | 3600            | 5.184E+15         |

| PC & modem                         | 56000                | 0.50        | 3600            | 3.024E+16         |

| PC & ADSL modem                    | 1500000              | 0.15        | 3600            | 2.430E+17         |

| MP3 or similar                     | 10000                | 0.10        | 3600            | 1.080E+15         |

| MPEG or JPEG                       | 200000               | 0.05        | 3600            | 1.080E+16         |

| HQ video                           | 1000000              | 0.01        | 3600            | 1.080E+16         |

| Total data volume                  | 3.104E+17            |             |                 |                   |

| Bandwidth required                 | 3.593E+12            |             |                 |                   |

| Total U.S. residents               | 300,000,000          |             |                 |                   |

| TABLE 2.1         |         |           |              |

|-------------------|---------|-----------|--------------|

| Hypothetical Tota | al U.S. | Bandwidth | Requirements |

11

and trucking companies will very soon rely upon Global Positioning System (GPS), and all the feedback, route info, directions, and map updates will be sent throughout the network, go into Mobile Switching Centers (MSCs), and from there into the cars, trucks, and other vehicles. This may happen using GSM/PCS (Global System for Mobile Communication/Personal Communication Service), but it could also take place using Generalized Packet Radio Service (GPRS), Universal Mobile Telecommunications System (UMTS), Wireless Application Protocol (WAP) and High-Speed Circuit-Switched Data (HSCSD) or other new upcoming technology. Independent of the particular implementation, it will not only occupy bandwidth, but will be of a certain structure. It will have associated signaling like Q.931/E.164, it will use small packets or will be cell based, and it may carry IP traffic. Nevertheless, it will send much more signaling information than current technologies, and it will ubiquitous. Other wireless applications include, but are not limited to, Bluetooth, 802.11a/b/g, Digital Enhanced Cordless Telecommunications (DECT), HyperLAN II, and HomeRF, with upcoming home networking applications like Home Phoneline Networking Alliance (HomePNA)-all with their own inherent signaling and messaging mechanism, and all of them requiring a virtual overlay network for signaling and messaging. Additionally, once these devices are wired, they will be accessed from everywhere, especially from abroad. Roaming information, together with the data to be transferred, will accumulate into quite a large portion of total traffic.

Cell phone usage will continue to increase, but probably not at the rate predicted in previous years. The cell phones will become smarter, and the networks will become smarter in order to provide the user more intelligent services. Experts assume that the traffic generated by cell phone users grows faster than expected, despite the fact that fewer new subscribers than projected will be using wireless services. What is important to mention here is the fact that, especially in the Scandinavian countries, micropayment methods with cell phones have gained quite a bit of ground. People try not to carry cash around any more, and credit card purchases for small payments do not make sense because the administrative effort and therefore the cost for that is too high. Therefore, micropayments are carried out using a cell phone, and the amount due is billed to the phone bill. This increases the amount of cell phone usage with very short messages, close to Short Message Service (SMS) usage. Any new infrastructure in the network must be able to efficiently route and switch these messages at an appropriate granularity.

Additionally, there will be increasingly intelligent gadgets using the cell phone infrastructure, but which are not cell phones. Automotive anti-theft systems and cars equipped with systems—those that automatically dial emergency numbers such as 911 if the car's electronic systems detect a deceleration exceeding a certain threshold, typically indicating a severe accident, and other systems to locate and triangulate those cars—will generate additional traffic.

Some other trends may also contribute to additional traffic on the network. Experts envision that the open network will be used more and more for business and mission-critical transactions, and therefore authenticity and security will become more and more of an issue. This induces the need for trust centers, which in turn will have to authenticate users and validate keys. This requires reliable and high-priority links into the trust centers, to be used for each secured transaction.

This generates additional traffic, but in contrast to other traffic, is extremely important and vital to the users. This will replace Virtual Private Networks (VPNs) entirely. B2B and B2C will be unthinkable in the future without trusted communication over the open Internet. Trust centers will be a crucial part of it, and they will generate a significant amount of high-quality traffic.

In addition to these, the increasing number of Top Level Domains (TLDs) and generic Top Level Domains (gTLDs) as well as hosts at all will lead to a much higher rate at which address resolution requests cannot be fulfilled locally and therefore must be resolved at a very few central places—much like the Intelligent Network with the 800 numbers. This will lead to additional traffic for address and name resolution services, and may open up a completely new market. Search engines with better address resolution capabilities and RealNames equivalent services will help the user find information, but at the expense of a lot of lookups in the Net: short and timing-critical messages to be exchanged everywhere.

Because of integration, unification and convergence requirements for both the carriers and the data service providers such as ISPs, the Internet is already undergoing dramatic changes. While in the beginning the Internet used the PSTN TelCo infrastructure, the TelCo industry has started to use the Internet infrastructure as a backbone.

This is a very fundamental change, and the change is apparent in the backbone and in the access area. In the early days, Class 5 Central Office (CO) switches were the concentrators for end users with dial-up ports and modems. Class 5 CO switches now provide DSL ports for high-bandwidth users, but the DSL ports are not routed to the Class 5 switch core anymore. Instead, they are physically and logically separated and connected to ATM switches or Digital Subscriber Access Line Multiplexers (DSLAMs). The DSLAM ports now connect to carrier-grade routers instead of Class 4 CO switches. In the backbone, the change is equally dramatic. The Class 5 CO switches were connected to a hierarchy of Class 4 CO switches through T1/E1 or higher multiplexed digital hierarchies (Plesiochronus Digital Hierarchy, PDH). In fact, the Class 5 switches now connect to carrier-grade routers instead of Class 4 CO switches, and as a result, the Internet is the backbone for the TelCo industry, the carriers, the RBOCs and CLECs, and the datacom industry. It is the core of the integrated, unified, and converged network.

The unified network in the backbone and in the access area will force all providers—the carriers, the RBOCs and CLECs, and the datacom industry such as the ISPs—to focus more on International Telecommunications Union—Telephony Section (ITU-T) standards for reliability, availability, serviceability, and manageability, and therefore demand more from future routers. We can conclude that future IPv6 routers will have to meet the following requirements:

- · Losslessly switch and route datagrams

- Be able to perform Segmentation And Reassembly (SAR)

- Perform policing at line speed for thousands of virtual connections simultaneously and thereby enforce and support SLAs

- Perform Traffic Management by queuing and buffering traffic according to SLAs, and drop excess traffic

- Support Traffic Engineering by means of collecting Statistic Traffic Data

- Support a mixture of hierarchical and mesh interconnect infrastructure in terms of data traffic

- Support an overlay network for metadata and signaling data

- Enable traffic rerouting at the edge and provide redundant fail-safe systems towards the core

- Communicate securely within the components of the router

- Communicate securely between the OAM&P card and a Billing Center

- Communicate securely between the OAM&P card and a PKI Center for authentication

- Communicate securely between the OAM&P card and a Network Management Center (NMC)

- Communicate with the PSTN infrastructure.

In addition, they will have to do what the traditional IPv4 basic router always did and must do—route traffic efficiently. However, they must do it at dramatically higher speeds, with more line cards per router, and supporting more protocols simultaneously. This gives us another set of requirements that future advanced routers will have to fulfill.

#### CONCLUSION

The original architects of the Internet and subsequently the first architects of routers have done a tremendous job. They have created a basic architecture that has, so far, withstood the test of time and survived a 20-year run of annual doubling of traffic. The newest changes in the requirements from the view of network operators, carriers, ISPs and users will result in a new form of the Internet. IPv6 and QoS within Service Level Agreements will become predominant, and the Internet as we can envision it today will replace the PSTN backbone. As a result, the Internet and modern routers will have to support new requirements.

### 3 The Carrier Business Model

#### **OVERVIEW**

Data services—especially IP services—always held a promising future that has not yet come to economic fruition in the worlds of the carriers and ISPs. Neither has Voice over IP (VoIP) displaced Plain Old Telephony Services (POTS), nor have the ISPs and the data carriers had great financial success so far.

One of the many reasons IP services have not yet really taken off is the fact that the promoters of IP services ignored one important prerequisite, and that was and is that the Service Providers—carriers and ISPs—must make a profit. This requires a business model that includes billing, and billing requires demonstrable compliance with SLAs and Quality of Service (QoS) promises. Although the sheer volume and the associated cost of IP traffic suggest that every packet is free in terms of expenses, it really is not. The infrastructure must be in place, and it must be paid for; even IP traffic has to be billed somehow. Comparing this to "Good Old Telephony" the perpacket costs of data transmitted over an IP network indeed is cheaper than the "per timeslot" cost of each and every phone call. However, a survey within the peer groups of Telephony Service Providers showed that up to 80% of the voice call costs incurred are costs for billing. Nobody is sure whether these numbers still hold true, but this should teach the router manufacturers an important lesson: if the router does not support accounting for traffic and therefore billing, then the total cost of the transmission of any datagram may be lower; but since none of the traffic is billable, the service providers cannot afford to buy them since they cannot afford to deploy it. They must make money by billing. Flat-rate billing is unfair, unjustifiable, and probably does not hold its position in court. Why should a person or an organization that transmits 100 Mbyte of low-priority traffic per month pay the same flat fee as a person or an organization that makes use of much more bandwidth? While the infrastructure cost surely requires a basic fee for making services available, every bit counts (and must be paid for). High-priority traffic is more expensive, so a person or an organization that consumes 1 Gbyte of high-priority bandwidth occupies many more resources than the above-mentioned standard user. So, at least for internal billing purposes, per-priority billing and policing must be an option. As long as this is not the case, router manufacturers will not sell too many routers into TelCo and backbone data service providers.

Billing is only then a possible business suggestion if and when there are SLAs and a set of QoS parameters in place. In turn, this requires billing on a per-cell, per-packet, per-connection, or per-transaction basis. This requires the router to be capable of not only supporting full QoS and enforcing SLAs, but policing on a per-cell basis and sending this information to a billing center. This transmission must be sufficiently secure that it cannot be cracked or its integrity damaged by any reasonable means. Network Management and IP Billing solutions are necessary for IP Services to be a global success—and IPv6 is crucial. However, this will put additional stress and burdens on the router, since it now must be able to police every single packet. It must perform statistical traffic analysis and monitoring, and it must be able to monitor traffic on a per-user level; if that user has subscribed to multiple QoS levels, the router must track all paths, connections, transactions, and quotas for this user. It additionally must update usage tables, thresholds, billing information records, and all information pertaining thereto. After each transaction or after a preset time interval, the router will have to send this data to the billing center within the Network Management Center (NMC).

Today, the requirements are mostly determined by SLAs between the Service Provider and the customer. In ATM networks, there are multiple priority levels to allow a customer to choose the right combination of services for his demand and particular situation. Mission-critical data—like Session Announcement Protocol (SAP)—will not easily tolerate dropped packets, and therefore "best effort" might not be a good choice. Real-time requirements for video distribution can be fulfilled at a price. For NNTP, Simple Mail Transfer Protocol (SMPT), File Transfer Protocol (FTP), and TFTP, "best effort" is good enough. If VoIP is used, a TDM-equivalent clear channel might be useful. However, all these services must be billed differently. In turn, this requires that the router is capable of associating paths or transactions to a user, combining that with the QoS and the billing information on record, and then determining whether or not the user is within his or her quota. If so, everything can proceed, but if not, a notification to the billing center or the OAM&P center within the NMC must be sent and confirmed.

Very soon the CLECs, the RBOCs, and the long-distance telephone operators and providers will understand that the pure price pressure will force them to abandon their telephony Class 4 switches, and consolidate Time Division Multiplex (TDM) traffic originating and terminating in Class 5 switches into Gigabit- and Terabitswitched routers (GSRs and TSRs). Consequently these devices will have to be able to route and interpret ITU-T Common Channel Signaling System number 7 (CCS#7) messages. Even if Voice over IP (VoIP) will not penetrate the access quickly, it will be used in the backbone. The long-distance telephony traffic will ultimately share the bandwidth in the backbone with data. So there will be timing- and delay-variationsensitive phone traffic and timing-insensitive data traffic in the backbones; for cost and Operation, Administration, Maintenance and Provisioning (OAM&P) reasons, however, the Class 5 switches will remain for some time. While the impact on the long-distance providers and carriers is quite profound, the cell phone providers and carriers will feel the pressure even more. Not only have cell phones started to displace landlines, the pricing has come down to a level that is on par with the landline-at a higher level of capital expenditure than for wirebound phone services. In order to survive that crunch, cell phone providers and carriers must reduce their operating cost below that of a wireline phone provider. That is only possible for the cell phone operators if they effectively can transport the data and the signaling, including all metadata, for free. As a result, they must replace all Class 4 and Class 5 CO switches with a router-based network and maintain gateways to the PSTN and only keep their "air interface," the Mobile Switching Centers (MSCs).

A QoS-aware and SLA-capable network infrastructure must be in place to make IPv6—or any other advanced protocol, for that matter—a viable alternative to TDM backbones; therefore routers must support these functions in hardware and software for the anticipated number of simultaneous users.

#### SERVICE LEVEL AGREEMENTS (SLAS)

IPv6 itself is a quite dramatic technology change, but the technology change in the protocol is eclipsed by its implications. In fact, IPv6 brings the Internet Protocol and all services based upon it closer to ATM than most proponents want to admit. Since IPv6 is capable of unifying data and voice services—a promise that ATM made but never really fulfilled—both types of services will have to be supported by IPv6.

That is exactly what IPv6 is all about. IPv6 defines a Quality of Service field that ultimately can be used to implement all the traffic types that are in use today. Where ATM defined Constant Bit Rate (CBR), Variable Bit Rate/Real Time (VBR-RT), Variable Bit Rate/Non-Real Time (VBR-NRT), Available Bit Rate (ABR), and Unspecified Bit Rate (UBR), IPv6 defines 16 priorities that can be used to implement several different levels of QoS. However, IPv6 is not as sophisticated as ATM because it does not have to be. Where ATM defined all these parameters for the variance of the bit rate and the cell delay variation (CDV), IPv6 defines only levels of priority for QoS, and that is ultimately what the routers and their line cards and switch fabrics can understand and process. While it is nice to have CBR, VBR-RT and VBR-NRT available, it makes the design of a line card extremely complicated because arrival and departure of cells must be policed and monitored. It is computationally much more useful to reduce the complexity down to priorities with which cells are processed and forwarded from the ingress line card to the egress line card through the switch fabric. In effect, IPv6 provides the same or better throughput at the same or better compliance with prioritization as ATM, but it does not provide guarantees for real-time transmittals of data. There is no provision for measuring or influencing Cell Delay Variation (CDV) or packet delay variation in IPv6.

For all traffic types that are included in the SLA, important criteria and parameters for SLAs will include:

- Net bit rate (minimum, maximum, average)

- System availability (minimum)

- System uptime (minimum)

- Cell Delay Variation (minimum, maximum, average) (ATM networks only)

- Logical Connection setup time (minimum, maximum, average)

- Delay and latency (minimum, maximum, average)

- Round trip delay (minimum, maximum, average)

As a result of these SLAs, both the service provider and the customer will have to have equipment in place that can validate or verify compliance or noncompliance with the agreed-upon parameters. Another consequence is that the service providers will have to put equipment in place that has at least a chance of complying with the SLAs' parameters.

Therefore, router manufacturers must design a new generation of routers capable of fulfilling the above-mentioned requirements. In other words, the carrier requirements will have to be translated into requirements for the advanced router architectures.

#### THE VOIP BUSINESS MODEL

Independent of whether the carriers, long-distance providers, or the ISPs will start billing VoIP calls (including higher bandwidth video-telephony calls), there must be a mechanism in place to associate an SLA with a call or a similar customer transmittal. Billing of telephony and data services today is based on a general contractual framework. The call itself has implicit implications. The call does not establish a contract with an SLA or a QoS. In the future, the contract—including SLA and QoS—can be made or modified and agreed upon by the service provider and the customer prior to any call. A flat rate would be an alternative, but then there is no possibility of modifying the QoS parameters as required.

Today, based upon the contractual framework, every single call is carried by the provider, assuming the client agrees upon the conditions that are currently valid at that point of time. This implies uncertainty for both the customer and the service provider. While the customer has no proof for the beginning of, the length of, and the route taken by the call, the service provider has no assurance that the person who initiated the call was legally empowered to do so. This leads to the fact that the customer typically has no certainty about the cost of the call while the service provider has no certainty if and whether the invoice for the call might be disputed. The service provider may have deployed Least Cost Routing, but the customer has no direct benefit out of it. The customer therefore cannot adjust his habits to periods of time in which the service providers' resources are available, or at least when the likelihood of availability of delay-bound bandwidth is higher. On the other hand, the service provider has no impact on the habits of the customer, so overprovisioning of bandwidth is necessary. This leads to higher cost.

It therefore would be appropriate if the resources could be used in a more efficient way. This could be accomplished by providing for the service providers' network a resource manager that is capable of negotiating every single call over the network. The network in this definition can comprise of not only the telephony network, but also of any other resource capable of transporting, switching, routing, or bridging the requested traffic type in a mutually agreeable manner from the source to the destination—including provisions for buffering the traffic, delivering well-defined Classes and Qualities of Service, cell and packet loss probabilities, cell and packet delay variations, and cell and packet reordering.

If the service provider and the customer agree upon this scheme, then it is a natural implication to negotiate a contract for every single call and therefrom mutually determine the quality and the price. Since the resources have a certain value at any given (but variable) point of time—depending on network utilization and load status—the fees or charges cannot be constant. They might even change during the call or the data transfer. This implies something else: the framework in between the customer and the service provider covers only very basic responsibilities and duties, as well as the charges for these. Every single call or data transfer request establishes a new, explicit contract. The customer requests a certain connection for a given time or requests a certain bandwidth along a path with well-defined requirements. The resource manager figures out the actual value of this connection and routes it on the shortest, most cost-effective way or any available path from the source to the destination. The caller then has better control over his willingness to pay for premium quality or to save money by using spare bandwidth, or even to decide to postpone the call or data transfer; the provider has the opportunity to better load his valuable resources. There are no more implicit contracts, no fixed communications schemes, and no unnecessary blocking of valuable resources.

This is a much more demand-driven approach, an open market: it provides the freedom and the fair negotiation between a requester and a resource provider. Valuable resources rise in cost, while spare bandwidth and resources decline in cost. This generates a much smoother usage pattern, better overall network load and utilization, and therefore a higher return of investment for the provider, since its effort to extend the network is now reduced. However, this is only possible with a dedicated and sophisticated capability for policing, billing, traffic management and engineering, and OAM&P support.

#### INTERNAL CORPORATE ACCOUNTING

While billing for IP services by carriers or ISPs may not be immediately imminent, another topic is apparent today: internal accounting for services in corporations. Therefore, billing through the ISPs and carriers is not painting the entire picture. All Information Technology (IT) must increasingly justify its expenditures—and rightfully so. In all organizations that hold their IT department accountable, accountability is necessary, and it is crucial. All IT spending must be justified, and that is not easy today. While it is possible to say peak load of some routers may be 80% of their capacity, that does not say anything about usage and consumers of bandwidth. Today, at best, a Chief Information Officer (CIO) can claim that he assumes from some probes or statistical monitoring of the network that there is a certain distribution of bandwidth consumption. This is impossible to track over time or on a per-user, per-priority class. In other words, there is no clear technical justification for more bandwidth. What would it be like if the CIO could report to the Chief Financial Officer (CFO) that the internal network must be upgraded because engineering requires 34% of all traffic, with 60% of priority 4 traffic, 15% of priority 3 traffic, 15% of priority 2 traffic and 10% of priority 1 traffic; internal business reengineering through SAP consumes 33% of all traffic, with 5% of priority 4 traffic, 10% of priority 3 traffic, 30% of priority 2 traffic and 60% of priority 1 traffic; revenuegenerating orders from outside take 33% of all traffic, with 10% of priority 4 traffic, 5% of priority 3 traffic, 5% of priority 2 traffic and 80% of priority 1 traffic? That would be a perfect justification to order not only more routers to extend the capacity of the network, but also to adjust SAP traffic in its volume and priority.

This would allow for internal accounting of bandwidth usage, and would enable the cost of the infrastructure to be shared and distributed in a fair way—according to its consumption. This would remove the dark cloud over IT infrastructure investments, which today are seen as necessary. They are accounted for by a nontransparent account and seen as an expense for which justification cannot be obtained—other than the statement of the CIO saying "we need it to function."

As a result, the expense for the network infrastructure can now be billed directly towards the departments' accounts, instead of against a general corporate or company-wide "Network Infrastructure" account to which all departments contributed, independent of their usage profile. This may also curb at least some appetite for additional bandwidth, and it might also help pinpoint individual bandwidth hogs. The reason for that is the tendency to waste whatever is free, but be thoughtful of whatever has a cost associated with it.

#### CONCLUSION

Carriers and ISPs have offered data services quite successfully for a while. As it became increasingly obvious that the data network was perfectly capable of carrying even traffic that had some real-time requirements, this type of traffic increased. Ultimately, it showed that IPv4 and "best-effort" traffic routing could not deal with the complexities of real-time traffic and different priorities. As a result, IPv6 was called to duty for multiservice traffic to unify the carrier's backbones and access network and to carry the traffic that stems out of the PSTN backbone. While billing and policing were not in the original blueprint of the current data networks, these features can easily be supported and implemented by the next generation of smart routers. In order to fulfill the requirements of the new carriers, ISPs, corporate backbones, and the access networks, they will have to:

- · Losslessly switch and route datagrams

- Be able to perform Segmentation And Reassembly (SAR)

- Perform policing at line speed for thousands of virtual connections simultaneously and thereby enforce and support SLAs

- Perform Traffic Management by queuing and buffering traffic according to SLAs, and drop excess traffic

- Support Traffic Engineering by means of collecting Statistic Traffic Data

- Support a mixture of hierarchical and mesh interconnect infrastructure in terms of data traffic

- Support an overlay network for metadata and signaling data

- Enable traffic rerouting at the edge and provide redundant fail-safe systems towards the core

- · Communicate securely within the components of the router

- Communicate securely between the OAM&P card and a Billing Center

- Communicate securely between the OAM&P card and a PKI Center for authentication

- Communicate securely between the OAM&P card and a Network Management Center (NMC)

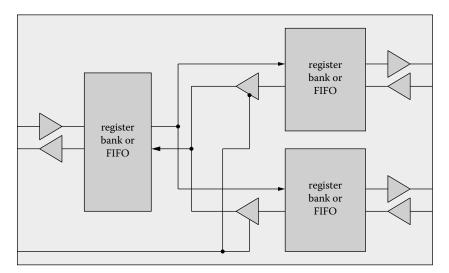

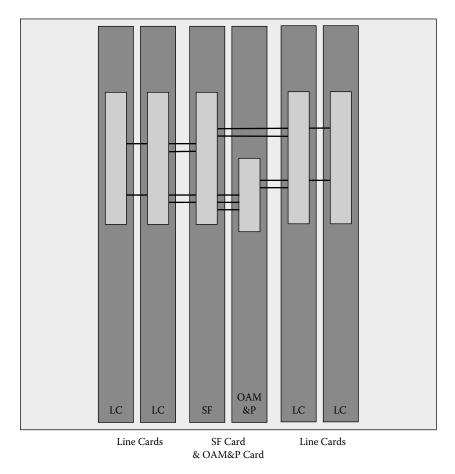

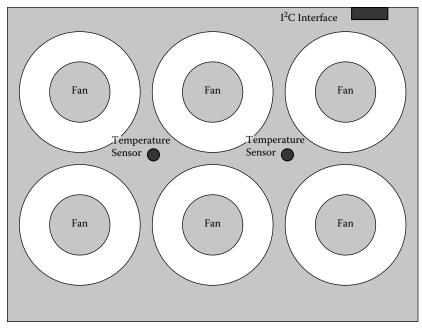

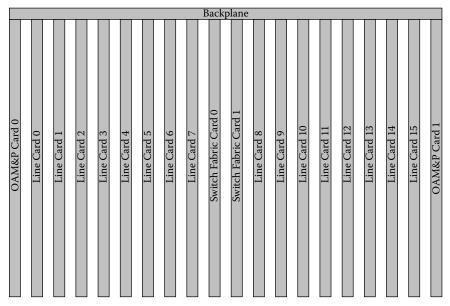

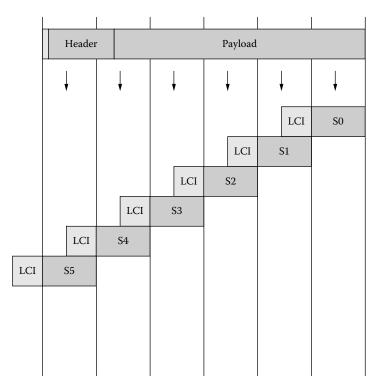

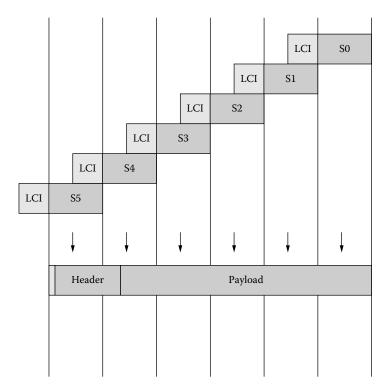

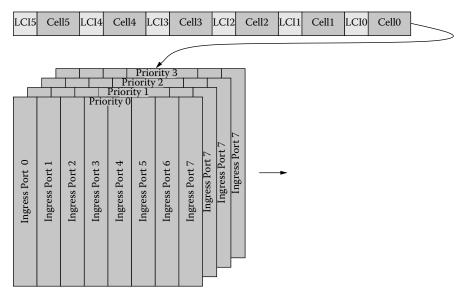

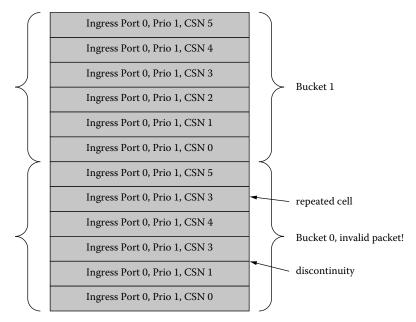

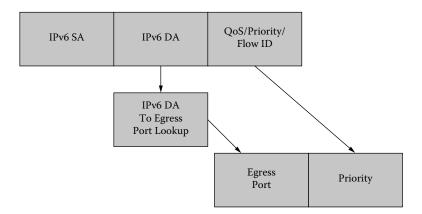

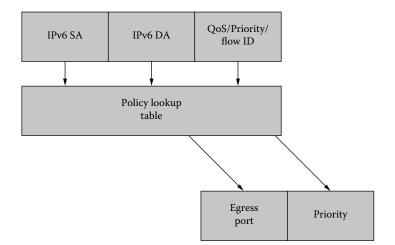

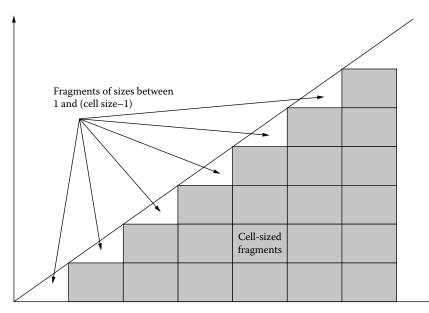

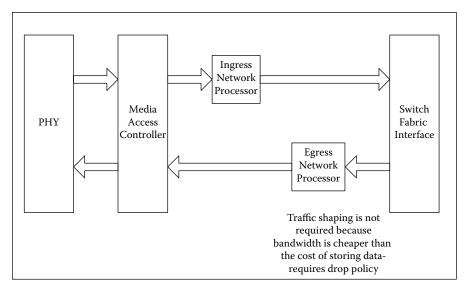

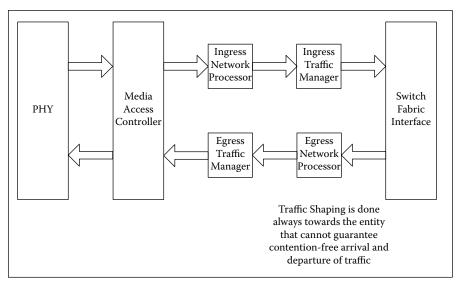

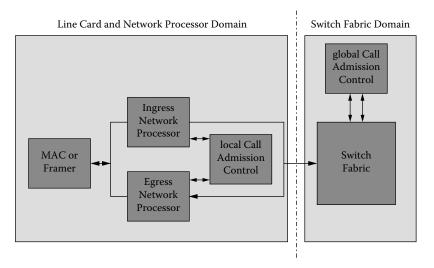

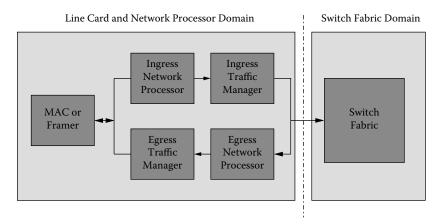

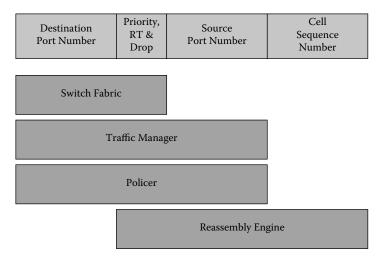

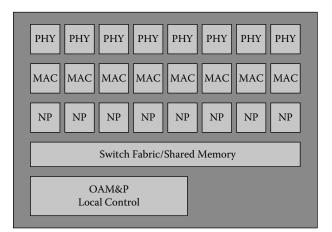

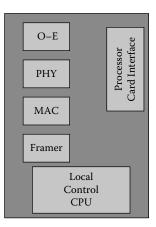

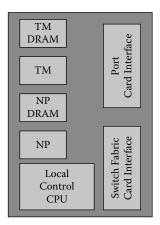

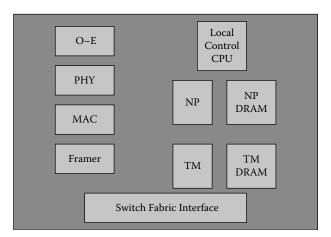

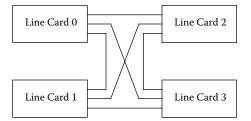

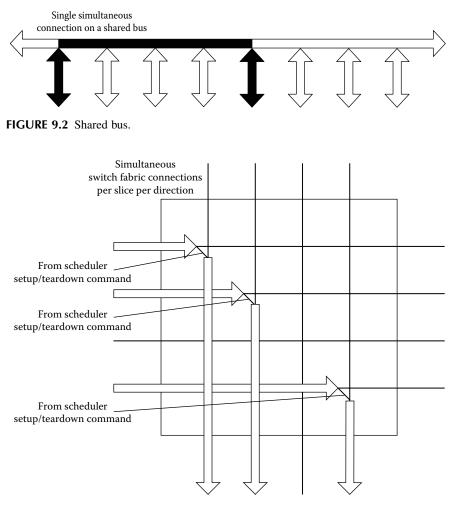

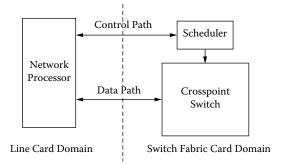

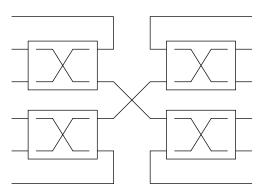

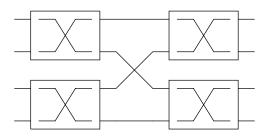

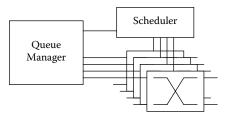

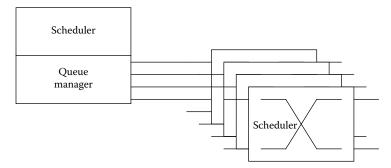

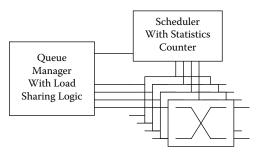

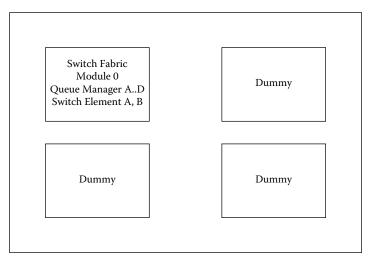

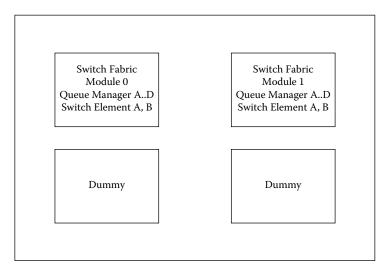

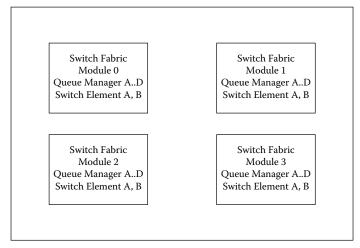

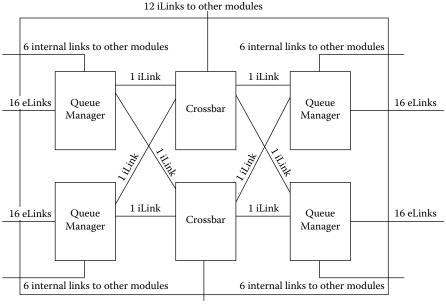

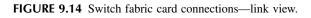

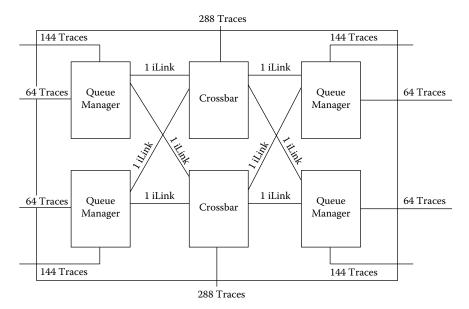

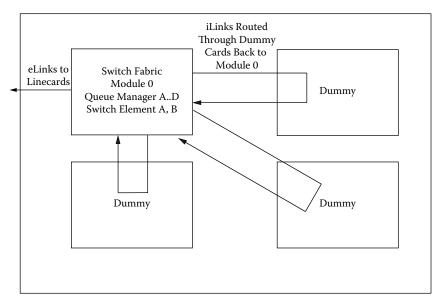

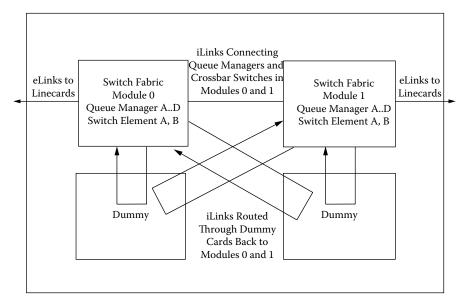

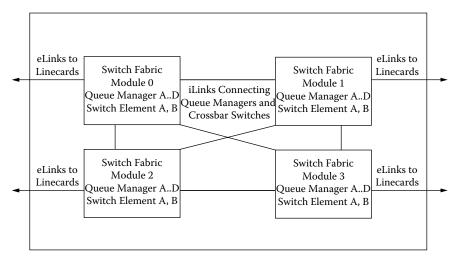

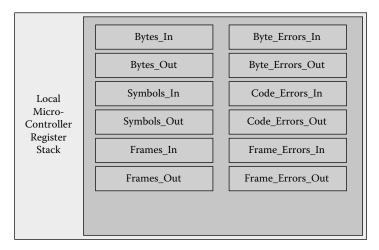

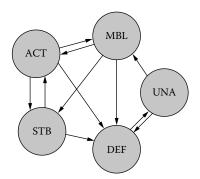

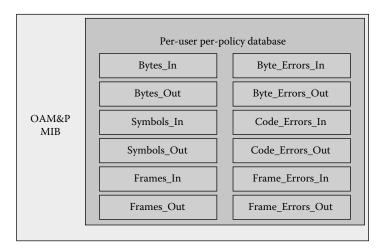

- Communicate with the PSTN infrastructure.