#### Section 5

# Basic Computer Organization and Design

Slides with white background courtesy of Mano text for this class

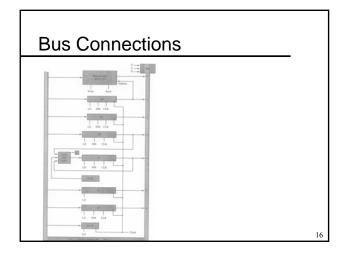

#### Mano's Basic Computer

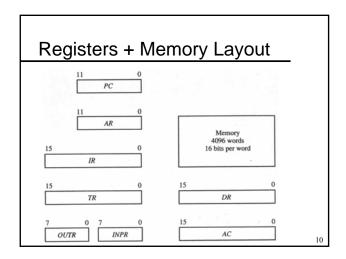

- Memory unit with 4096 16-bit words

- Registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, SC

- Flip-flops: I, S, E, R, IEN, FGI, FGO

- 3 x 8 op decoder and 4 x 16 timing decoder

- 16-bit common bus

- Control logic gates

- Adder and logic circuit connected to input of AC

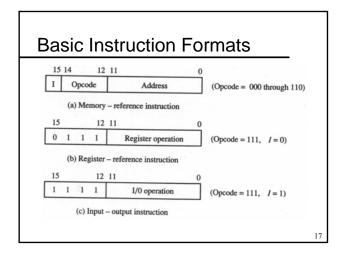

#### Instruction Code

- Computer instruction is binary code that specifies a sequence of microoperations

- Operation code + Address

- Op code must have *n* bits for  $\leq 2^n$  operations

- Op code sometimes called a macrooperation

- Address is register or memory location

Memory location is operand address

- Shorten "instruction code" to "instruction"

- Instructions and data in memory

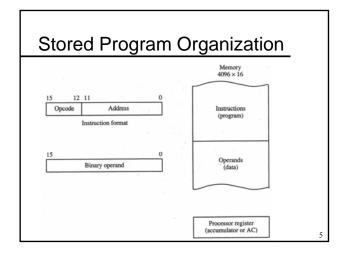

# Stored Program Organization

- One processor register

- AC accumulator

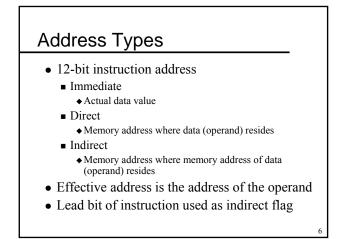

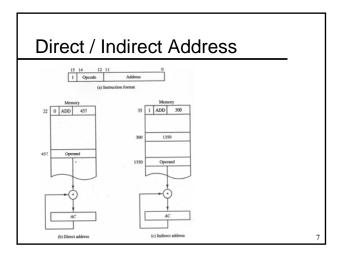

- Instruction format

- 4-bit op code

- 12-bit address (for 2<sup>12</sup> = 4096 memory words)

- Instruction execution cycle

- Read 16-bit instruction from memory

- Use 12-bit address to fetch operand from memory

- Execute 4-bit op code

| Register<br>symbol | Number<br>of bits | Register name        | Function                     |

|--------------------|-------------------|----------------------|------------------------------|

| DR                 | 16                | Data register        | Holds memory operand         |

| AR                 | 12                | Address register     | Holds address for memory     |

| AC                 | 16                | Accumulator          | Processor register           |

| IR                 | 16                | Instruction register | Holds instruction code       |

| PC                 | 12                | Program counter      | Holds address of instruction |

| TR                 | 16                | Temporary register   | Holds temporary data         |

| INPR               | 8                 | Input register       | Holds input character        |

| OUTR               | 8                 | Output register      | Holds output character       |

#### Program Counter (PC)

- Holds memory address of next instruction

- Next instruction is fetched after current instruction completes execution cycle

- *PC* is incremented right after instruction is fetched from memory

- *PC* value can be replaced by new address when executing a branch instruction

#### **Register Control Inputs**

- Load (LD)

- Increment (INR)

- Clear (CLR)

#### Common Bus

11

- Connects registers and memory

- Specific output selected by  $S_2S_1S_0$

- When register has < 16 bits, high-order bus bits are set to 0

- Register with LD enabled reads data from bus

- Memory with Write enabled reads bus

- Memory with Read enabled puts data on bus

When S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> = 111

12

15

14

#### Address Register (AR)

- Always used to specify address within memory unit

- Dedicated register eliminates need for separate address bus

- Content of any register output connected to the bus can be written to memory

- Any register input connected to bus can be target of memory read

- As long as its LD is enabled

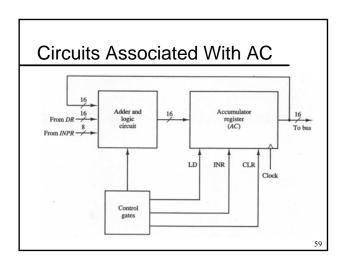

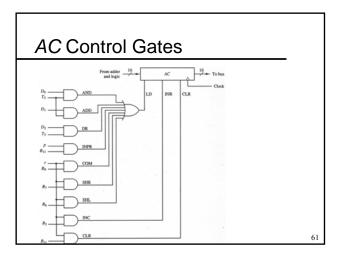

#### Accumulator (AC)

- Input comes from adder and logic circuit

- Adder and logic circuit

- Input

- 16-bit output of AC

- 16-bit data register (DR)

- ♦ 8-bit input register (INPR)

- Output

- 16-bit input of AC

- $\bullet E$  flip-flop (extended AC bit, aka overflow)

- *DR* and *AC* input used for arithmetic and logic microoperations

#### Timing Is Everything

- Content of any register output connected to the bus can be applied to the bus and content of any register input connected to the bus can be loaded from the bus during the same clock cycle

- These 2 microoperations can be executed at the same time

$DR \leftarrow AC$  and  $AC \leftarrow DR$

|        | Hexadeo | imal code |                                      |  |

|--------|---------|-----------|--------------------------------------|--|

| Symbol | I = 0   | I = 1     | Description                          |  |

| AND    | 0xxx    | 8xxx      | AND memory word to AC                |  |

| ADD    | 1888    | 9xxx      | Add memory word to AC                |  |

| LDA    | 2xxx    | Axxx      | Load memory word to AC               |  |

| STA    | 3888    | Bxxx      | Store content of AC in memory        |  |

| BUN    | 4xxx    | Cxxx      | Branch unconditionally               |  |

| BSA    | 5xxx    | Dxxx      | Branch and save return address       |  |

| SZ     | 6838    | Exxx      | Increment and skip if zero           |  |

| CLA    | 71      | 800       | Clear AC                             |  |

| CLE    | 7       | 400       | Clear E                              |  |

| CMA    | 7.      | 200       | Complement AC                        |  |

| CME    | 7.      | 100       | Complement E                         |  |

| CIR    | 7       | 080       | Circulate right AC and E             |  |

| CIL    |         | 040       | Circulate left AC and E              |  |

| INC    | 7       | 020       | Increment AC                         |  |

| SPA    |         | 010       | Skip next instruction if AC positive |  |

| SNA    |         | 008       | Skip next instruction if AC negative |  |

| SZA    |         | 004       | Skip next instruction if AC zero     |  |

| SZE    | 2       | 002 .     | Skip next instruction if E is 0      |  |

| HLT    | 7       | 001       | Halt computer                        |  |

| INP    | F       | 800       | Input character to AC                |  |

| OUT    | F       | 400       | Output character from AC             |  |

| SKI    | F       | 200       | Skip on input flag                   |  |

| SKO    | ÷.      | 100       | Skip on output flag                  |  |

| ION    | Ē       | 080       | Interrupt on                         |  |

| IOF    |         | 040       | Interrupt off                        |  |

#### Instruction Set Completeness

- Arithmetic, logical, and shift

- Move data from and to memory and registers

- Program control and status check

- Input and output

- (I/O, I/O, it's off to the bus we go...)

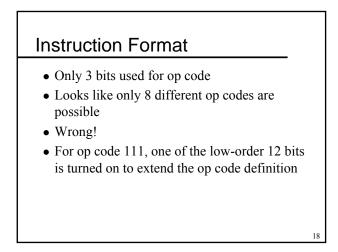

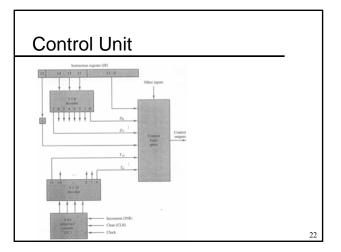

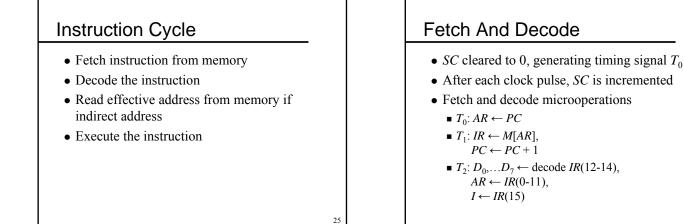

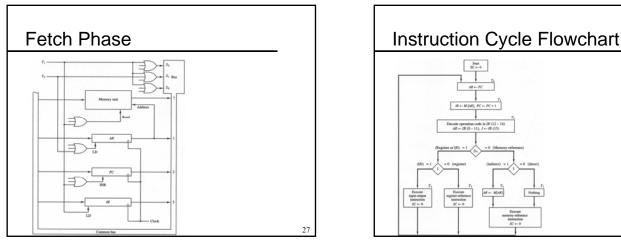

#### **Control Unit**

- Instruction read from memory and put in IR

- Leftmost bit put in *I* flip-flop

- 3-bit op code decoded with 3 x 8 decoder into  $D_0$  to  $D_7$

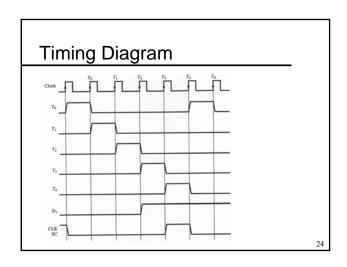

- 4-bit sequence counter (*SC*) decoded with 4 x 16 decoder into *T*<sub>0</sub> to *T*<sub>15</sub> (timing signals)

- I,  $D_0$  to  $D_7$ ,  $T_0$  to  $T_{15}$ , rightmost 12 bits of IR, and other inputs are fed into control and logic gates

21

23

# • Inputs are increment (INR) and clear (CLR) • Example • SC incremented to provide $T_0$ , $T_1$ , $T_2$ , $T_3$ , and $T_4$ • At time $T_4$ , SC is cleared to 0 if $D_3$ is active • Written as: $D_3T_4$ : SC $\leftarrow 0$

29

# $\frac{f_{n+1}^{(m)} (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)} (f_{n+1}^{(m)}) (f_{n+1}^{(m)} (f_{n+1}^{(m)}$

| Instruction | Paths |

|-------------|-------|

|-------------|-------|

- $D'_7 IT_3$ :  $AR \leftarrow M[AR]$

- $D'_7 I' T_3$ : Do nothing

- $D_7 I'T_3$ : Execute a register-reference instruction

- $D_7IT_3$ : Execute an I/O instruction

|     | <i>r</i> :                | <i>SC</i> ←0                                                            | Clear SC         |

|-----|---------------------------|-------------------------------------------------------------------------|------------------|

| CLA | <i>rB</i> <sub>11</sub> : | $AC \leftarrow 0$                                                       | Clear AC         |

| CLE | rB10:                     | $E \leftarrow 0$                                                        | Clear E          |

| CMA | $rB_9$ :                  | $AC \leftarrow \overline{AC}$                                           | Complement A     |

| CME | rB8:                      | $E \leftarrow \overline{E}$                                             | Complement E     |

| CIR | rB7:                      | $AC \leftarrow \text{shr } AC, AC(15) \leftarrow E, E \leftarrow AC(0)$ | Circulate right  |

| CIL | rB <sub>6</sub> :         | $AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15)$         | Circulate left   |

| INC | rB5:                      | $AC \leftarrow AC + 1$                                                  | Increment AC     |

| SPA | rB4:                      | If $(AC(15) = 0)$ then $(PC \leftarrow PC + 1)$                         | Skip if positive |

| SNA | rB <sub>3</sub> :         | If $(AC(15) = 1)$ then $(PC \leftarrow PC + 1)$                         | Skip if negative |

| SZA | $rB_2$ :                  | If $(AC = 0)$ then $PC \leftarrow PC + 1)$                              | Skip if AC zero  |

| SZE | $rB_1$ :                  | If $(E = 0)$ then $(PC \leftarrow PC + 1)$                              | Skip if E zero   |

| HLT | $rB_0$ :                  | $S \leftarrow 0$ (S is a start-stop flip-flop)                          | Halt computer    |

32

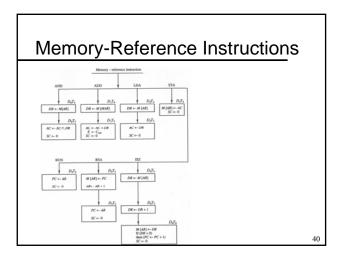

|        | Operation | Quelo la descisión                               |

|--------|-----------|--------------------------------------------------|

| Symbol | decoder   | Symbolic description                             |

| AND    | $D_0$     | $AC \leftarrow AC \land M[AR]$                   |

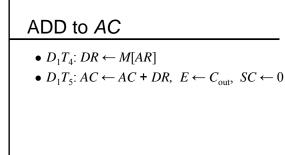

| ADD    | $D_1$     | $AC \leftarrow AC + M[AR], E \leftarrow C_{out}$ |

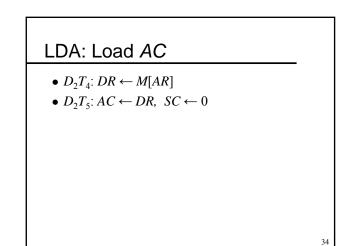

| LDA    | $D_2$     | $AC \leftarrow M[AR]$                            |

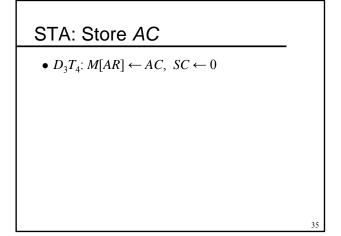

| STA    | $D_3$     | $M[AR] \leftarrow AC$                            |

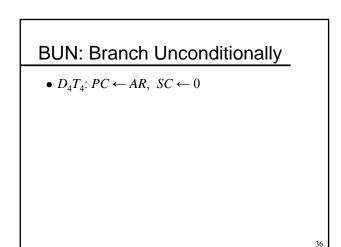

| BUN    | $D_4$     | $PC \leftarrow AR$                               |

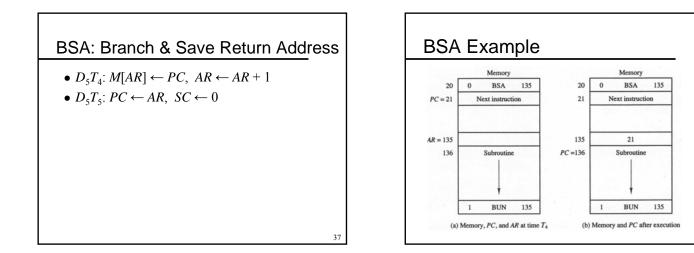

| BSA    | $D_5$     | $M[AR] \leftarrow PC, PC \leftarrow AR + 1$      |

| ISZ    | $D_6$     | $M[AR] \leftarrow M[AR] + 1,$                    |

|        |           | If $M[AR] + 1 = 0$ then $PC \leftarrow PC$       |

#### AND to AC

- $D_0T_4$ :  $DR \leftarrow M[AR]$

- $D_0T_5$ :  $AC \leftarrow AC \land DR$ ,  $SC \leftarrow 0$

39

## ISZ: Increment & Skip if Zero

- Increment word specified by effective address

If value = 0, increment PC

- $D_6T_4$ :  $DR \leftarrow M[AR]$

- $D_6T_5$ :  $DR \leftarrow DR + 1$

- $D_6T_6: M[AR] \leftarrow DR, SC \leftarrow 0,$ if (DR = 0) then  $(PC \leftarrow PC + 1)$

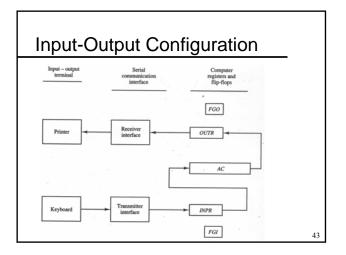

### Input Register INPR

- 1-bit input flip-flop *FGI*

- Initially cleared to 0

- When key hit on keyboard

- 8-bit alphanumeric code is shifted into *INPR*

- Input flag FGI set to 1

- No more input can be accepted from keyboard

- Computer checks FGI, when set to 1

- Parallel transfer from *INPR* to *AC*

- FGI cleared to 0

- More input can now be accepted from keyboard

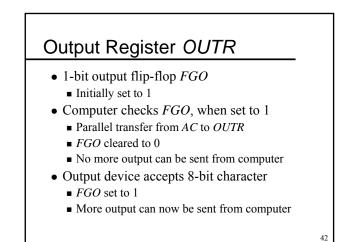

| IR(i) =<br>INP<br>OUT<br>SKI<br>SKO<br>ION<br>IOF | p:<br>pB <sub>11</sub> :<br>pB <sub>10</sub> :<br>pB <sub>9</sub> :<br>pB <sub>8</sub> : | $SC \leftarrow 0$<br>$AC(0-7) \leftarrow INPR,  FGI \leftarrow 0$<br>$OUTR \leftarrow AC(0-7),  FGO \leftarrow 0$<br>If (FGI = 1) then (PC \leftarrow PC + 1)<br>If (FGO = 1) then (PC \leftarrow PC + 1)<br>$IEN \leftarrow 1$<br>$IEN \leftarrow 0$ | Clear SC<br>Input character<br>Output character<br>Skip on input f<br>Skip on output<br>Interrupt enabli<br>Interrupt enabli |

|---------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

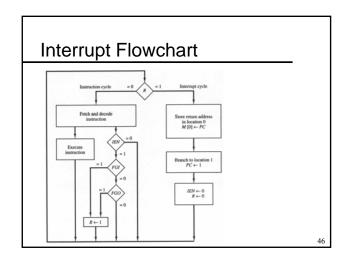

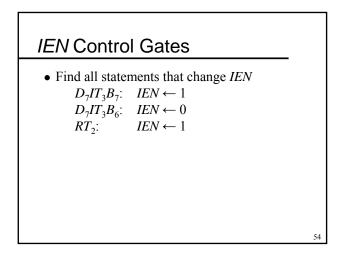

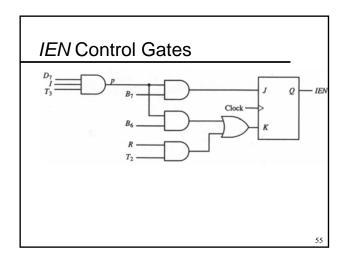

#### Interrupt Enable IEN

- Having computer constantly check *FGI* and *FGO* via an executable instruction is a waste of time

- Instead, *IEN* is programmatically set, effectively saying "let me know if you need me"

- Meanwhile, it keeps executing instructions

- During each execution cycle, if computer detects *FGI* or *FGO* is set, then *R* is set to 1

- The interrupt happens when the computer is ready to fetch the next instruction

45

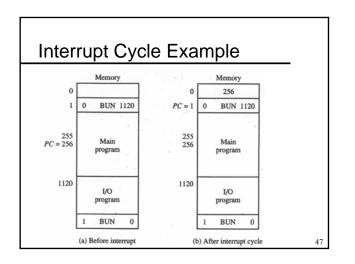

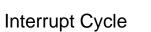

- R = 0 means go through instruction cycle

- R = 1 means go through interrupt cycle

- Condition for setting *R* to 1  $T'_0T'_1T'_2(IEN)(FGI + FGO): R \leftarrow 1$

- Fetch phase modified to service interrupt  $RT_0: AR \leftarrow 0, TR \leftarrow PC$   $RT_1: M[AR] \leftarrow TR, PC \leftarrow 0$  $RT_2: PC \leftarrow PC + 1, IEN \leftarrow 0, R \leftarrow 0, SC \leftarrow 0$

48

© 2004 by Ted Borys. All rights reserved.

50

52

#### Inputs To Control Logic Gates

- Two decoders

8-bit instruction and 16-bit sequence

- Seven flip-flops: I, S, E, R, IEN, FGI, FGO

- IR bits 0 through 11

- *AC* bits 0 through 15

- Check if AC = 0 and check sign bit

- *DR* bits 0 through 15

Check if *DR* = 0

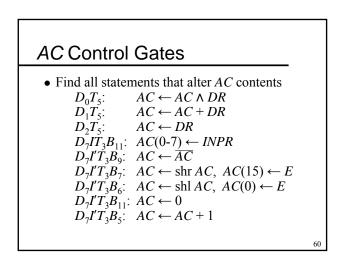

#### **Outputs Of Control Logic Gates**

- Control inputs of nine registers

- Control read & write inputs of memory

- Set, clear, or complement flip-flops

- $S_2$ ,  $S_1$ , and  $S_0$  to select a register for the bus

- Control AC adder and logic circuit

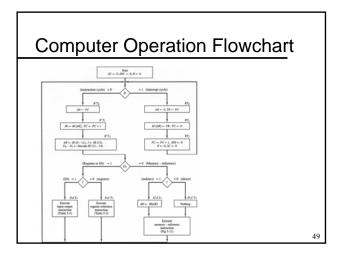

#### AR Control Gates

- Register control inputs: LD, INR, and CLR

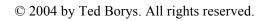

- Find all statements that alter AR contents  $P'_{T}$

| $KI_0$ :      | $AR \leftarrow PC$       | LD  |

|---------------|--------------------------|-----|

| $R'T_2$ :     | $AR \leftarrow IR(0-11)$ | LD  |

| $D'_7 IT_3$ : | $AR \leftarrow M[AR]$    | LD  |

| $RT_0$ :      | $AR \leftarrow 0$        | CLR |

| $D_5 T_4$ :   | $AR \leftarrow AR + 1$   | INR |

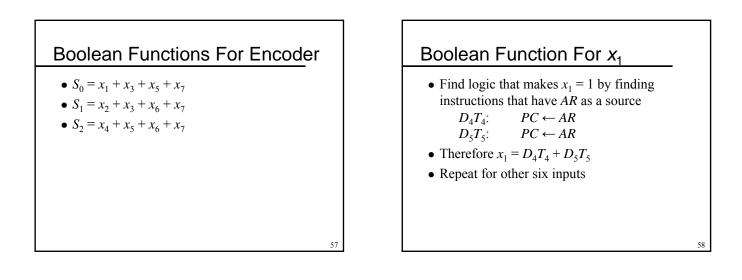

| Register<br>selected<br>for bus | Outputs |       |    |                       | Inputs                |            |                       |                       |                       |                       |

|---------------------------------|---------|-------|----|-----------------------|-----------------------|------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                                 | So      | $S_1$ | S2 | <i>x</i> <sub>7</sub> | <i>x</i> <sub>6</sub> | <i>x</i> 5 | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | <i>x</i> <sub>2</sub> | <i>x</i> <sub>1</sub> |

| None                            | 0       | 0     | 0  | 0                     | 0                     | 0          | 0                     | 0                     | 0                     | 0                     |

| AR                              | 1       | 0     | 0  | 0                     | 0                     | 0          | 0                     | 0                     | 0                     | 1                     |

| PC                              | 0       | 1     | 0  | 0                     | 0                     | 0          | 0                     | 0                     | 1                     | 0                     |

| DR                              | 1       | 1     | 0  | 0                     | 0                     | 0          | 0                     | 1                     | 0                     | 0                     |

| AC                              | 0       | 0     | 1  | 0                     | 0                     | 0          | 1                     | 0                     | 0                     | 0                     |

| IR                              | 1       | 0     | 1  | 0                     | 0                     | 1          | 0                     | 0                     | 0                     | 0                     |

| TR                              | 0       | 1     | 1  | 0                     | 1                     | 0          | 0                     | 0                     | 0                     | 0                     |

| Memor                           | 1       | 1     | 1  | 1                     | 0                     | 0          | 0                     | 0                     | 0                     | 0                     |

#### Mano's Basic Computer

- Memory unit with 4096 16-bit words

- Registers: AR, PC, DR, AC, IR, TR, OUTR, INPR, SC

- Flip-flops: I, S, E, R, IEN, FGI, FGO

- $3 \ge 8$  op decoder and  $4 \ge 16$  timing decoder

- 16-bit common bus

- Control logic gates

- Adder and logic circuit connected to input of AC

63