# DISTANCE RELAYS, FAULT LOCATORS AND THEIR DESIGN USING ANALOG/DIGITAL CIRCUITS

#### **A DISSERTATION**

Submitted in partial fulfilment of the requirements for the award of the degree

of

#### MASTER OF ENGINEERING

in

# WATER RESOURCES DEVELOPMENT (ELECTRICAL)

WATER RESOURCES DEVELOPMENT TRAINING CENTRE UNIVERSITY OF ROORKEE ROORKEE (U.P.)

April 1978

# CERTIFICATE

Convision that the discontation catibled 'Distance Relays, Fould Lesature cat their Design Using Analog/ Digital Circuite' which is being subsitted by Eri L.A.Derezho in portial fulfilment for the succe of the Degree of Master of Engineering in Veter Recourses Development (Electrical) of the University of Receive is a record of the condition's out whit control out by him under our supervision and guidence. The potter embedded in this discortation has not been examined for the succession has not been examined for the succession

Theo to Arther to costily that he had veried for a period of 6 antihe from 1.10.1977 to 3.4.78 for propering the discortation for Master of Ingineering degree at the University.

Dates 3.4.1978

1 1 4

78 (N.L.DEMAL) LOOTIFOF Elcet. Ingg. Doptt. University of Rosenco. ROULINE

(I. C. CHAULAT) 3.4.78 Eorder (Blootrich) U.R.D.S.C. University of Leerico. DODL TT

# ACKNOWLEDGEMENTS

I deam it a proud privilege to thank wholehwartedly and to record herein my deep sense of gratitude to Sri M.L. Deval. Lecturer. Electrical Engineering Deptt., University of Roorkee, Roorkee for his valuable guidance and encouragement. as also to Sri R.C. Chauhan, Reader, WEDTC for his timely help and guidance.

My thanks are also due to the Prof. & Head Sri O.D. Thapar and the faculty of the WEDTC for having extended to me all necessary facilities.

I have drawn a wealth of information from the several references listed and I thank the authors concerned for having utilized their material freely.

Lastly I am highly grateful to my parent organisation, the Karnetaka Electricity Board, Bangalore for having deputed me to the WEDTC, University of Roorkee for undergoing the training course and the Master of Engineering degree course.

× . K.

L. A. NORONHA Asstt.Engr.(E1),KEB on deputation at W.R.D.T.C., University of Roorkee, Roorkee(U.P.)

ROORKEE

Deted: 3.4.78

# <u>c o d 8 b d 8 e</u>

# Phoe 9

| CHAPTER | I   | ALTERODUCTION 9 - 9                                                                      |

|---------|-----|------------------------------------------------------------------------------------------|

| CHAPTE  | 11  | LIFLAY ELEMENTS THE IR TYPES AND<br>INCLUT DEVELOF. THITS IN DISTANCE<br>ELEMANNG 4 - 29 |

|         | 2.1 | Introduction                                                                             |

|         | 5.2 | Elcotranguotic rolayo                                                                    |

|         | 2.3 | Elcotrento roleyo                                                                        |

|         | 2.4 | Statte rolayo                                                                            |

|         | 2.9 | Resent devolopmento in Diotoneo<br>Protection                                            |

|         | 2.6 | Ceneluciono                                                                              |

| CHAPTER | III | CHARACTERISTICS OF DISTANCE HELAYD 26 - 68                                               |

|         | 9.1 | Distance relays as comportions                                                           |

|         | 3.2 | Clossfication of comparators                                                             |

|         | 9.9 | Conventional or Electronugnotic<br>Giotence roley cheresteristics                        |

|         | 9.4 | Cherectoriotics of static roleys                                                         |

|         | 5.5 | Speakal oheresteristics                                                                  |

|         | 9.6 | Loloy roopence                                                                           |

|         | 9.7 | Dooirablo obcrectoriotico for<br>Osoteneo roleyo                                         |

|         | 9.0 | Ceneluolono                                                                              |

| CHAPTER | IV  | PAULY LOCATORS - THEIR DEVELOPATIZE,<br>TYLES AND THEIR REQUIREMENTS E9 - 116            |

|         | 4.1 | Introduction                                                                             |

|         | 4.2 | Dovolopcento in fault Locatoro                                                           |

|         | 4.9 | Echaroncing Soult locatoro                                                               |

|         | Q.Q | Pault locators based on measurant                                                        |

|         | 4.9 | Cround fault locators bacad an<br>nonourenents of residual currents                      |

|         | 4.6 | Pault Locatoro voing noutral constaro                                                    |

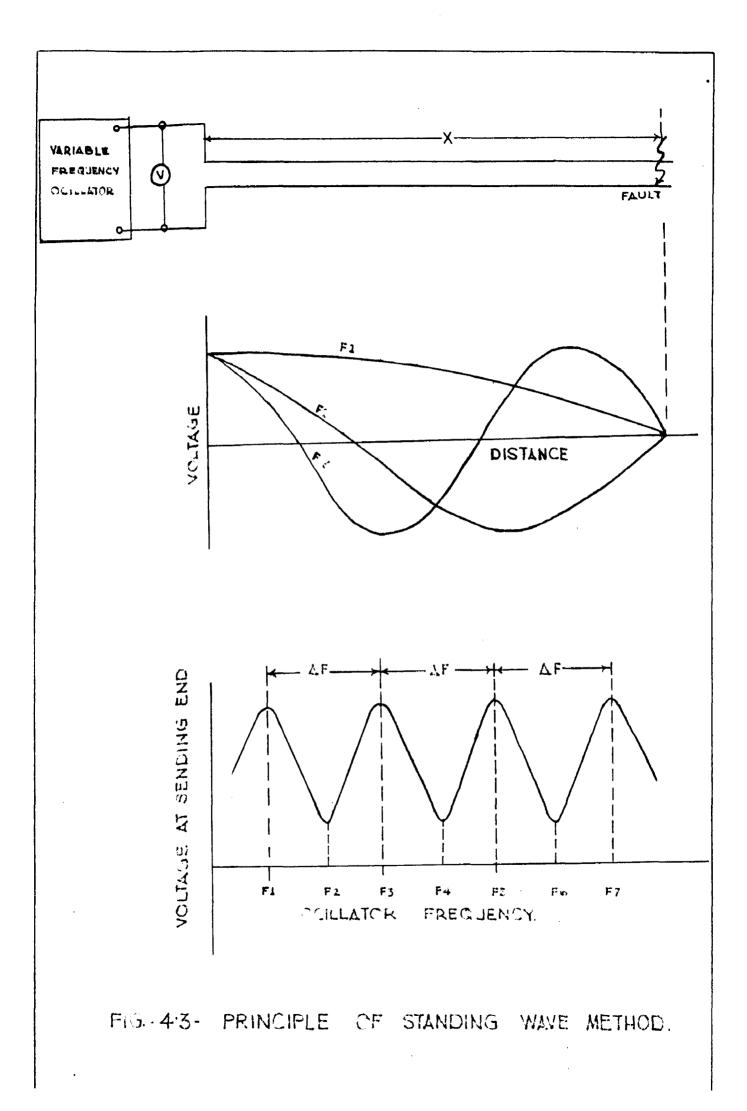

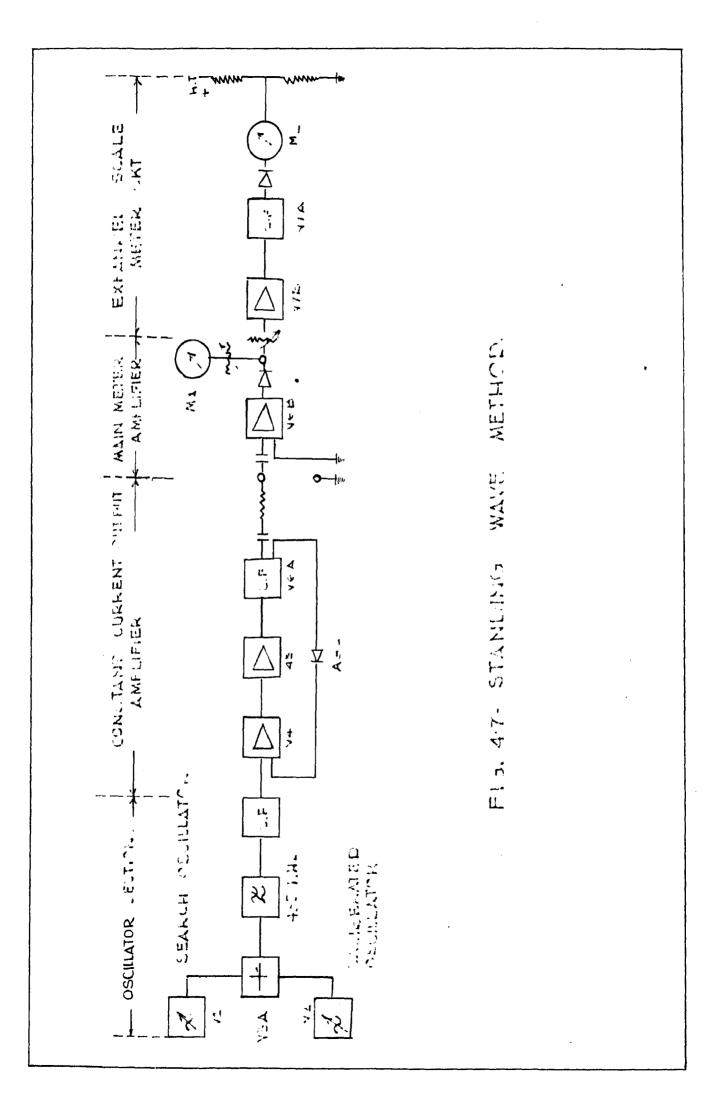

|         | 4.7 | Poult location using standing voro nothedo                                               |

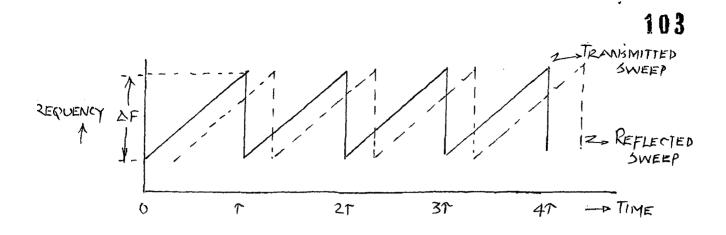

|         | 0.0 | Foult locators using frequency modulation<br>mothods                                     |

- 4.9 Foult locatoro baced on mecourchest of impodence

- 6.10 Poult locatoro bacca en monsurcacent of industanco

- 4.19 Delco portion fault locatoro

- 4.12 Pouls locator wing negative coquence

- 4.19 Use of transistors in fault locators

- 4.14 Gervoy of nois typos of feult locators

- 4.15 Exportence of a fault locator in acrvice

- 4.16 Bocomo for rookrietod uso of foult locatoro

- 4.17 Dogulacianto of a lault locator

- 4.18 Copubility of a fault locator

- 4.19 Concluciono

- CHAPTER V DEGIGE AND DEVELORATING OF THE DISEANCE MELAY ALONG WITH THE PAULE LOCATOR USING ANALOG/DIGITAL CIECUITS

· 1977 - 1771

- 5.1 Introduction

- 5.2 Moonsing United

- 5.9 Binary, Dooinel and Octol nurbero

- 5.0 Binory codor

- 9.5 Decloca Algebra and gateo

- 5.6 Arithootic offenito

- 5.7 Intograted circuito

- 5.8 Cloopfication of logic article

- 5.9 Multivibratoro cas filp-flopo

- 5.10 Baolo Blockraite countero

- 5.19 Operational coplassor

- 5.12 Doolca of the proposed Poloy cad fault locator

- 5.13 Deceription of the elreultry

- CHAPTER VI COLOLUSIOIS

··· 172 - 97:

174 - 18

HEFFRINCES

# LACE OF ADERVIATION

.

| IV              | Kilovolto                |

|-----------------|--------------------------|

| £¢              | ROOS                     |

|                 |                          |

| P.7°0/p.%.*0    | Potential Arcaofereoro   |

| ∇.2°0/∇.∿'0     | Voltoso tecnolardoro     |

| 0.2./0.0        | Curront transcrourd      |

| oca'o           | over current rolayo      |

| 900/900         | constant out out a sold  |

| D/B             | Reolotaneo               |

| X/11            | Locolares                |

| 8               | Inpolenco                |

| IHV/o.h.v.      | Catro Al Ca voltaco      |

| H.V./h.v.       | TACA VOLOGO              |

| 0°0°            | olternothing current     |

| 4.0.            | Barcot current           |

| CEO             | Cotheto Day Ocelllograph |

| 8.0./0.0.       | Dicers Clacult           |

| 0.C./0.6.       | Open elecuts             |

| 8.20            | FCALO Progrady           |

| KHB             | Relo Horto               |

| nor./nin.       | Mondown/Ninsown          |

| 20              | MAILAccorneo             |

| 0+ <u>3</u> +   | തലൂർ                     |

| X .C .          | church execute           |

| \$.0.           | 01 \$0 <i>4</i> 0        |

| D.2.2°0         | Normotemotivo sereco     |

| 0.0.8.0         | olcotratolivo larcoo     |

| $\nabla \Delta$ | Vol Conceo               |

|                 |                          |

#### CHAPTER - 1

#### INTRODUCTION

1.1 The huge capital investment involved in a power system for the generation, transmission and distribution of electrical power is so great that proper precautions must be taken to ensure that the equipment not only operates as nearly as possible at its peak efficiency but also that it is protected from faults and accidents ensuring thereby reliability, dependability, uninterrupted service of quality and loss of revenue. This fact has all the more been accentuated by the complexity of system designs involved by large scale interconnections coupled with it's associated problems of stability, autoreclosing, faster fault clearing times, higher degree of accuracy, speed and sensitivity.

1.2 Transmission lines have air as it's principal insulation in addition to an insulation of a high resistivity material such as porcelain which is used as a mechanical support to the structure carrying the line conductors. Air insulation can be accidentally short circuited by birds, rodents, snakes, kitestrings, tree limbs, creepers etc. or reduced in insulation strength by ionisation due to lightning, corona etc., Porcelain insulators may be bridged by moisture with dirt or salt and can become cracked. They may even flashover due to atmospheric pollution such as is caused by dust and soot deposits. Other disturbances to the system may be caused by power swings, loss of synchronism etc. 1.5 The protection of transmission lines against all eventualities has been and is still engaging the attention of power and relay engineers to attain the art of perfection in the protection of transmission lines and so also has been the continuing development in the field of transmission line fault locators. This is very much true as line patrolling to locate a fault on an overhead line is time consuming, expensive and moreso in bad weather, rough country on long extra high voltage lines.

1.4 This dissertation therefore reviews the development in the field of transmission line protection with particular reference to distance relaying and fault location methods. The possibilities in the development of a distance relay along with a fault locator using analog and digital circuits has been indicated.

1.5 The historical development of relays, both conventional electromagnetic and static have been briefly discussed and dealt with in Chapter II, as also the recent trends in the application of microprocessors, minicomputers and on-line digital computers for distance relaying purposes.

1.6 The characteristics of electromagnetic distance relays and of the static distance relays are dealt with in Chapter III, along with a discussion on the desirable characteristics of the distance relays.

1.7 The historical development of the fault locators, their different types that have been used and are being used, is treated in Chapter IV. The requirements and capabilities of a fault locator as also the necessity of having a fault locator in service have also been spelt out in the said chapter.

1.8 The design possibilities in developing a distance relay along with a fault locator having a digital display which indicates directly the distance to the fault is detailed out at the end in Chapter V along with the required circuitry. A resume of digital principles and applications of the same for developing the relay and the fault locator is treated in the earlier part of the said chapter.

1.9 The conclusions drawn from this dissertation and the scope for further work is made known in Chapter VI.

#### CHAPTER-II

4

# RELAY ELEMENTS THEIR TYPES AND RECENT DEVELOPMENTS IN DISTANCE RELAYING

#### 2.1. INTRODUCTION

The earliest form of protection was the fuse which still today is in use on distribution circuits and lines because of its simplicity and cheapness. It however suffered from the disadvantage of not only requiring replacement before power supply could be restored but also lacked in speed of operation, selectivity, discrimination etc., and was therefore replaced ultimately by electromagnetic relays.

# 2.2. ELECTROMAGNETIC RELAYS

### 2.2.1. Early development

The earliest form of electromagnetic volues were of the attracted armature, solenoid and plunger, hinged armature and balanced beam types. These relays have a tendency to operate inadvortently on sudden charges in circuit conditions and as measuring units are handicapped by inherently low resol/pick up ratios<sup>(1)</sup> The attracted armature type relays are still used for all auxiliary relays such as annunciators, semaphore indicators, alarm relays otc., The balanced beam type relay has been used extensively for high speed differential relays and impedance relays. This relay provides a very fast clearing time of the order of one cycle but tends to overreach on faults, has a low resetting value compared to it's operating value and is succeptible to the transients due to the asymmetrical d.c. in the current wave<sup>(1)</sup>. It may, however, be stated that the balanced beam type is a simple and commical rolay and as such has been extensively used in the relays manufactured by H/3 Brown Boweri Ltd.<sup>(2)</sup> and H/S ASEA<sup>(3)</sup> with improved designs.

#### 2.2.2. Subsequent Development

As power systems increased in size and complexity it was necessary to employ more precise relay mechanisms with selectivity on an inverse current basis. This was achieved in the induction disc watthour meter which was converted into a relay by substituting contacts for the indicating register. This resulted in the inverse time overcurrent relays which are still in use today, although in an improved form.

2.2.3. The induction relay in it's improved form has a cup shaped armsture and is made for fast operation with reasonable immunity from system transients and it's drop out is within a few percent of it's pick up so that it is used where normal and abnormal conditions are very close to oneanother. These relays can be of the 2 or 4 pole single phase or 8 pole 5 phase or a split cup 4 pole unit with shaded pole arrangomente<sup>(1)</sup>. The 4 pole induction cup relay has been widely used by M/S General Electric Co., and M/S Westinghouse Co. Ltd. of U.S.A.<sup>(4,5)</sup> and as well by M/S English Electric Co., of India Ltd., Hadras<sup>(6)</sup> for distance protection owing to the following advantageo such as

- (i) high open of operation,

- (ii) absence of second harmonic torques due to transionts as is encountered in the balanced beam type,

- (iii) low burden on C.T's and V.T's,

- (iv) uniformity in the torque produced during the period of operation.

2.2.4. The 8 pole induction cup relay was first developed and used as a polyphase distance relay(7) in 1937 and was subsequently improved upon by Beeman and Beard in 1941. It was in 1934 that A.R.Von C. Carrington<sup>(8)</sup> attempted to reduce the number of relays by switching the proper voltages on the occurrence of a fault by means of a phase selector rolay which discriminates between different types of fault. The involvement of a phase selector relay, did not find much practical use, for it's applicability. It was however in 1954 that the first polyphase distance relay developed by Gavenko, Popas and Sapiro<sup>(9)</sup> to operate correctly on all interphase faults was applied to actual systems. In 1948<sup>(5)</sup>. M/S Westinghouse Co., Ltd. developed a polyphace relay for phase faults only and was subsequently modified to the K-Dar Componsator distance relaying scheme to cover all types of faults. The switched reactance relays to cover both phase and ground faults is used currently in the SSRBJV English Electric Relays<sup>(6)</sup>.

#### 2.2.5. Salient Features of Electromagnetic Relays

The saliont features of electromagnetic relays used currently for distance protection may be summarised as follows -

(1) positive operation because of rigid specifications and quality control in the design and manufacture of contacts, coils, bearings and other mechanical components backed by over 50 years of experience in manufacture.

(ii) consistent operation as proved by field experience (iii) fast operating time of the order of  $1/\frac{1}{2}$  cycle.

- (iv) their use as back up relays in connection with carrier protection schemes.

- (v) apathy on the part of power engineers in our country to go in for static relays but to roly heavily on electromagnetic rolays moreso cut of conservatism to depend upon time proved performance, experience gained in their application, testing, maintenance and also perhaps due to lack of knowledge of electronic and transistor circuitry to which our elder engineers never had an opportunity of being expessed to, either, in their curriculum or in the field.

## 2.3.1. ELECTRONIC RELAYS

2.3.1. Early Dovalopment

It was realised as long back as in 1948 in a paper<sup>(10)</sup> presented by R.H. Me Pherson et al that the development in system design, high speed reclesing problems connected with stability and the increasing demand for higher degrees of accuracy, speed and dependability have accentuated these problems to a point where the inherent limitations of electromagnetic relays are raising barriers for the achievements of the desired goals. The increasing use of electronic circuits coupled with the great strides made by electronics in nearly every field of engineering and the widespread interest in electronic devices of all kinds, pointed out the way to protection engineers to use electronic means for lifting these barriers. The said paper reports that it was in 1927 that Hr. A.S. Fitzerald developed an electronic pilot relaying system to evereme the limitations of pilot wires when

.7

operating over long lines. The scheme was abandoned because of the short life and the high cost of the tubes available then. But a somewhat similar scheme is still in use today in the phase comparison carrier current relaying. In 1931, Holf Hidoroe (11) of Horway developed electronic circuits for most of the common protective relays using thyratron tubes wherein the undervoltage. over current, power directional and distance relays used input circuits consisting of transformers, metal rectifiors, linear resistance, inductance, capacitance elements to sum up and compare functions of system voltage to form a resultant single voltage for operation of the thyratron tube relay. In 1932, in the U.C. a laboratory sample reactance relay was built and tosted but was not developed further (10), because the electromagnetic relay was fully adoquate for the moods of the industry and no stops were taken to put the electronic relay into production. This type of electronic relay was built because it embodied all the common rolay principles in a single rolay and hence presented all the problems of the different types such as over current, under voltage directional, differential and distance relays. The experience gained from this development was destined to become valuable for all future developments.

2.3.2. Carrier rolaying wis the principal source of experience with tubes. In the early days, tubes had an irregular life, required frequent replacement and led to the general impression that the tripping of the circuit breaker should not be dependent upon the operation of the tube. The gradual improvement in tubes and replacement averaging once a year reduced skepticism that

tripping via tubes was not acceptable. The interest in electronic tubes was all the more aroused with the advent of long life tubes, consistent operating time as well as consistent low operating times even at low currents for more effective use of instantaneous reclosing. It was also realised that the lack of inertia, in tubes unlike in the case of electromagnetic relays which tends to operate the relay at the remote end of a fault more slowly, would enable an electronic relay with an operating time totally independent of the magnitude of the current or location of the fault and consequently would also enable simultaneous tripping of the breakers at both ends of the line.

2.3.3. The first relay using thermonic values was described by Ms Pherson et al<sup>(10)</sup> and was applied for distance protection, wherein the line voltage was compared with the line current and consisted of a gulsing circuit, measuring circuit and the tube circuits. The pulsing circuit was used to generate a pulse at the moment of maximum line voltage and the pulse was used to overcome a large grid bias of the tube allowing it to conduct. The measuring circuit was the sonsitive element which made responsive to signals emanating both from the pulsing circuit and measuring circuit. The response of the tube circuit initiated the tripping signal when the impedance being measured fell below the sot value of the relay. The operating time of this relay was found to be instantaneous and the burden negligible. 2.3.4. Subsequent Developments

In 1954, Borgseth<sup>(12)</sup> published a paper on direct phase comparison distance scheme using a diode co-incidence circuit.

In the same year Kennedy<sup>(13)</sup> described an electronic carrier relaying scheme using no electromagnetic relay and even the tripping was performed by the use of a heavy duty thyratron. A resume was also given in the same year by A.R. Van C. marring $ton^{(14)}$  on electronic protective relays.

#### 2.3.5. Reasons for non use of electronic relava

disctronic relays however did not find much favour with power engineers though used extensively for carrier communication and relaying principally on account of:

- 1) large volume of space occupied in assembling the circuitry and its cost

- ii) fragility of electronic tubes and components

- 111) uncertainty in the operation of the tubes

- iv) requirements of anode supplies and cathode heater requirements.

- v) problems encountered to ensure correct operation during transient conditions, and

- vi) the inability of electronic circuits and relays to surpass the quality and reliable performance of the well established and cheap electromagnetic relays which were backed by several years of proven field experience.

# 2.3.6. Operational advantages of Electronic relays

Those relays operationally claimed to have the following advantages:

- 1) low burden on C.T's and V.T's since operating power is from an auxiliary d.c. supply.

- 11) absence of mechanical inertia and contact bounce.

iii) vory high speed of operation - almost instantaneous

iv) low maintenance, owing to the absence of moving parts.

#### 2.4. GRATIC RELAYS

# 2.4.1. Definition of a static relay

The ASA definition of a static relay as published in IdEd Committee Report<sup>(35)</sup> is " A relay or (relay unit) in which there is no armature or other moving element, the designed response being developed by electronic, solid state, magnetic or other components withoutmechanical motion ".

2.4.2. As such a static protoctive relay refers to a relay in which the measurement or comparison of electrical quantities is done in a static network which is designed to give an output signal in the tripping condition when a threshold condition is passed. The output signal operates a tripping device which may be electronic somi-conductor or electromagnotic.

# 2.4.3. Classification

Static rolays are classified according to the type of the measuring unit or the comparator and are as follows :-

- 1) Electronic rolays

- 11) Transductor relays

- 111) Rectifier bridge relays

- iv) Transistor rolays

- v) Hall offoct relays

# vi) Gauss effect relays.

Amongst the above rolays, the transistorised rolays and rectifier bridge relays are the most widely accepted type of static rolays so much so that the word static relays is synonymous with transistorised and semi-conductor relays<sup>(15)</sup>. Accordingly though electronic relays do fall in the domain of static relays they have been described earlier to review their historic development. Somi-conductor devices have overcome the limitations of thermionic tubes and have eventually taken the pride of place of being described as static devices.

# 2.4.4. Advantages of static rolavs

In 1962, M.Kaufman<sup>(16)</sup> reported the opinion of a committee of experts constituting the countries represented by Belgium, France, Germany, Foland, Switzerland, Sweden, U.K. and U.S.A. conferring the following advantages upon static relays over the electromagnetic relays and arc.

- 1) quick rosponse, long life, high resistance to shock and vibration

- 11) quick reset action a high reset value and absence of oversidet which is easily achieved because of the absence of mechanical inertia and themal storage.

- iii) No bearing friction or contact troubles such as corrosion, bouncing, wear and honce minimising maintenance.

- iv) Ease of providing amplification thus enabling higher degree of geneitivity to be obtained.

- v) The low energy levels required in the measuring circuits permit miniaturisation and at the same time minimise current transformer inaccuracies.

- vi) Greatly improved pick up/ drop off ratio

- vii) The basic building blocks of somiconductor circuitry permit a greater degree of sophistication in the shaping of operating characteristics enabling the practical realisation of relays with threshold characteristics more closely approaching the ideal requirements.

- viii) Uce of printed or integrated circuits avoids wiring errors and facilitates rationalisation of batch production.

- 2.4.5. Static rolays employing transistors have their limitations and which are :

- 1) variation in their characteristics with temperature and ago

- dependence of reliability on a largo number of small

components and their electrical connections

- 111) low short airanit time over load capacity as compared with electromagnetic relays.

It has fortunately nowbecome possible to compensate for all of the above limitations. The use of thermistors eliminate temperature error, whilst agoing may be minimized by preseaking for several hours at a relatively high temperature. The factors (ii) and (iii) listed above are the design features of the circuit and careful design can compensate if not eliminate these limitations<sup>(15)</sup>.

# 2.4.6. Dovelopment in Transistoricad relays

In 1956, C. Adamson and Wedopohl<sup>(17,18)</sup> described the development of a the distance rolay with junction transistors and was styled " Dual Comparator the type relay". The derived voltage inputs from the system fault voltages and currents were applied to a coincidence circuit. This rolay was however not exploited commercially<sup>(19)</sup>. The first wholly static distance relay<sup>(20)</sup> to be produced commercially was a transistorised version of the electronic the relay developed by the Pherson et al<sup>(10)</sup> in 1960. In 1966 K. Parthearathy developed a new 3 step solid state static rolay<sup>(25)</sup>

for distance protection and as well as a polyphase static distance relay<sup>(26)</sup>. Subcequently Sri Gupta S.C.<sup>(27)</sup> developed and designed a polyphase static distance relay in 1969 based on the principle of phase sequence measurement of the relay terminal voltages and it's performance was claimed to be much better than the earlier polyphase static distance relays. In 1970, N.M.Anil Kumar<sup>(28)</sup> suggested in his paper a polyphase relaying scheme based on phase sequence detection of the compensated voltages at the relay point and also indicated how different characteristics may be obtained by modifying the relay inputs. -Meanwhile documented work on Rectifior bridge compara-2.4.7 tors took place in Horway<sup>(19)</sup> and Germany. These basically consist of two rectifier bridges and a moving coil or polarised relay and by variation of the taps or of the comparator used, different characteristics could be obtained. Those relays are widely used today in U.K., U.S.A., Continental Europe for distance protection.

2.4.8 Static relays with conic section characteristics and quadrilateral characteristics have also been developed by A. Vitanov<sup>(37)</sup>, H.P. Whincha et al<sup>(39,40)</sup> Sri Anil Kumar<sup>(28)</sup> and others. A comprehensive treatment of these type of characteristics along with their development is given in para 3.5 of Chapter III.

2.4.9 A comprehensive literature on relays based on "Hall Effect" and "Gauss Effect" relays is given by A.R. Van C. Harrington<sup>(19)</sup>. The high cost of the Hall crystals, large temperature error and low output have prevented it's commercial

omploitation except in the USSR<sup>(15)</sup>. Similarly crystals based on Causs Effect have not been used because of it's prohibitive cost.

# 2.4.10 Banarvations in the use of Static Relave

Though static relays have soveral inherent advantages, the reservations of cortain utilities in their use have been exposed by the AIBE Committee Report in 1965<sup>(22)</sup>. They in order are

- (1) susceptibility of static relays to maloperate on transients caused by electromagnetic and electrostatic coupling.

- (11) that they have an upper and lover appiont temperature whereas electromagnetic relays operate at any temperature.

- (111) requires a reorientation in the thinking and the servicing practices of relay engineers. Often expensive test equipment is required along with the services of engineers with good electronic training.

- (iv) failure of diodes due to high voltage on pilot wires, deterioration of somiconductors due to excessive heat, failure resulting from switching surges, inductive kicks, and contact bounce of the electromagnetic relays when emergicing the trip coil of a circuit breaker.

The above objections to a large extent have been overcome and static relays are finding wide application in the relaying of EEV systems co as to provide a means for obtaining the desired overall characteristics as also to have the highest reliability and the highest possible security factor<sup>(21)</sup>. As such they are increasingly being used by several utilities abroad as the main primary protection.

#### 2.5 RECENT DEVELOPMENTS IN DISTANCE PROTACTION

The recont trend in the dovolopment of distance type 2.5.1 of protection has been by the application of on-line digital computer. They employ the predictive calculation of peak fault current and voltage from a number of compling values. Inc possibilities to emplore the avenues open for on-line digital computer ware explored by Barry J.Mann and I.F. Morrisson<sup>(23)</sup> in 1971. They have in their paper described the determination of the transmission line impedance from the peak fault current and voltage gapple values to determine the propence of a fault and have indicated their emerionees on a model transmission line followed by subsequent field tests. The scheme initially suffered from setbacks due to the prosence of d.c.transients but were successfully overcome by employing mimic impedances. Their analysis was done only for a faulted single phase line.

#### 2.5.2. Advantages of on-line digital Computors

The use of digital computers affords the following advantages in power system protection.

- (1) decreases fault clearing time

- (11) affords breaker failure protection

- (111) transient blocking

- (iv) out of stop blocking

- (v) out of step tripping

١

(vi) blocking tripping on generator dropping or load dropping.

In this context it must be hereover montioned that G.D.Rockfellor<sup>(29)</sup> in 1969 advocated the use of digital computers for protective relaying claiming that the hardware cost for a given lovel of capability has been dropping whilet the coftware cophistication and unowledge has been advancing thus making it ideally suited for the use of computers for protection wherever they are installed for data acquisition, data storage and monitoring. His paper was in the nature of a feasibility report which presented the requirements and logic of the computer to some and locate faults, the input quantities required, the speed of the computer, the storage capability and also it's reliability and economics. He also claimed that the computer speed in initiating tripping would be a man, of 4 ms for severe faults and a man of 10 ms for moderate or distant faults.

The LEEE Committee Report<sup>(35)</sup> amongst other things such as advocating colidatate relaying has also exphasised the use of digital computer to protective relaying and quoted the program developed by one utility to calculate and print out the impedances seen by relays during fault inception.

# 2.5.3. On Linn Dirital Computer Provention

A subsequent paper of Barry J. Eann<sup>(24)</sup> et al describes a digital computer programme for the protection of a 3 phase transmission line. The programme detects the prosence of a disturbance or fault, classifies the fault into one of the well known six types and using the impedance detection method described in their earlier paper clears the fault. The mode of operation is similar to an ordinary conventional distance relay in which the complex impedance of a faulted line is calculated and the value is used as the final criterion for cotabliching the presence or absence of a fault. The computer programe

dovoloped complete coquentially the three line currents and voltages at the rate of 40 samples/cycle and the interval of sampling is set by a 2 KEZeccillator. Each voltage sample is compared with the value of the provious comple and if the value difference is in excess of a specified telerance the counter of that particular point is incremented and the computer jumps into the fault determination subroutines. The aim of the subroutines is to determine which two of the R, Y, or B phaces or ground to be used to derive the equivalent single phace quantities are used for phase faults and voltages and zero sequence componented phace currents for ground faults. The authors claim that after final debugging the program was tested successfully for 1000 faults and no program indicated falcely R, Y or B or ground involvement in a fault.

G.D.Rockfeller in his subsequent paper<sup>(54)</sup> described the test results of an experimental general purpose process control digital computer, which provides high speed phase and ground distance fault protection of a 230 KV transmission line. The stored programme performs all the functions of relaying using the cutput of an analog to digital convertor which reads the instantaneous values of power system currents & voltages.

# 2.5.4. Use of Micro Programma and Mini Computera

A Report by CIGRE Committee Korking Group 01 of Study Committee No.34 (Protection) publiched in Jan. 1977<sup>(32)</sup> among other things states that recently, the heavy fall in prices on the semiconductor market and rapid progress in large ceals

intogration (LSI) tochnology has promoted further development in computer relaying. The relatively cheap microprocessors now available claim to offer economic solutions, provided as the committee report states that users are ready to pay additional capital for the improved performance which the computer relaying can give compared with conventional relays.

2.5.5. Advantages and Disedvantages of Micropressanors/Mini Computers

2.5.5.1. Significant advantages over conventional equipment is as follows :

- (1) greater sophistication of protective charactoristics

- (11) greater flexibility

- (111) self monitoring of computer hardware by diagnostic programo

- (iv) ability to validate input data and cater for missing or erroneous information.

- (v) suitable input/output interfaces to enable communication with other monitoring or control devices or the control ongineer

- (v1) high speed analogue input peripherals allow instantancous values of a.c. currents and voltages to be processed. The actual instantaneous values of coveral cycles of power frequency can be stored and printed out after a fault. This recording function provides a very valuable mans for fault analysis of post cortem review.

### 2.5.5.2 Mandrantagan

- (1) At present all inputs must be converted from analogue to digital form

- (11) computers are more difficult for usors to operate and maintain

(111) the hordware is subject to rapid obsolescence.

#### 2.5.6. Beguiromants of Computer baand Rolaving Schorag

Any computer based relaying scheme will have to meet very stringent requiremonts both as regards pover system protection and power system operation. The computer system if used as main protection will have to compose with the present analogue devices having operating times ranging from 1/2 to 14 cyclos. Novertholoss in the back up mode of protection. the speed will naturally be not because of the inhorent speed of operation of computers. Selectivity improvements will require better modelling of the characteristics of the protected power system plant and a larger tolorance to errors that may be present in the input information, if conventional instrument transformers are to be used as input cources to computer baced relaying systems. The technique of measurement, the algorithms used and the hierachy of the system must be such that a greater cortainty of operation is available as compared with what can bo achieved with modern analogue techniques and equipment. The total reliability of the computer system must be proved to be equal to or exceed the reliability of existing devices that perform similar duties. A margin in favour of the latter devices will automatically lead to a delicate balance between improvements as regards power system protection aspects and drawbacks

from the system operation point of view. The downtime of the computer must be kept down to a minimum. The quality of the hardware and it's compatability with power system environment must be assessed with the utmost care and the software must be thereughly checked to avoid programming errors or program degradation. The true cost of a computer based relay system is rather difficult to assess and especially so if the relaying tasks form only a part of the activities of a larger computer installation.

#### 2.5.7. Types of Computerised Versions

The present computing computer vorsions in the market are the mini computers and microprocessors.

# 2.5.8. Mini Computera

Mini computers have been available since the early part of 1960's and the recent ones are fast, with a cyclic time of the order of intensee, are powerful in calculation and are casy to handle because of their highly developed coftware. It's initial hardware cost is rather high and it can perform only one arithmetic or logic operation at a time. This makes it difficult even with sub microsecond memory cycles to match the speed of modern solid state relays that work in parallel. In order to prevent hardware failures it is absolutely necessary to provide for duplicate computer systems and as such it's cost is one order of magnitude higher than that of conventional relays.

#### 2.5.9. Micro Progossora

Micro processors have been on the markets for about four years. They have lower processing power than mini computers, but their lower cost permits them to be used as dedicated devices which work in parallel, each performing only a limited number

of functions. This system has the advantage of less complexity and therefore higher reliability.

#### 2.5.10. Solution to Relaving Problom

The mathematical treatment and the colution of relaying problems related to the protection of transmission lines/feeders depends to a large extent on whether the measurement is being carried out with the knowledge of only local quantities or whether information is available from other parts of the power system and or whether provision can be made to minimize the influence of unwanted frequency components in a signal without penalising the operating time and the characteristics of the computer to be used for the task.

The majority of the work dono on computers in the field of protection is on & fcodors. This is partly because of the relative simplicity of the equation describing the protected object.

The feeder protection based on inductance-resistance or impedance measurements can be achieved by a number of different techniques. R. Ponelot presented in his paper<sup>(33)</sup> a method employed in the formulation of a protection programme which is as follows :

- (1) Fault detection

- (11) Selection of faulty phases

- (111) Line 1, distance

- (1v) Disconnection

In 1975 A.M.Ranjbar and B.J.Cory of the Imperial College, london<sup>(30)</sup> proposed digital methods for the protection of long e.h.v. lines on transient faults and the method suggested is the accurate determination of the resistance and inductance of the line so that any number of harmonics on the current and voltage waveforms are eliminated. The authors claim that this method is suitable for the distance protection of transmission lines so as to clear the fault in the first cycle of it's occurrence and the method is claimed by M.Chamin & G. Ziegler<sup>(32)</sup> in the elimination of harmonics of any order by successive integration over particular time intervals.

In 1973, Hope and Unamahoshwaran<sup>(34)</sup> have also shown that the offects of harmonics can be totally eliminated by using Fourier Integral method using orthogonal pair of functions. Such as sine, cosine functions, odd and even square waves.

# 2.5.11 Other Application of Computer

The other important computer applications are that the result of state estimation programs can be used for automatic adjustment of relay settings to the actual load flow and infeed conditions and to mark splitting points for load loss minimisation. Automatic adjustment of operating settings to a new system configuration, for instance, after a major breakdown it will help maintain consitivity and improve coloctivity during notwork restoration.

#### 2.6 CONCLUSIONS

The trend in the development is to return to protective equipments similar to well known conventional equipments but with operation in a digital mode. Software packages have been

doveloped for nearly all protective functions, the majority boing, however, only a transposition of analogue relay funetions into digital form<sup>(32)</sup>. It must novortholess be emphasized that the application of computers to relaying tasks requires careful study of the power system environment with particular reference to the effects of electric and magnetic interference and to maintain programs of both software and hardware. Servicing has however been rendered eactor by relatively simple incorporation of solf checking features for fast and accurate fault To have a on-line digital computer exclusively for diagonosis. protective relaying will work out to be a very costly affair If a computer is installed for other purposes, then the functions of protective relaying may be achieved without any entra cost. The use of microprocessors and mini computers exclusively for protoctive releving is equally a costly affair particularly in our country where these have to be imported.

The following lines from A.R. Van C. Harrington's book<sup>(1)</sup> will sum up the development and trends in relaying. It is clear that the future of protective relays still holds an interesting challenge to engineers, since the technique of automatic protection has by no means settled down to a prodictable patterne in fact the mumber of uncolved problems seems to increase each year.

#### CHAPPER-III

#### CHARACTERISTICS OF DISPANCE RELAYS

#### 3.1. DISTANCE RELAYS AS COMPARATORS

All distance relays whether of the electromagnetic or of the static type are basically comparators and they operate when an electrical quantity of the protected circuit either changes from it's normal value or changes its ratio and or phase relation with respect to another electrical quantity of the circuit. The comparison is usually made in the relays by turning the electrical quantities into forces, torques, m.m.f's. or e.m.f's. proportional to the two quantities compared.

#### 3.2. CLASSIFICATION OF COMPARATORS

Rolay movements are distinctly associated with the characteristics of the relay and accordingly the movements are classified into two groups<sup>(1)</sup> -

1) Amplitudo Compratoro

Eg. a) Balancod boam rolay

- b) Induction disc element with shadod pole driving Engnots

- c) Opposed rectifier bridges

- d) Tracticotor rolays

# 11) Phase Comparators

- Eg. a) Induction cup rolay

- b) Induction dice element with watthetric type of driving magent

- (c) Induction dynamomotor

- (d) Polarisod roctifier bridges

- (o) Hall offect crystals

Babically an inhoront amplitudo comparator becomes a phase comparator and vice versa 1f the input quantities are changed to the sum and difference of the original two input quantities. A comprehensive treatment of this appet is given in reference cited He.(1).

# 5.3. CONVENTIONAL OR ELECTROMAGNETIC DISTANCE RELAYS-CHARACTERIS-

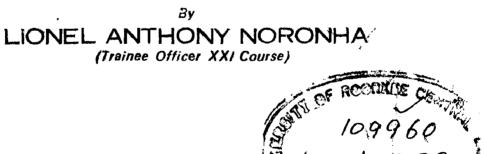

5.5.1. The two input quantities in these relays produces a torque in co-operation and the equation for the characteristic of the relay at the threshold of operation under stocky state conditions when plotted on a diagram where are are  $|\frac{B}{A}|$  Cos  $\phi$  and  $j|\frac{B}{A}|$  Sin  $\phi$  is of the form

$\mathbb{E} |A|^2 - \mathbb{E} |B|^2 + |A| |B| \cos(\phi - \phi) - \mathbb{E}^* = 0$

Whore A and B are the two electrical quantities being compared,

K and K' are scalar constants

R'' is a constant representing a bias which is a mechanical restraint.

Q to the phase angle between A and B

0 16 a prodotorminod fined angle which in those relays 10 the value of Q which provides manimum relay torque.

The above equation represents all the circular and straight line characteristics of electromagnetic distance relays, as obtained from two electrical input quantities.

It must however be montioned that R'' is a finite quantity in single quantity relays ( level detectors) but is made substantially zero for comparators. Thus we have for distance relays the above equation to be of the form<sup>(1)</sup>

Dividing throughout by R'A<sup>2</sup> to have

$$\frac{K}{R^{*}} - \left|\frac{B}{A}\right|^{2} + \left|\frac{A}{B}\right| \frac{Coo(0-0)}{R^{*}} = 0$$

Adding  $\left(\frac{\lambda}{2k'}\right)^2$  to both sides of the above equation and reerranging torms we have

$$\frac{|\frac{B}{A}|^2 - |\frac{B}{A}| \frac{Cos(0-0)}{R'} + \frac{1}{2R'}|^2}{R'}$$

$$= \frac{R}{R'} + \frac{1}{2R'}|^2$$

$$= \sqrt{\frac{1 + \sqrt{1 + \sqrt{1 + 1}}}{2R'}}$$

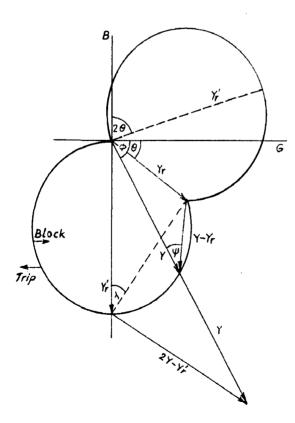

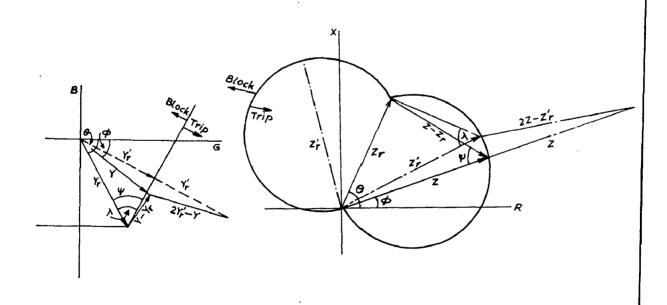

The above is the equation of a circle on a complex plane having  $|\frac{B}{A}|$  cos  $\phi$  and  $j|\frac{B}{A}|$  ain  $\phi$  as co-ordinates, the radius being  $\sqrt{\frac{1+\phi A}{2R^{\prime}}}$  and the centre at  $\frac{1}{2R^{\prime}}$  from the origin and at as angle 0 from the reference axis (Refer Fig.3.0). The axes have been designated as  $|\frac{B}{A}|_{p}$  and  $j|\frac{B}{A}|_{q}$  for  $|\frac{B}{A}|$  cos  $\phi$  and  $j|\frac{B}{A}|$  sin  $\phi$  respectively. In the cases of distance relays A will be current and B the voltage and the coordinates of the diagram will be  $|\frac{V}{A}|$  cos  $\phi$  and  $j|\frac{V}{A}|$  sin  $\phi$  or R and jX. The diagram in which the characteristic is plotted on R and JX as co-ordinates is called the impedance diagram or the complex impedance plane or 2-plane. Similarly if  $|\frac{\Lambda}{B}|$ is plotted the diagram has coordinates G and JB and the diament is called the Admittance diagram or Y-plane.

Admittance is the reciprocal of Impedance so that Y2-1 3.5.2. Honce if the locue of Z is a circle, then the inverse of it is a straight line parallol to the real axis (51). Again by inversion we have that if the locus is a circle on one plane, then the locus will also describe a circle on the inverse plane except in the special case when the cicle pasces through the origin in which case it will be a straight line. Thus from the general oquation of the electromagnetic distance relays we have their characteristics described by circles or straight lines, when drawn on the impodance or admittance plane. The relay operates if the tip of the impedance voctor on the impedance plane which 10 dotormined by the ratio of voltage and current applied to the rolay torminals is placed within the limit of the region of conplon plano limited by the rolay characteristic. When the tip of the impedance vector 18 moved to another part of the complex plane, the rolay does not operate if this part is outside the limits of the characteristic equation in question.

# 5.3.5. <u>Classification of cleatromanetic relays based on their</u> Charpetoristics

It is by considering the operating characteristics drawn in the complex plane we can distinguish or rather classify the following main types of electromagnetic distance relays.

29

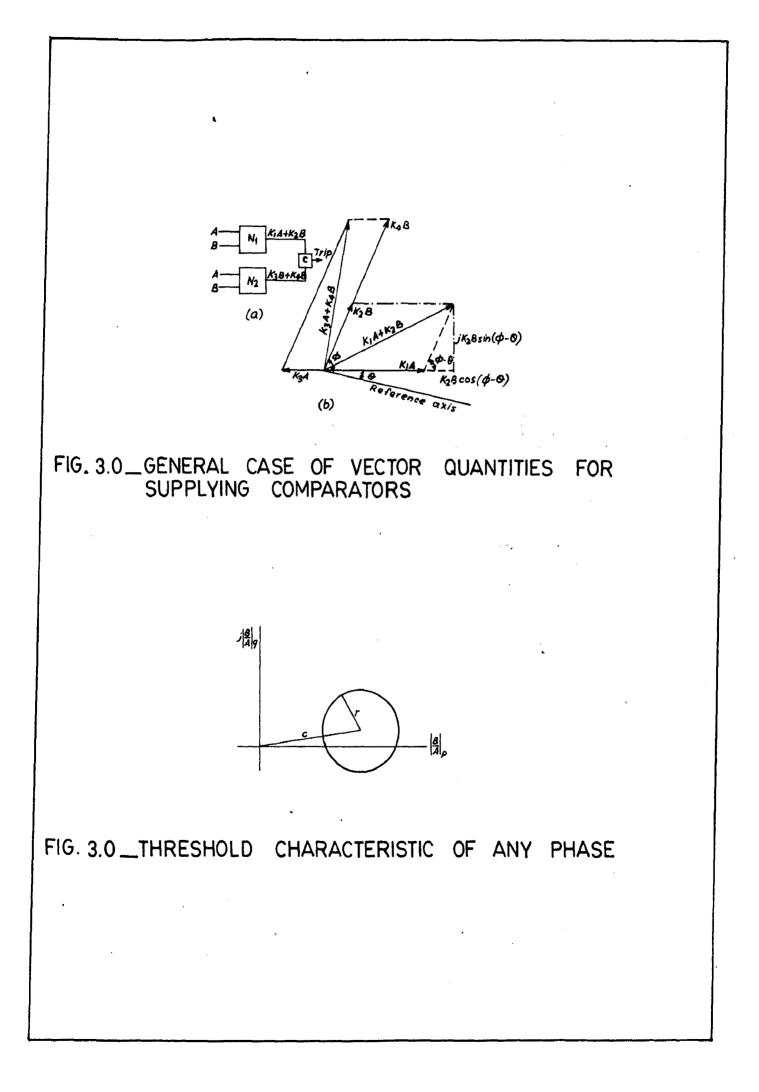

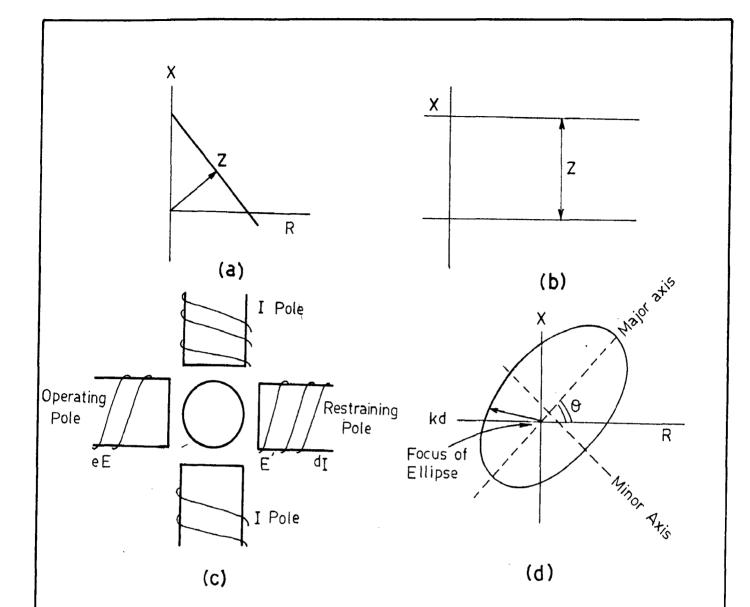

9.3.3.(1) Non directional distance relay with a circular Centre at characteristic with its origin called the 'Impedence Relay '. Thus in the balanced beam type, if we substitute the current I for A and the voltage V for B we have the relay to operate when

$$|z| < \frac{|\overline{K}|}{|\overline{K}|^2}$$

or  $|\overline{X}|^2 < |\overline{K}|$

$$|\overline{X}|^2 > |\overline{K}| |V|^2$$

The above is the equation of a circle with origin at contre and radius equal to  $10^{10}$  K .

Such a rolay is set to operate when the impodance measurvey the rolay is less than the impodance of the protected line AB rof. Fig. 3.1.

5.5.5.(11) Non directional distance may with a straight line characteristic parallel to the real axis or (R-axis) in the impodance plane called the ' Reactance Rolay.

In 1928, Mr. A.R. Van C. Marrington developed the first induction dise type distance rolay which had a reactive VA magnet instead of the usual potential restraining magnet, and subsequently in 1954 it was improved to the 4 pole induction cup inctead of an induction dise to design the first high speed reactance rolay. Two opposite poles had current windings, while the other two had opposed current and potential windings such that by substituting in the general characteristic equation (1),  $\Lambda = I$ ,  $B = V_0$ , K' = K''=0,  $\theta = 90$ . We have

$II^{2} + VI \cos (\phi - 90) = 0$   $II^{2} - VI \sin \phi = 0$   $II = V \sin \phi$   $\frac{V \sin \phi}{I} = K$ The relay operator when  $\frac{V \sin \phi}{I} < K$ i.o. when K < K. the oblaic setting

#### of the rolay

This equation gives a straight line characteristic Fig.3.2 3.3.3.(111) The directional distance relay with a circular characteristic, passing through the origin called the ' The relay' or the Admittance Relay.

This relay was developed in 1952 by Mr. A.R. Van. C. Warrington. The relay measures a component of admittance Y/0 and the relay is also known as the Angle Impedance relay in U.S.A.

In this roley a 4 pole induction cup had potential windinge or two opposite poles and or opposed current and potential windinge on the other two poles.

Thus in the general characteristic equation A = I, B = V, E,E<sup>(1)</sup> = O

> $-II'V^{2} + VI \cos(\phi - \theta) = 0$ or I Cos ( $\phi - \theta$ ) = II'V = 0  $\frac{I}{V} \cos(\phi - \theta) = II'$  $\frac{1}{V} \cos(\phi - \theta) = II'$

$$Z = \frac{1}{K^{2}} \cos\left(\phi - 0\right)$$

or  $2 = \mathbb{E} \cos(\phi - \theta)$

The above is the equation of a circle passing through the origin vide fig.3.3 The relay operator when Y cos ( $\phi - \theta$ ) > If or when Z < I cos ( $\phi - \theta$ ).

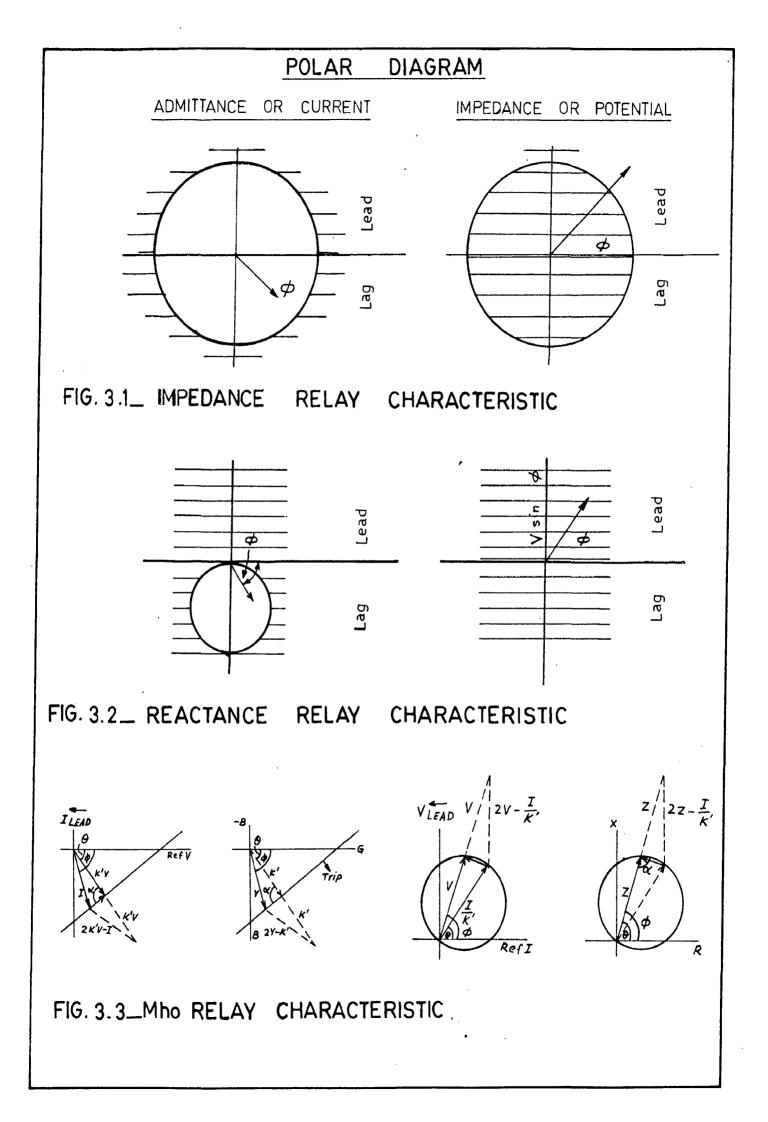

5.3.3(1v) Ohn Roley

This rolay measures a particular component of the Impedance 2/9. The threshold characteristic is a straight line on an impedance diagram fig. 3.4 i.e. in the general characteristic equation

$K^* = K^{**} = 0, \quad A = I, \quad B = V,$   $KI^2 - VI \cos(\phi - \theta) = 0$   $K = \frac{V}{I} \cos(\phi - \theta)$ or  $2\cos(\phi - \theta) = K$

The relay operator when  $2 \cos (\phi - 0) > R$ . It is seen from the above that the reactance relay is a particular case of the ohd relay when the relay measures  $2/90^{\circ}$ .

#### 9.3.3.(v) Offect Hhe Rolay

This is the term given to a roley whose circular characteristic in an impedance diagram does not pass through the origin, vide fig.3.5. This characteristic is obtained by adding current bias to a the roley. The bias provided an entry  $I^2$  term and the general equation would be of the form

$||I|^2 - ||V|^2 + |V| |I| \cos (\phi - 0) = 0$  and this represents a circl of radius  $r = \sqrt{(1 + 4)d(9)/2K'}$  and contro at a distance from the

origin given by  $C = \frac{1}{2K} - \frac{1}{0}$ . The offset the relay characteristic when plotted on an Admittance diagram is again a circle but its radius and distance of the centre from the origin are inversely related to these of the circle drawn on an impedance diagram.

The off cot of the impedance circle is secured as described above by adding to the line potential a biassing potential  $IZ_{b^{p}}$  proportional to the current, which has the effect of noving the characteristic impedance circle bodily by an amount  $IZ_{b^{*}}$ . Thus in the mac rolay characteristic substituting (V +IZ<sub>b</sub>) for V we have

-  $\mathbb{R}^{\bullet}$   $(\mathbb{V} + \mathbb{I}\mathbb{Z}_{b})^{2} \Rightarrow (\mathbb{V} + \mathbb{I}\mathbb{Z}_{b}) \mathbb{I} \cos (\phi - \phi) = 0$

Dividing throughout by I<sup>2</sup> we have

$$-\pi_{*}(\frac{1}{\Lambda_{5}} + \frac{1}{5\Lambda_{12}}) + \frac{1}{2_{5}^{p}}) + (\frac{1}{\Lambda_{1}} + \frac{1}{12}) + (\frac{1}{\Lambda_{1}} + \frac{1}{12}) \cos(\phi-0)$$

$$- K^{*} (Z^{2} + 2ZZ_{b} + 2Z_{b}^{2}) + (Z + Z_{b}) \cos (0 - 0) = 0$$

$$- K^{*} (Z + Z_{b})^{2} + (Z + Z_{b}) \cos (0 - 0) = 0$$

$$(Z + Z_{b}) \left[ -K^{*} (Z + Z_{b}) + \cos (0 - 0) \right] = 0$$

$$K^{*} (Z + Z_{b}) + \cos (0 - 0) = 0$$

$$K^{*} (Z + Z_{b}) = \frac{\cos (0 - 0)}{K^{*}}$$

$$Z + Z_{b} = \frac{\cos (0 - 0)}{K^{*}} - Z_{b}$$

This shows the characteristic equation is similar to that of the Who relay encopt neved by the impedance 2, ref.Fig.3.5. The biassing potential is obtained by introducing a reactor in the current circuit.

-2.

#### 3.3.4. Boncial Distance Rolay Characteristics

The following are various ways in which the standard impedance, admittance and reactance can be modified. These modifications were done so that the distance relays develop better telerance to fault resistance, and less susceptibility to power swings.

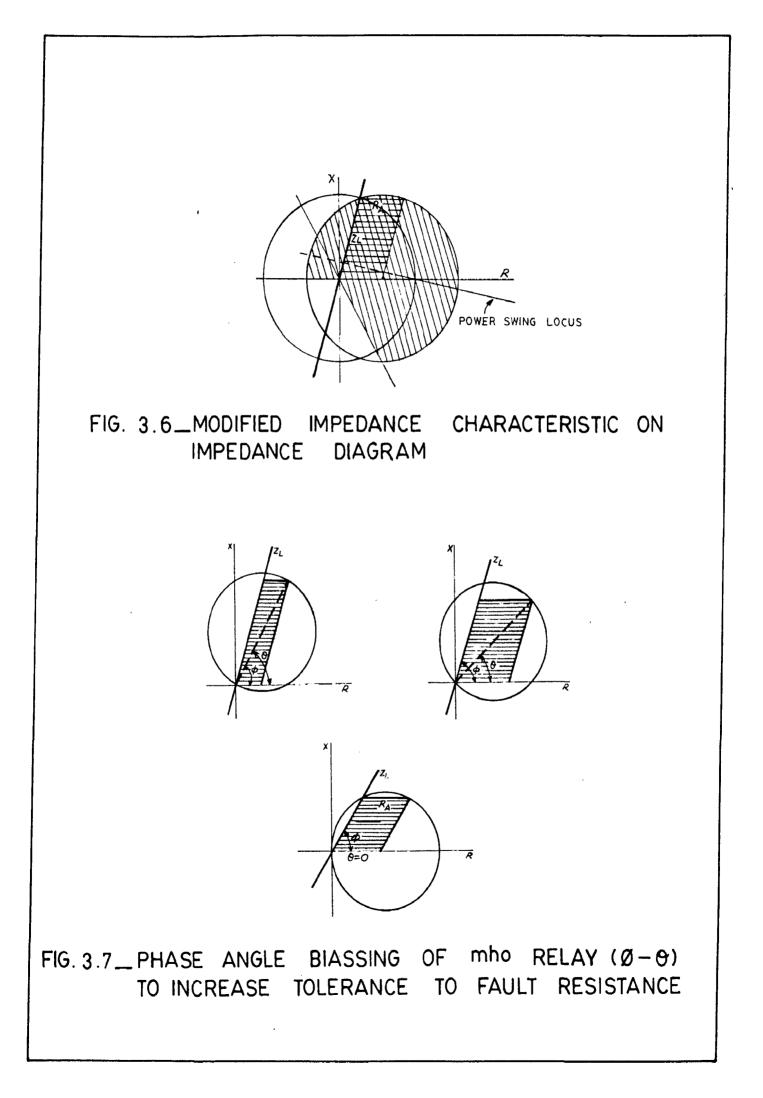

## 3.3.4.(1) Hedifind Incedance Roley

The standard impodence rolay characteristic can be neved outwards along the R-axis by current biassing the potential circuit with the Ir drop across a resistor so that it has more telerance for fault resistance as shown in figure 3.6. The maximum possible offset is when the circle passes through the origin. Biassing may also be done in the -X direction as well as in the R-direction so that a bigger impedance circle results which tends towards a reactance characteristic. Thus in the general charactoristics equation of an Japedance relay, introducing the Ir bias changes the equation to

> $|\mathbf{RI}|_{5} - |\mathbf{A} + \mathbf{IL}|_{5} = 0$  $|\mathbf{RI}|_{5} - |\mathbf{A} + \mathbf{IL}|_{5} = 0$

Dividing throughout by - I<sup>2</sup> to have

$Z^2 + 2Zr \cos \phi - R^2 + \gamma^2 = 0$

The above is the equation of a circle passing through the origin with its centre on the R-axis and distance rfrom the origin if r = R obset.

### 3.3.4.(11) Conductance Rolay

By suivalling the she rolay characteristic in the loading direction, clockwise in the impedance diagram its telerance to fault resistance can be increased with less vulnorability to power swings in the modified impedance rolay. In the limiting position along the R-axis it becomes a " conductance Rolay". In the conductance rolay there is no change in the balance equation from the she rolay, i.e.  $Z = K \cos(\phi - \theta)$  except that  $\theta$  is now zero instead of the normal value of  $60^{\circ}$ , but the obmic setting of the relay has to be multiplied by  $Z/(\cos \phi)$  so that the impedance cycle will still pass through the ohmic. value  $2/\phi$ . Refore Fig.3.7 for its characteristic. 3.3.5. Switched Distance Rolaya

Theoretically, four fault detoctors and 18 measuring units are required for providing three time distance stope for the ten variaties of phase to phase and phase to ground faults. The cost and the space required for installing such largo units has been reduced in practice by using measuring units for more than one purpose.

The number of measuring units is cometimes reduced to three by using the same set for phase and ground faults. The distance measuring units in modern schemes of this type are normally connected for phase faults, that is with dolta potential and delta current and are switched to we connections only when a single phase to ground fault occurs. A scheme of this type

provides immediate clearing of inter phase faults and a small delay in clearing single phase to ground faults. Movetheless, the economy of using a single measuring unit has to be balanced against the following effects.

- (a) time delay required for the fault detectors to access the type of fault

- (b) complete loss of protection if the switching contacts fail

- (c) possible wrong tripping if the type of fault changes during operation of the rolay ( effect of wind upon arc)

- (d) inaccuracy due to differing phase impodance ( offect of unsymmetrical transposition of conductors)

- (c) possible reduction in reliability due to dependence upon a number of contacts in series.

The Delta-Wye switching is used for distance relays of the impedance or admittance type with the timing unit started by a poly phase over current or who type fault detector for phase faults and by a residual current or power relay on ground faults.

The inter phase switching consists of one unit for phase faults and one for ground faults, these units being switched to the appropriate phase or phase pair by the fault detectors. Thus the phase and ground protection are two separate schemes.

Poly phase distance relays are no doubt ideal for protecting a polyphase system than single phase relays, but so far it has not been possible to devise the circuitry for obtaining uniform performance on all types of faults<sup>(1)</sup>, though considerable offerts have been made in this direction by Gupta<sup>(27)</sup>.

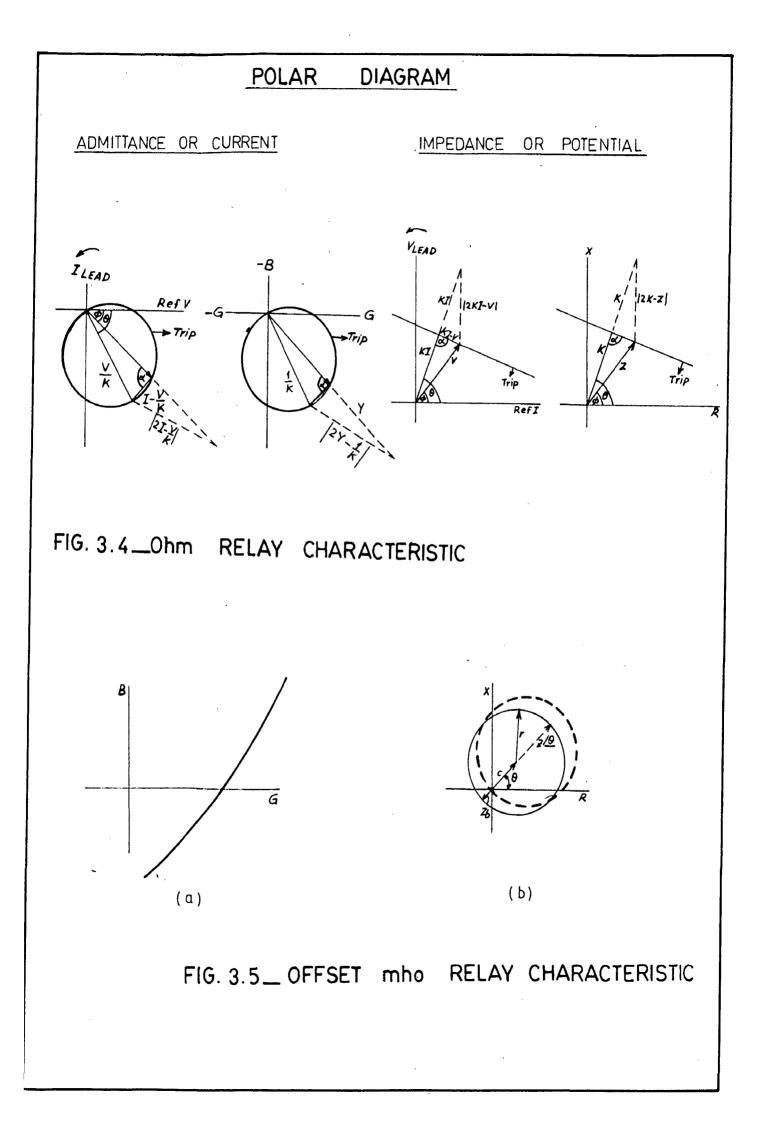

#### 3.4. CHARACTERISTICS OF STATIC R RIANS

3.4.4. The measurement of impedance, reactance or angle admittanco in static rolays is dons by the comparison of two different input combinations of current and voltage which result in circular or straight line characteristics as explained in the earlier part of this chapter under electromagetic relays. However, in a static rolay the two input quantities must be similar that is two currents or two voltages because they are not electrically separate as in the case of electromagnetic relays. As such in a voltage comparator the current is turned into a voltage by passing it through an impodance  $Z_{\rm p} / \Theta$  which is a replica of the impodance of the protocted line soction. Here the line voltage is compared with the voltage drop across the replica impodanco. In the current comparator the current is derived from the voltage by connecting the replica impedance in series with it giving a current V/Zp which is compared with the line current 1. The use of the replica impedance is not only convenient but pormits fast tripping since it climinates error due to transients in the fault current, and is due to the fact that the fault current passing through the line impedance produces the same voltage wave form as the secondary current passing through the replica impedance Thus any transionts that appear in the primary current appear oqually in the voltage V and IZ, and thus cancell out their offoct: on the impedance measurement.

3.4.2. Both amplitudo and phase comparators have been used. An amplitude comprator compares only the magnitudes of the input

signals and ignores their phase angle. The phase comparator on the other hand responds only to the phase relation between the two input quantities irrespective of their magnitudes. For linear and circular characteristics it operates when  $90^{\circ} > + > -90^{\circ}$ where + is the angle between the two inputs.

3.4.3. The characteristics of the static distance relays are as in the case of electromagnetic relays plotted on the Lapodance diagram (BandjX axes) and Admittance diagram (C and jB axes).

The characteristic is either a straight line passing through the origin or a circle with the origin at the contre dopending upon whether a phase comparison or an amplitude comparison is made and further as to whether the characteristic is plotted on an Impedance diagram or on an Admittance diagram. A circular characteristic not passing through the origin of one diagram is a reciprocal circle on the other diagram that is the diatance of each point on one circle is the reciprocal of the diatance from the origin of the corresponding on the other circle. Furthermore each point will be lagging as much the resistance axis as the corresponding point on the other circle was leading the conductance axis and vice versa.

3.4.5. In 1954, Borgsoth<sup>(12)</sup> described the means of obtaining distance rolay characteristic such as reactance, the, elliptical ote. on the impedance plane using electronic relays and using the principle of phase comparators.

3.4.6. It was however in 1960, that C.G. Dowsy<sup>(44)</sup> et al emplained as to how the mechanical complexity of electromagnetic

rolays could be replaced by transistorised circuitry to perform the desired mechanical functions. The logic symbols of ADD, EDT, OR have also been explained and block diagrams for those functions as applicable to phase comparison principle of comparing the instantaneous directions of current flow at opposite ands of a transmission line using a pilot channel is not out therein. The successful results of laboratory and field tests has been given in the companion paper to the above vide S.H. Herewitz et al<sup>(45)</sup>.

3.4.7. In 1963, C.G. Deway of  $a1^{(20)}$  described the necessary principles and circuitry for directional comparison relaying and static relaying equipment for transmission lines with mhe distance unit circuits for the time delay unit on pick up and drop out along with the pulse stretcher circuit to convert the pulse output. The successful application of this scheme was reported in their companion paper <sup>(46)</sup> as testified by field and laboratory tests.

3.4.8. In 1968, L. Jackson of al<sup>(47)</sup> reported the ease with which transistor comparators for distance relays can be designed for high speed operation taking into consideration the overall position and integrity of operation. It is reported therein that the operating speed must be defined over the whole working range of the relay and that neither, the speed nor the measuring accuracy should be unduly affected by the severe transients generated by modern e.h.v. net works. The advantages of transistor comparator which affords greater freedom of design for specific laws of operation and/or characteristics embracing freedom of

dosign in both static and dynamic charactoristics has been exceptified. The basically different methods of obtaining useful charactoristics from a comparator circuit is confined to the following :

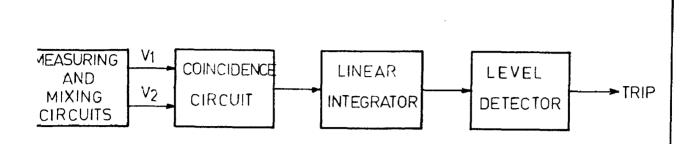

(1) block instantaneous comparison in which the duration of polarity coincidence determines the output. The tripping criterion is that the duration of the first coincidence should exceed a specified time usually one quarter of a cycle of the power frequency period.

(11) Block average comparison, a dovolopment of the above in which the duration of polarity coincidence is measured on both the half cycles of the input signals and the averaging value is determined in an integrating circuit, a trip signal being produced if a specified average value is maintained for more than the prescribed duration.

(iii) pulse comparison in which the polarity of one signal is measured during a short interval in the cycle of the second signal, usually but not necessarily at the latter's peak.

The relative monits of practical comparators of each categary have been compared by considering phase angle comparators since practical comparators under (iii) above have been realised only as phase angle comparators  $(^{47})$ . A comparison reveals that the everall characteristics of circle and straight lines in the complex plane can be easily obtained by all three of the above cited mothods with basically no difference in the steady state. However their comparison in their dynamic static reveals that (i) and

(111) are inherently susceptible to system transients and other opurious signals by virtue of their mear instantaneous operation and unloss all unwanted surges and transients are removed effectivoly, the measuring accuracy cannot be maintained under dynamic conditions without gacrificing operating spood. The block avorage comparator as described in (11) however has inherent transient free characteristics and its operating time is significantly unaffocted by the degree of d.c. offset transient in the input signals. This has been confirmed by the author after extensive laboratory tests on a proto typo relay that was developed. The basic block diagram of the same is as shown in Fig. 3.8. The rolay performance with a d.c. offset in one input only to the comparator and subsequently with d.c. offsets in both inputs were considered on the practical prototypo relay for different source-system impedance ratios. Their performance curves plotted as (1:) relay accuracy against syste m impodance ratio is almost a straight line except year the boundary conditions where there is a marked fall in accuracy.

(ii) rolay operating time against rolay accuracy which is almost a straight line. Accordingly the authors have spelt out the specification of the design requirements for the block average comparators as -

- i) measuring accuracy to be maintained over the full working range

- 11) timing charactoristic- should be of the definite minimum type for all faults within the protected some with an operating time of the order of 1 cycle of power froquency being considerably desirable.

mon man in

11) stability - should have inhoront resistance to high applitudo, short duration, system generated surges both with regard to maloperation and to surge damage.

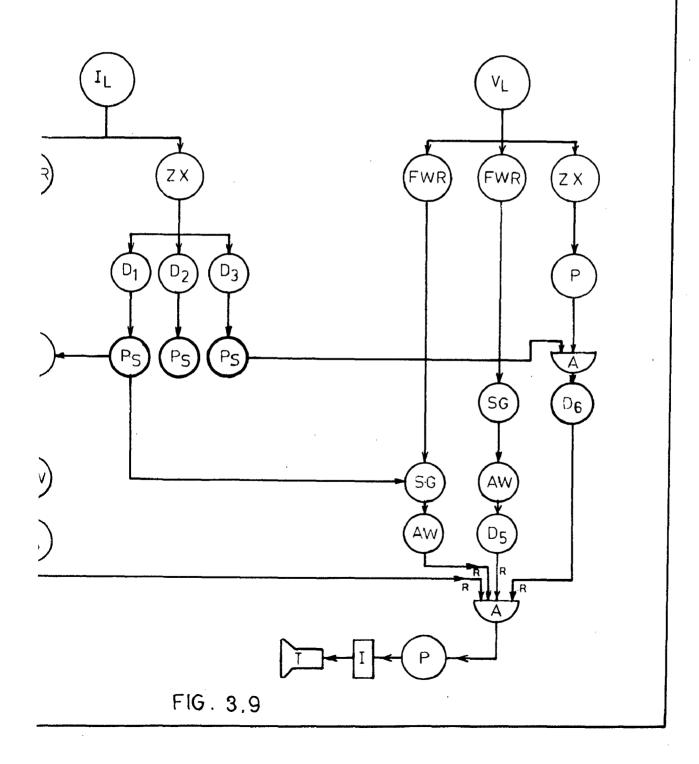

3.4.9. In the same year, P.G. Medaven<sup>(48)</sup> described in his paper a compliant technique developed which allows a comparison of instantaneous values derived at different instants of time, thereby dispensing with the need to phase shift and mix signals derived from the primary fine quantities. However the process of elimination of phase shifting requires a greater degree of sophistication in the relay circuitry. But it achieves on the other hand, a saving in both space and cost. The sampling period is of the order of 50 micro means in each half cycle and have been classified by the author under the following headings:

- i) those taking the zero crossing of line current I<sub>L</sub> as time reference and referred to as current polarised relays.

- ii) those taking the zero crossing of V<sub>L</sub> as time reference and referred to as voltage polarised relays.

The block diagram of the current polarised rolay is as shown in fig. 3.9. In this if the current and voltage signals are interchanged, the voltage polarised rolay is obtained.

| ZX | ۰   | Zoro crossing detector | S0 - | Sampling rate                      |

|----|-----|------------------------|------|------------------------------------|

| D  |     | Dolay Unit             | АБ - | Amplitudo/Pulse width<br>convertor |

| P  | ° 🗰 | Pulso unit             | 1 -  | Integrator and loval               |

| P  | -   | Pulce campling unit    |      | dotoctor                           |

| 9  |     |                        | T.   | Thyristor                          |

Here 2% Entocts both the +vo and -vo going seres and to avoid duplication of the circuits after the measuring gates the signals are rectified. The amplitude/ pulse width convertor produces a pulse length propertional to the amplitude of the sampled quantity at the instant of sampling. Signals represented by 'R' are restraining signals and signal 'C' is the operating signal. The output produces a zero pulse and fires a thyristor circuit or it can be fed to a level detector and integrator and thence to the thyristor. The relaying scheme therefore requires -

- 1) gere crossing dotector

- 11) dolay or pulso unit

- 111) measuring unit

iv) AND gate

Maloperation due to voltage spikes has been reported in the performance of these relays. The relay without an integrator has a tendency to over shoot which has been stated to be about 15% but this has been considerably reduced by having the integrator in the circuit.

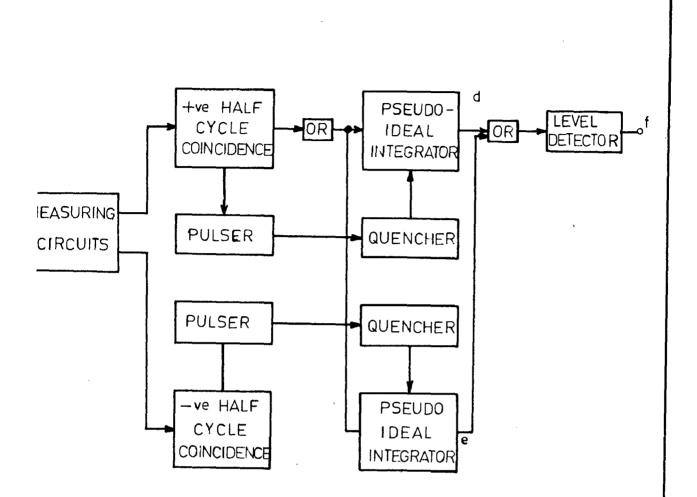

3.4.10. In 1969, K.S. Eshta et al<sup>(49)</sup> described a new type of phase comparator which operates on double the normal angular limits and which strikes a particularly fine balance between static single and dual phase comparator during transient conditions. The rolay has an angular over reach of less than 5% and an operating time of about 3/4 cycle. The rolay particularly overcomes the over-reach/underreach of static rolays during transient conditions, the nature of the over-reach depending upon the polarity of the d.c. offset. Dual comparators overcome the

FIG. 3.10

.

effoct but at the cost of operating time. The block diagram of the scheme is as shown in fig.3.10. The operating principle is that phase comparison is carried out both during the eve and -ve half cycles and the resulting coincidence outputs are OR gated. The output of the OR gate is integrated and fod to a level detector and the quenching of the integrator is carried out at the ond of each pair of coincidence measurements. An arrangoment of this kind with a single integrator will both overreach and undor-reach depending upon the polarity of the d.c. offset and the sequence of phase measurements. The degree of overreach/undorroach is a function of the X/R ratio of the line and the amount of d.c. offsat. The under reach is avoided by using two intogrators and quanchors as shown. The test values of the overreach/under reach values tabulated indicates that the angular over reach is loss than 5% even in the worst case of X/R ratio oqual to unity.

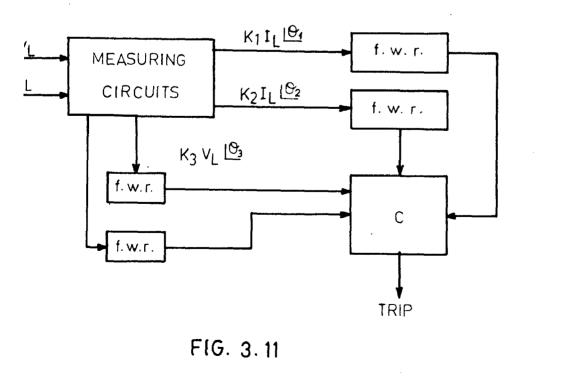

3.4.11. In 1970, H.F. Khincha<sup>(4C)</sup> of al described the dovolopment of amplitude comparator techniques based on the instantaneous 'comparison of the amplitude of the signals derived from primary line quantities. The block diagram of the scheme is as shown in fig.3.11. The scheme allows all the conventional and opecial characteristics of the distance relays by suitable adjustment of the constants in the relay circuitry.

II. Remamoorthy et al<sup>(50)</sup> reported in 1970 the new dovelopments in amplitude and phase comparison techniques for distance relaying with the amplitude comparator having its bace of operation on the integrals of the rectified voltage and current waveform

obtained at the end of each half cycle. The relay operation is shown to be immune to high frequency components and is less dependent on d.c. transient offects. Operational amplifiers have been used and the author has suggested that the use of I.C.'s will make the rolay circuits more compact and economical.

## 3.4.12 Types of Static Distance Relays

These are classified by their characteristics.

#### 3.4.12(1) <u>Directional Relay</u>

This is strictly not a distance measuring rolay but has been included as such (a) to complete the mathematical pattern since it is the dual of the impedance relay (b) because it is required forceme types of distance pelays which are not inherently directional.

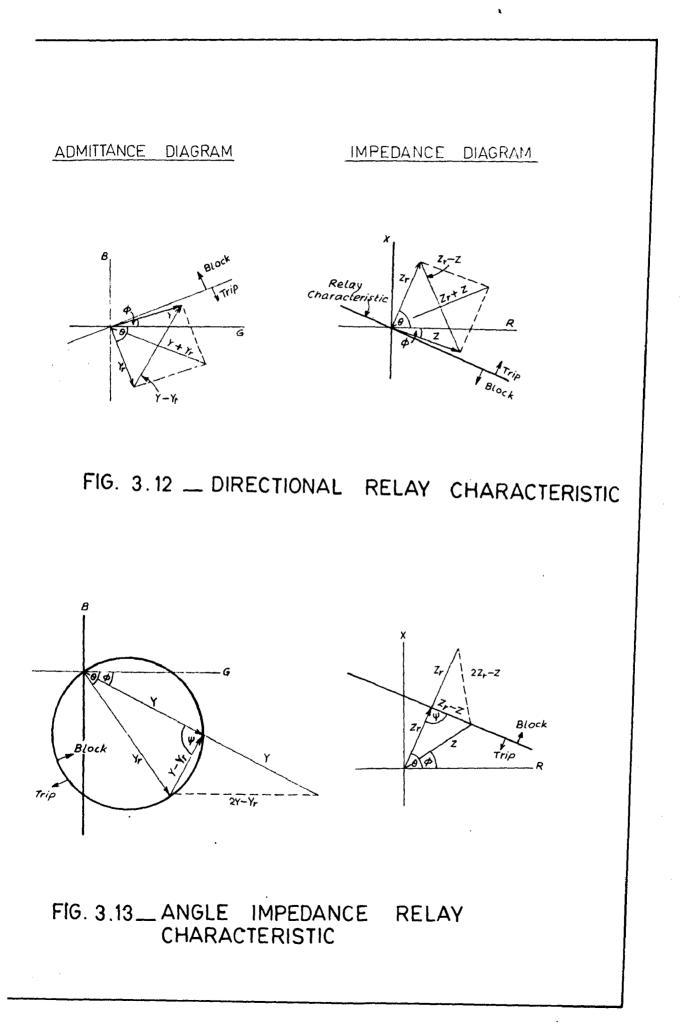

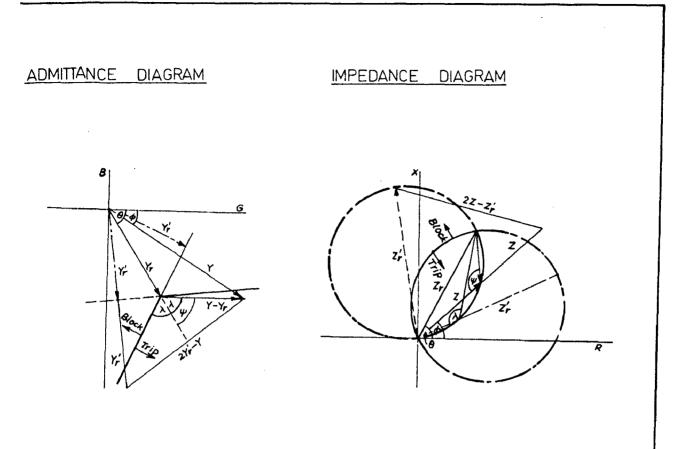

Its characteristic is a straight line passing through the origin on either the impedance or Admittance diagrams. The characteristic results from comparing the voltage inputs V and  $IZ_{p}$  in a phase comparator, and is also equally obtained by comparing their sum and difference namely ( $V + IZ_{p}$ ) and (V- $IZ_{p}$ ) in an amplitude comparator (Ref. Fig.3.12.) In (a) and (b) Phase Comparator trips when  $90^{\circ} > (\phi - \theta) > -90^{\circ}$  and Amplitude Comparator in (a) trips when  $|Z_{p}+Z| > |Z_{p}-Z|$  and in (b) when  $|Y_{p}+Y| > |Y_{p}-Y|$ .

#### 3.4.12(11) Anglo Impedance Relay

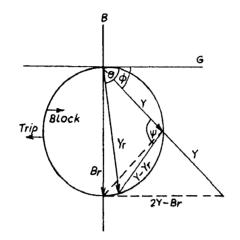

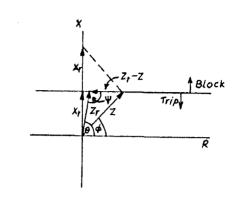

It's characteristic on an impedance diagram is offect from the origin by blasing the voltage drop across the replica impedance. Refer Fig.3.13.

In a phase comparator, the relay trips when  $90^{\circ} > 4 > -90^{\circ}$  where  $\Rightarrow \text{ Ang } \left[ \frac{8_{\text{F}}}{2_{\text{F}}} - 2 \right]$ . In an amplitude comparator the relay trips when  $|2| > |22_{\text{F}} - 2|$ 1.0.  $8^{2} > 4 8_{\text{F}}^{2} - 4 8_{\text{F}} 2 + 2^{2}$ 1.0.  $8_{\text{F}}^{2} (2_{\text{F}} - 3) > 0$   $2_{\text{F}} \left[ 2_{\text{F}} - \frac{V}{4} \operatorname{Cop} (\phi - 0) \right] > 0$ or  $^{\circ} \text{I2}_{\text{F}} \left[ \text{I2}_{\text{F}} - V \operatorname{Cos} (\phi - 0) \right] > 0$

On an admittance diagram the characteristic is a circle passing through the origin whose diameter is equal in length to the reciprocal of the perpendicular from the impedence characteristic to the origin and to cause tripping the head of theadmittance vector must extend outside the circle.

This characteristic is also obtained in the polarisod current rolay under sampled distance rolays<sup>(47)</sup> by  $I_D$  and  $V_L$  at  $\theta^0$  after current seco.

#### 5.24.12(111) Renetance Rolay

This is a particular case of the Angle Impedance Relay in which the reactive component of the impedance is measured. It's characteristic is parallel to the resistance and on the impedance diagram and a circle passing through the origin on the Admittance diagram. Refer Fig. 3.14. ADMITTANCE DIAGRAM

IMPEDANCE DIAGRAM

FIG. 3.14\_REACTANCE RELAY

$z_{r}^{p}$   $z_{r}^{p}$

FIG. 3.15\_\_RESTRICTED REACTANCE RELAY

In the phase comparator the quantity  $IZ_{p}$  is compared with  $(IZ_{p}-V)$  and the relay trips when n > (++0) > 0 in both the above diagrams. Here 0 is the phase angle of the replica impedance  $Z_{p}$ . If  $Z_{p}$  whre a pure reactance then + would be  $90^{\circ}$ .

In the applitude comparator on the Lapedance Diagram the relay trips when  $|\mathcal{Z}| < |\mathcal{Z}L_{F}-\mathcal{Z}|$  and the voltage inputs to the comparator are V and  $2IZ_{F} - 2 IR_{F}-V$  where  $R_{F}$  is made equal to the resistance of the replica impedance, thus leaving it's reactive component  $X_{F}$  only, and in the case of the Admittance diagram it trips when  $|\mathcal{Z}Y-B_{F}| > |B_{F}|$ . This characteristic is also obtained in the current polarised relay under sampled distance relays<sup>(47)</sup> by compling  $I_{L}$  and  $V_{L}$  at different intervals of time i.e.  $V_{L}$  at 0 = 0 and  $I_{L}$  at 0 = 4

3.4.12 (1v) Restricted Resectance Roley

The characteristic on the impedance diagram is a straight line bent at a prodeterminedpoint. On the admittance diagram the characteristic is a couple of circular area. Ref. Fig. 3.15.

The inpute to this relay are similar to those of the normal reactance relay and the tripping criterion is similar except that the limiting values of  $\psi$  are  $\geq \lambda$  instead of  $\pm 90^{\circ}$ .

In a phase comparator  $IZ_{p}$  is compared with  $(IZ_{p}-V)$  and in the mplitude comparator the inputs are |V| and  $|ZIZ_{p}-V|$ . 9.4.12(v) <u>impedence Rolay</u>

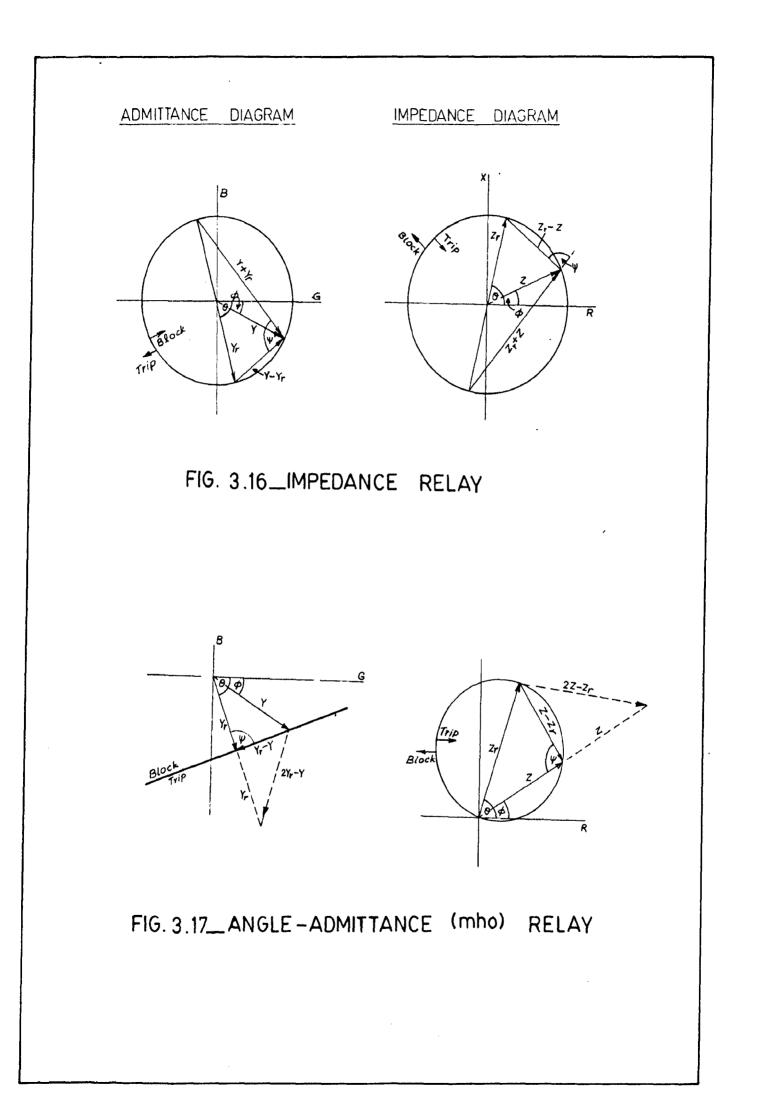

It's characteristic is a circle at the origin on both the Impodence and Admittance diagrams. Ref. Fig. 3.16.

Impodence is inherently an amplitude comparison of current and voltage and the rolay trips when  $|Z| < |Z_{ge}|$  so that the impute required for an amplitude comparator are V and  $IZ_{ge}$ . The phase comparator presents contain difficulties and as such is not used in distance relays.<sup>(19)</sup>

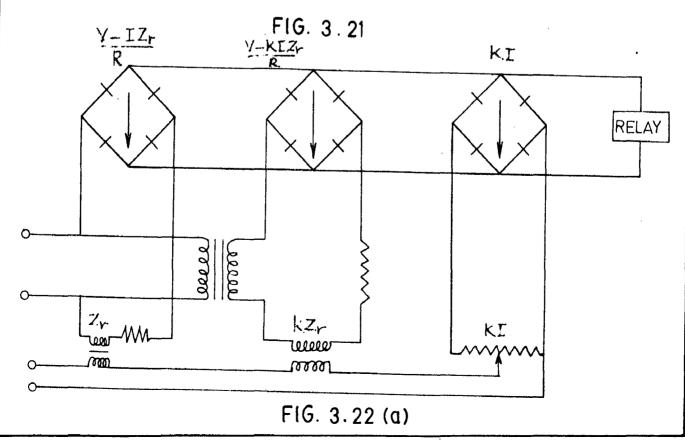

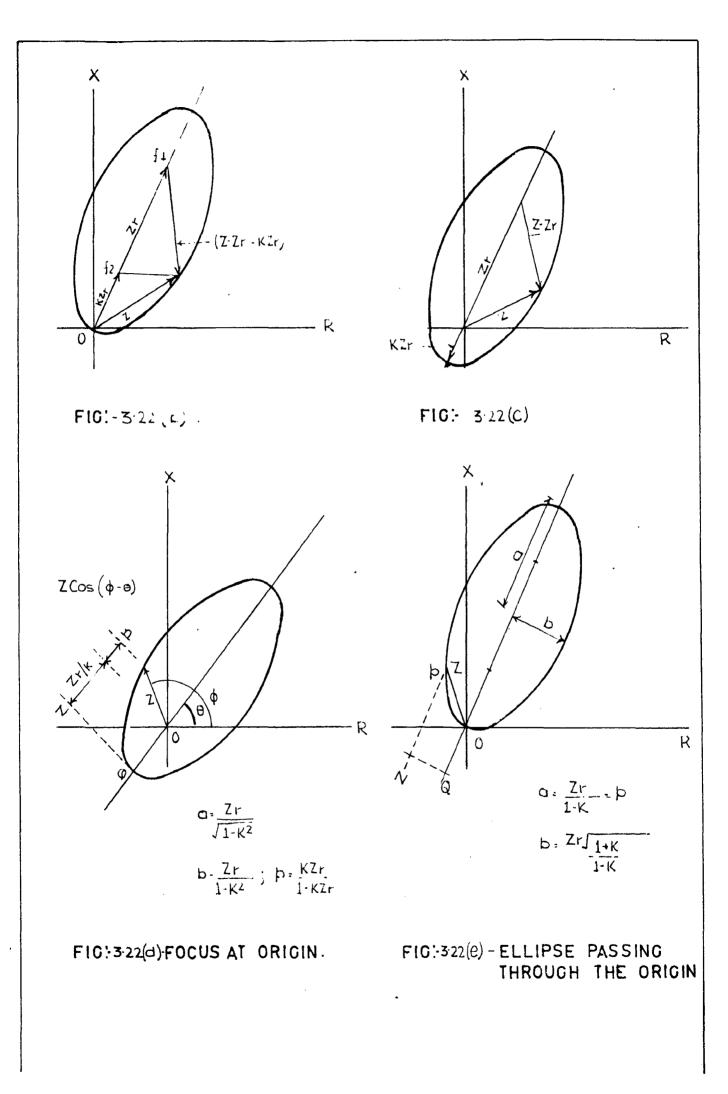

#### 3.4.12(vi) Anglo Admittanco or Mho Relay

On an admittance diagram the characteristic is a straight line effect from the origin in the lagging quadrant as shown Refer Fig.3.17. On the Impedance diagram it is a circle passing through the origin as shown and is the inverse of the angle impedance rolay. Refer. 3.17. The mass characteristics can be conveniently obtained with both the phase and the amplitude comparators. The inputs in the phase comparator are  $(IS_{\rm E}-V)$  and V and the rolay trips when  $90^{\circ} > \psi > -90^{\circ}$ . A product device operators when

$V \left[ IZ_r \cos (\phi - \theta) - V \right] > 0$  where  $\phi$  is the angle between V and I,  $\theta$  is the phase angle of  $Z_r$ .

Rearranging the above terms we have the relay to operate when  $\mathbb{Z} < \mathbb{Z}_{\mathbf{r}}$  code (0, -0). The impute in the amplitude comparator are  $| \mathbb{I}\mathbb{Z}_{\mathbf{r}} |$  operating and  $| \mathbb{2}\mathbb{V}-\mathbb{I}\mathbb{E}_{\mathbf{r}} |$  restraining and the relay trips when  $| \mathbb{2}\mathbb{Z}-\mathbb{Z}_{\mathbf{r}} | < |\mathbb{Z}_{\mathbf{r}} |$ . This characteristic is also obtained in the voltage polarised relays under campled distance relays<sup>(47)</sup> by campling  $\mathbb{V}_{\mathbf{L}}$  and  $\mathbb{I}_{\mathbf{L}}$  at 0<sup>o</sup> after voltage core.

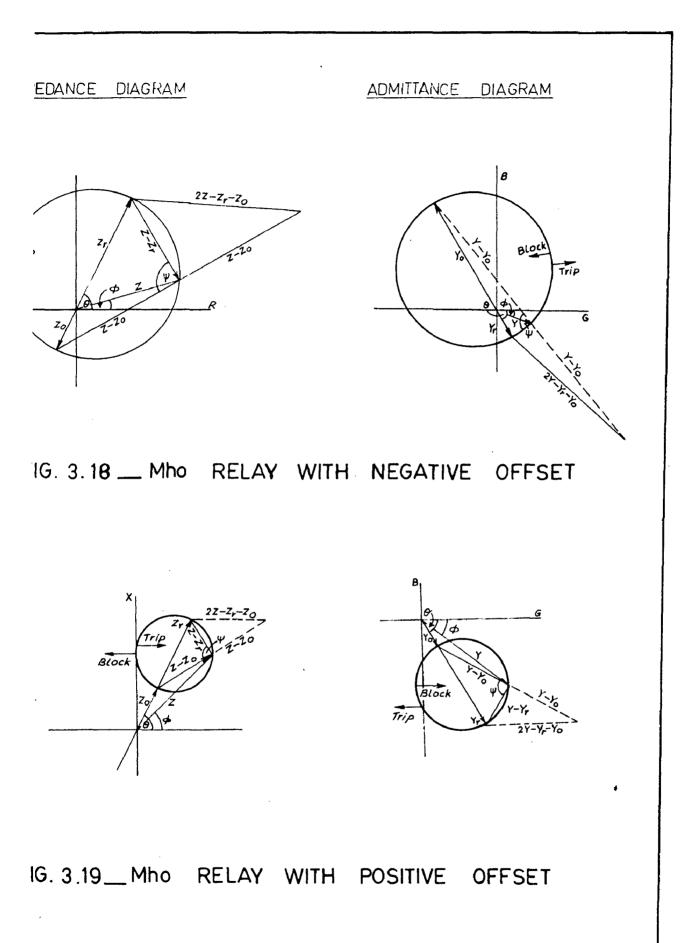

#### 9.4.12(vii) Offcot Who Rolay

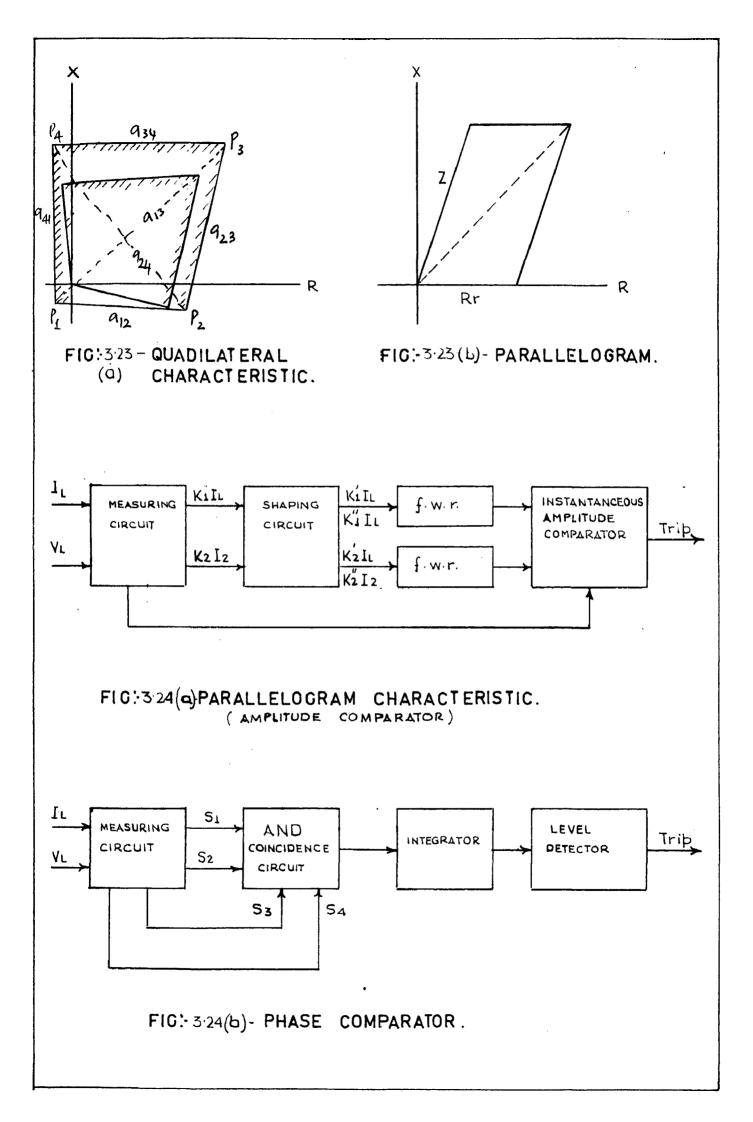

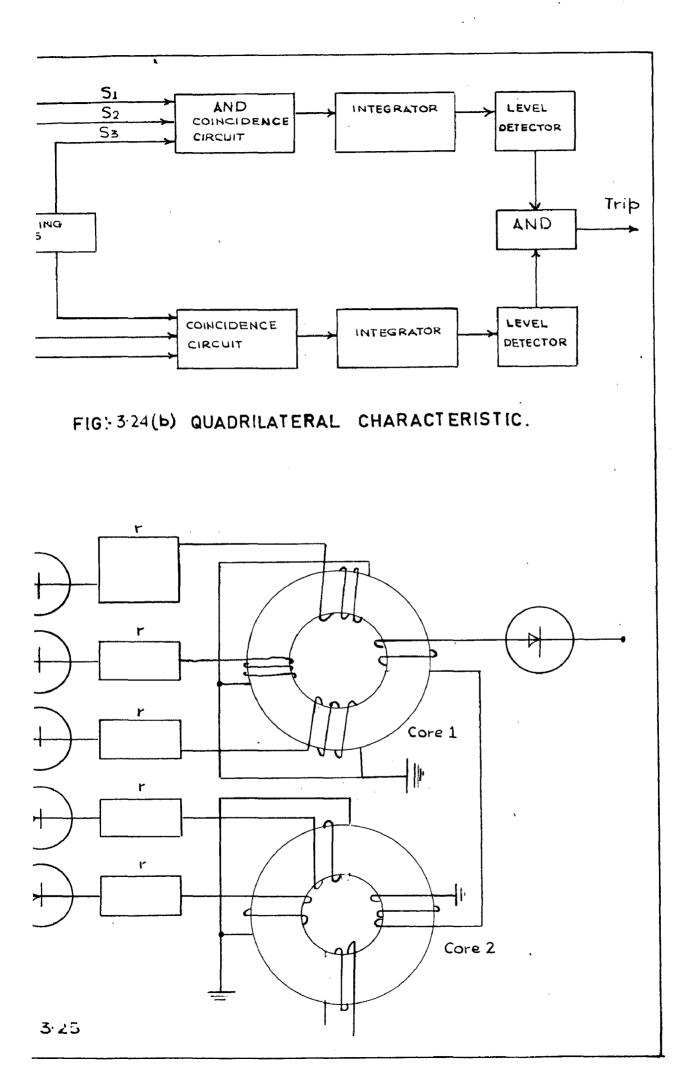

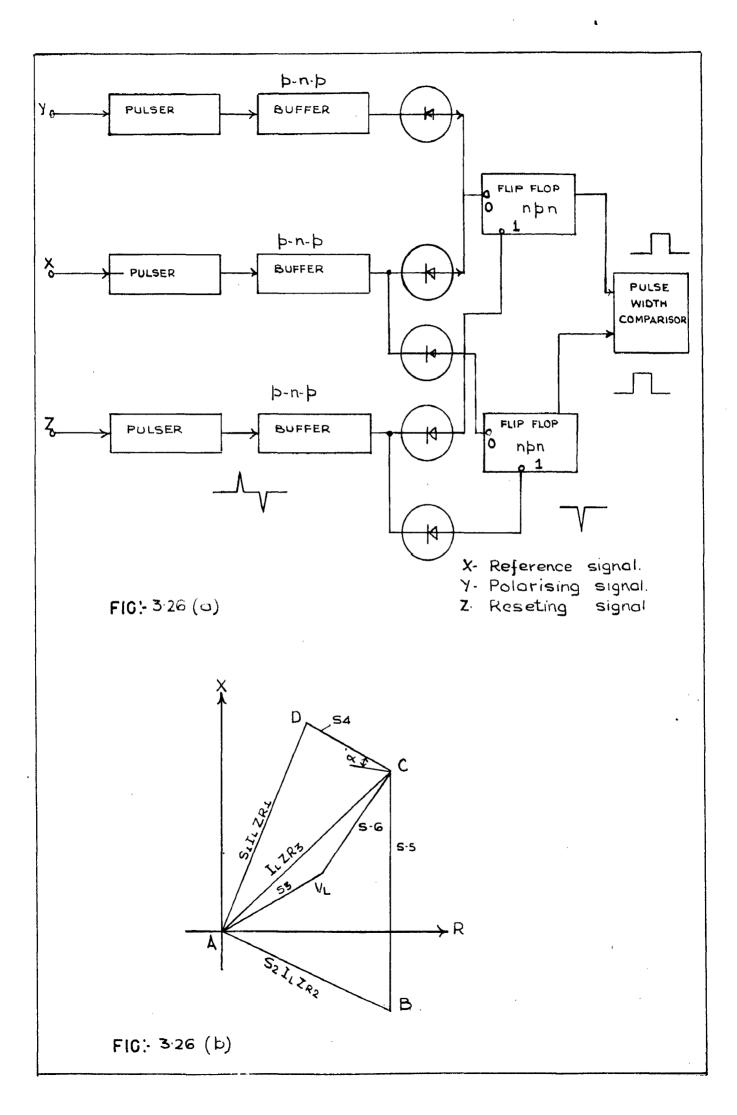

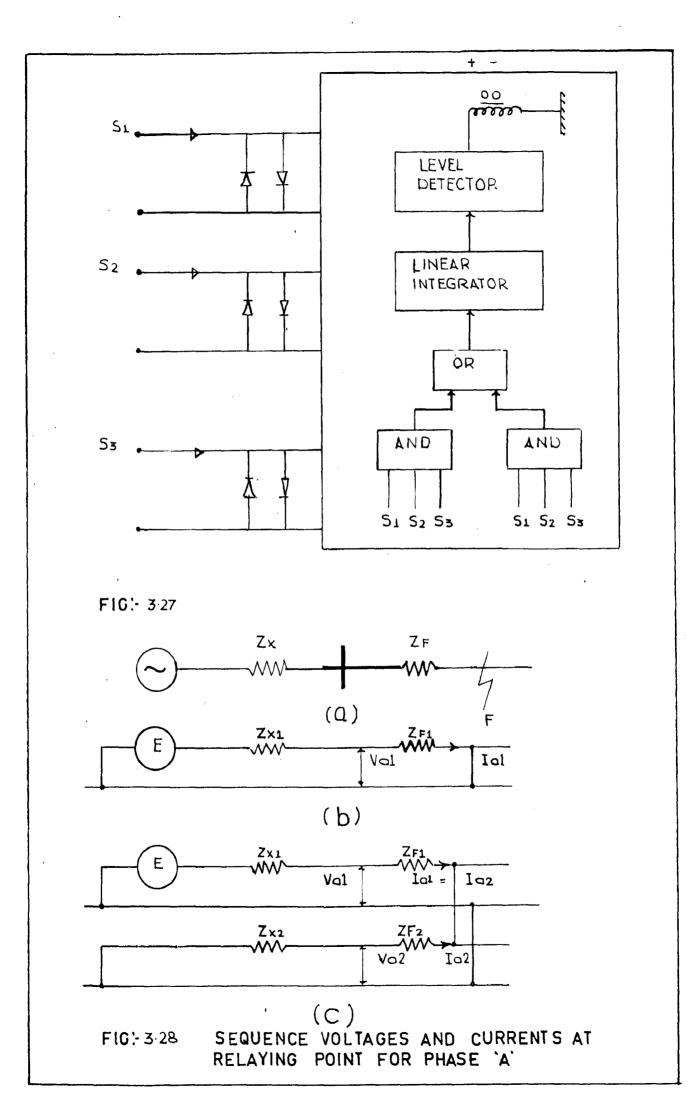

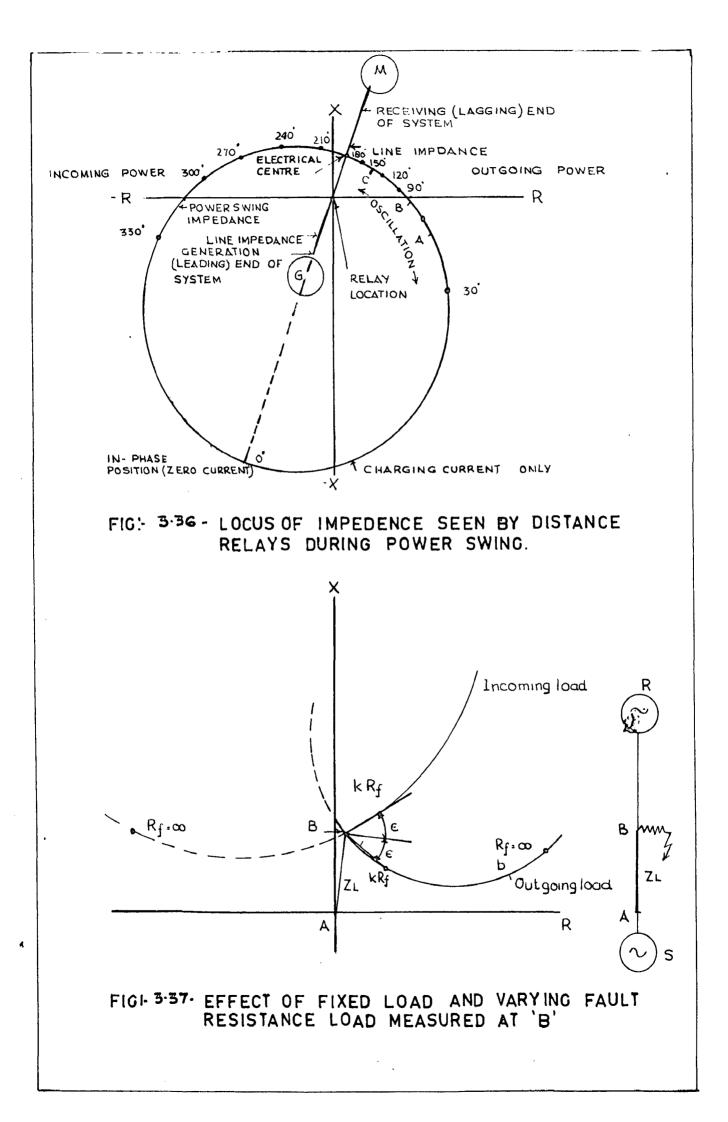

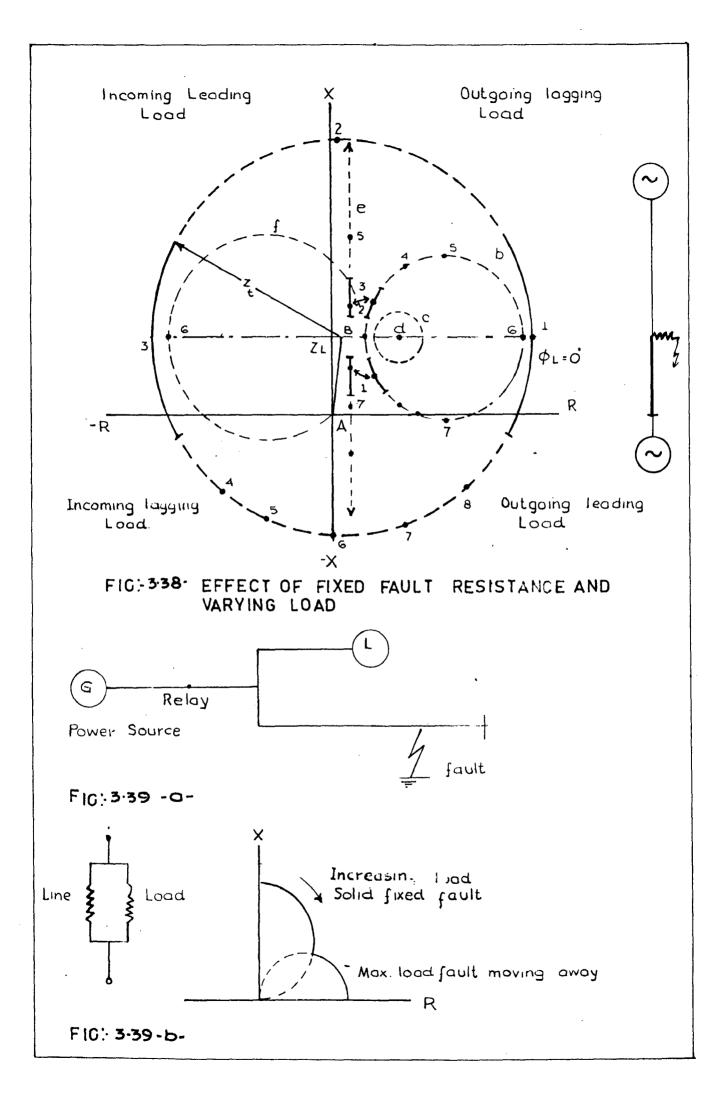

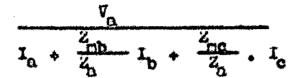

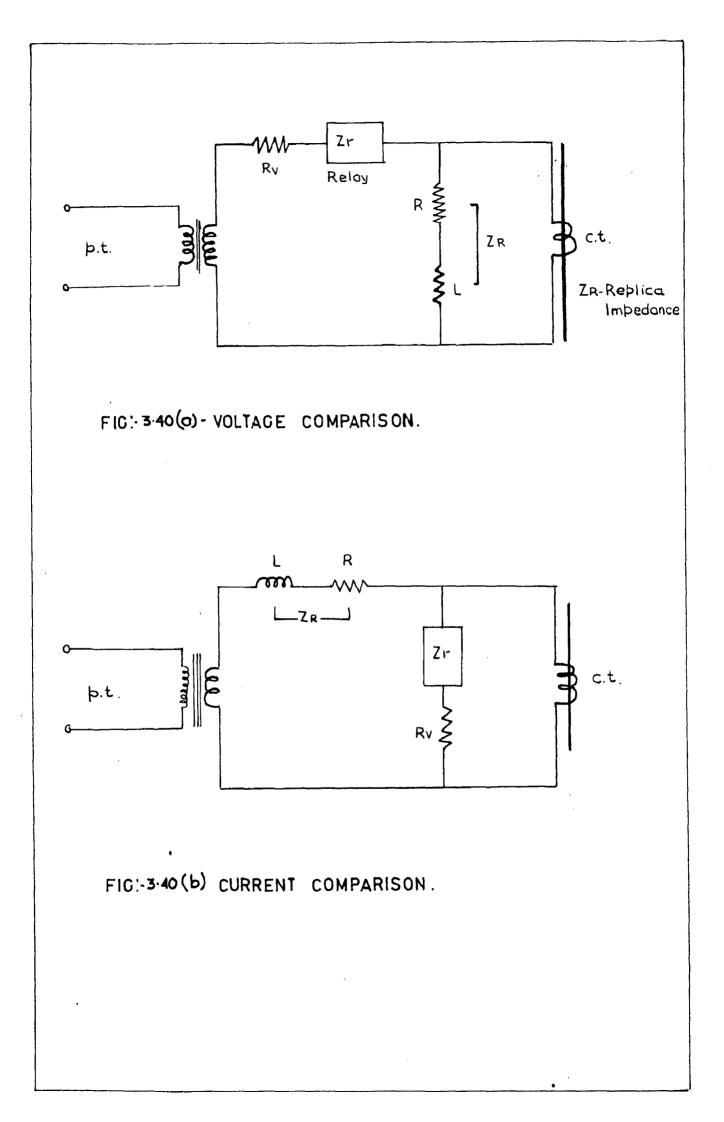

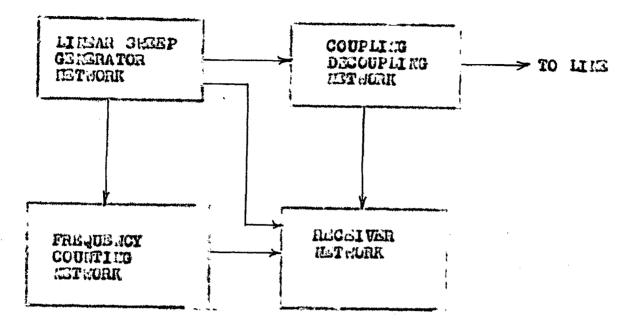

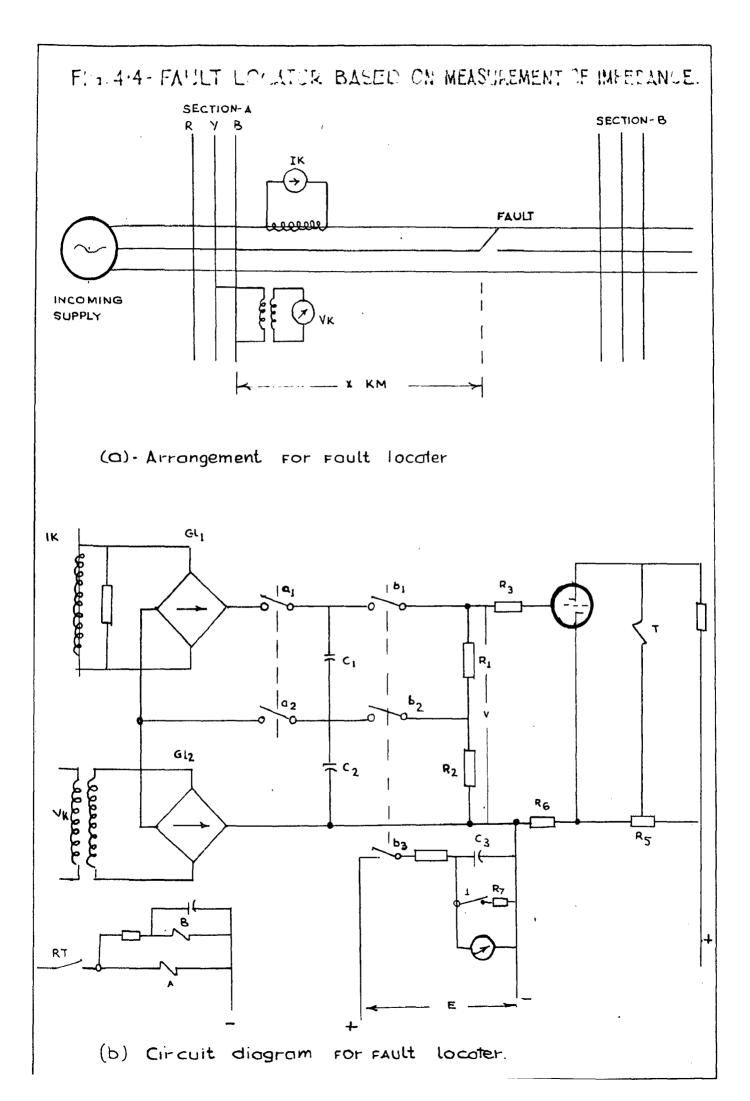

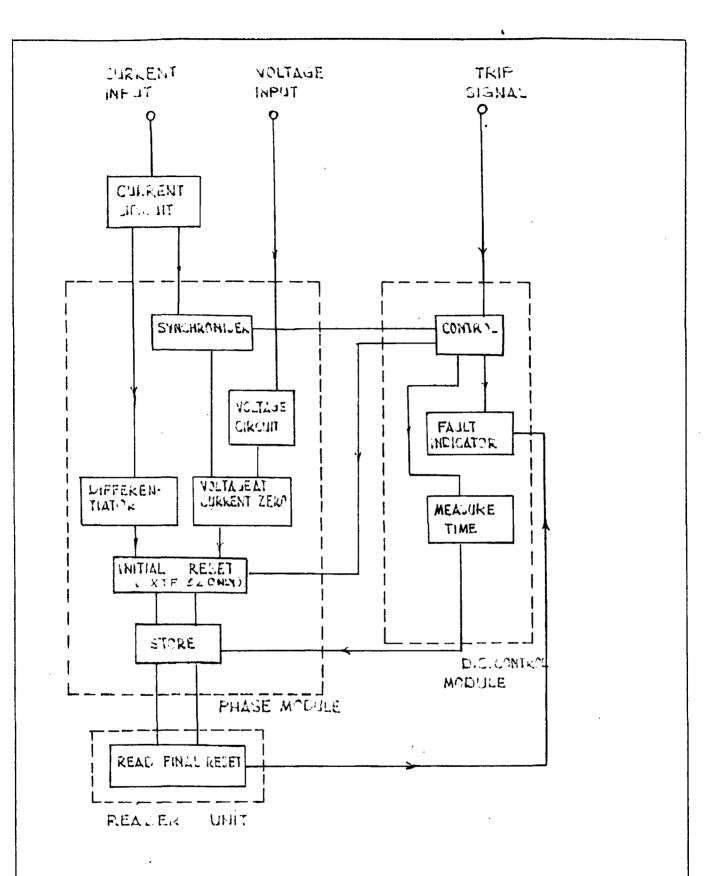

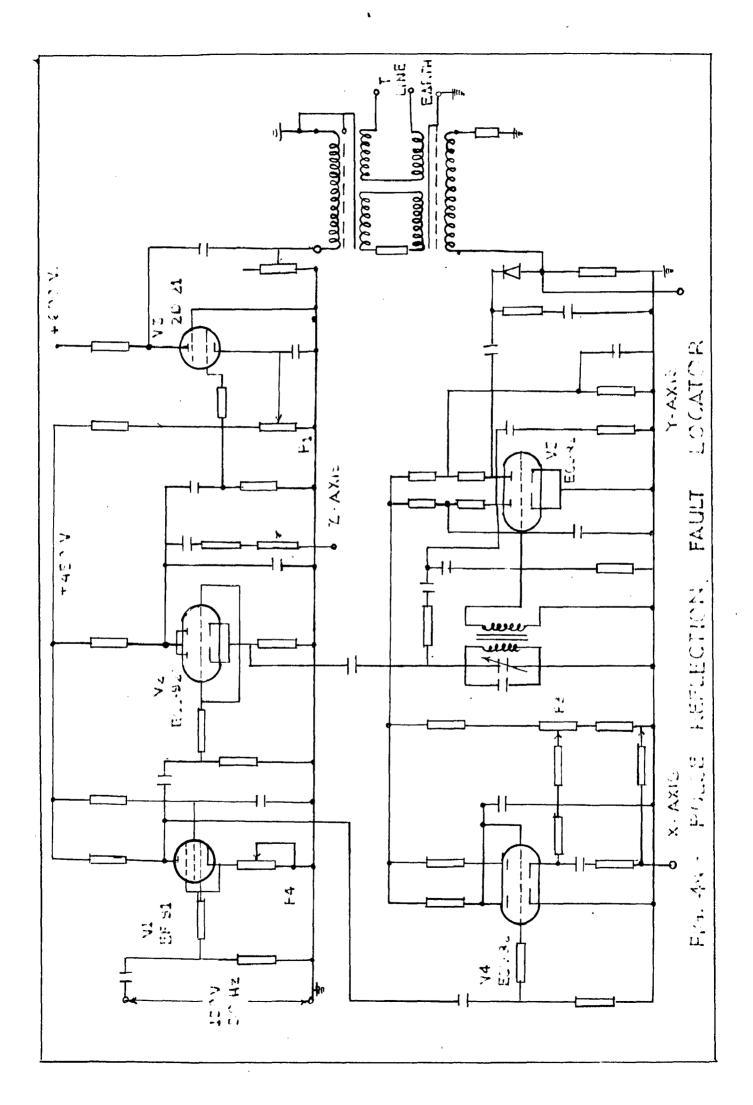

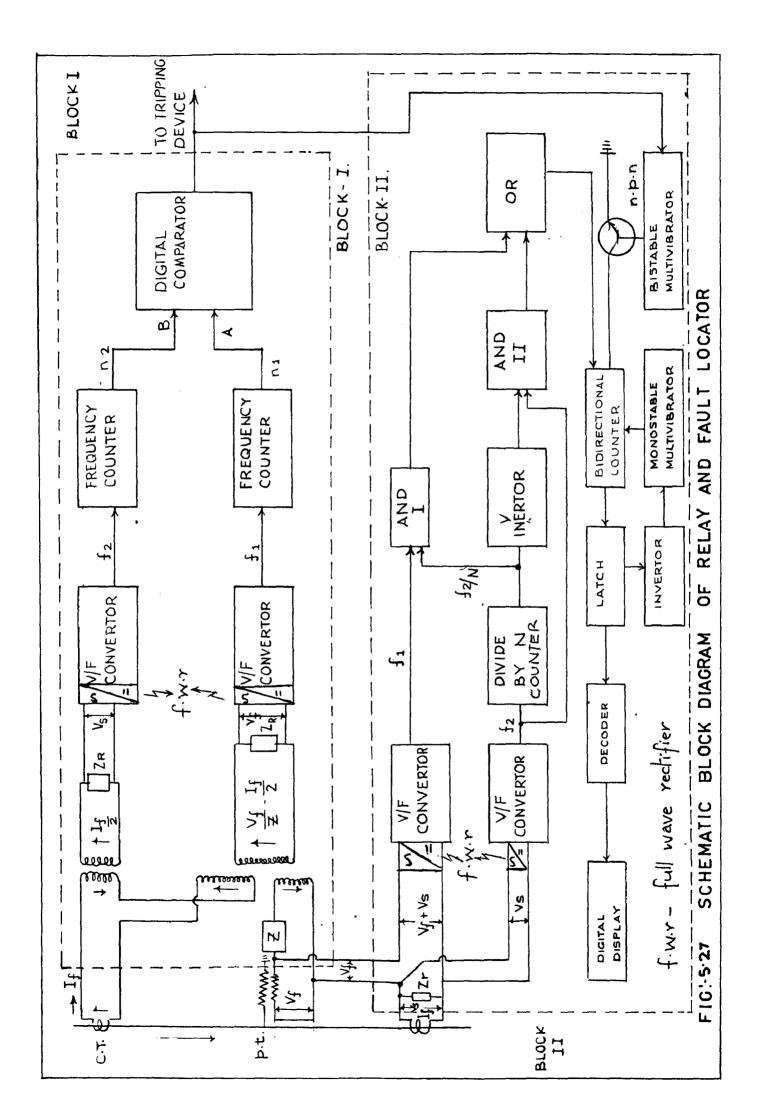

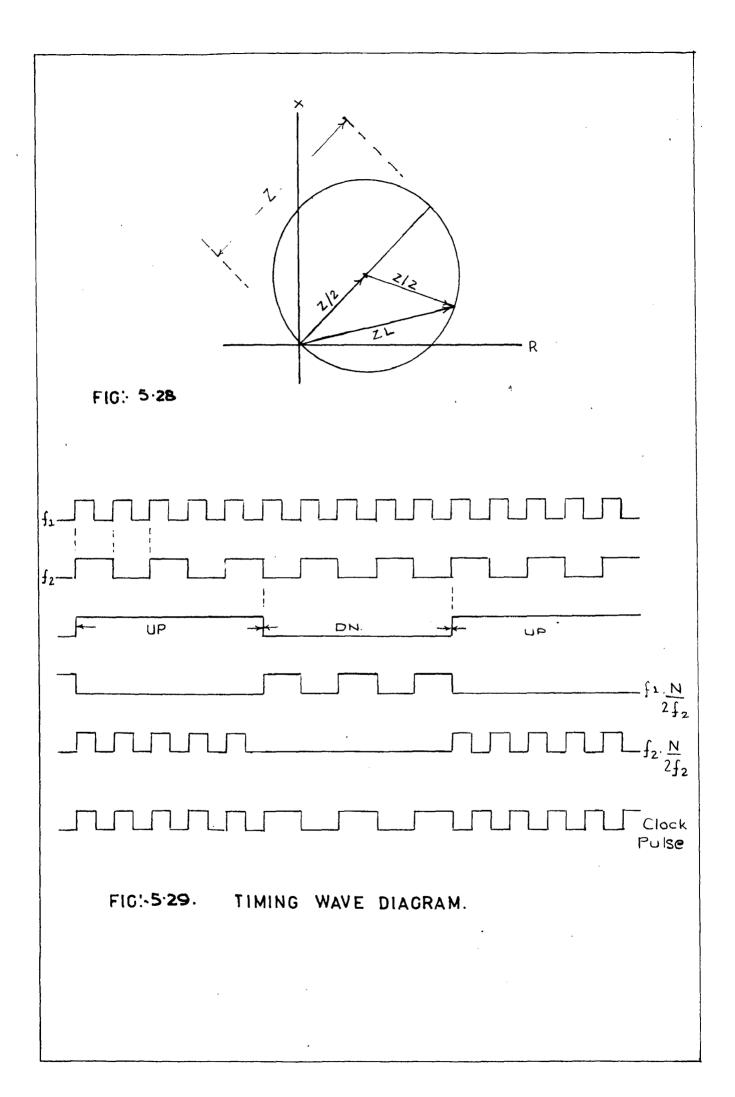

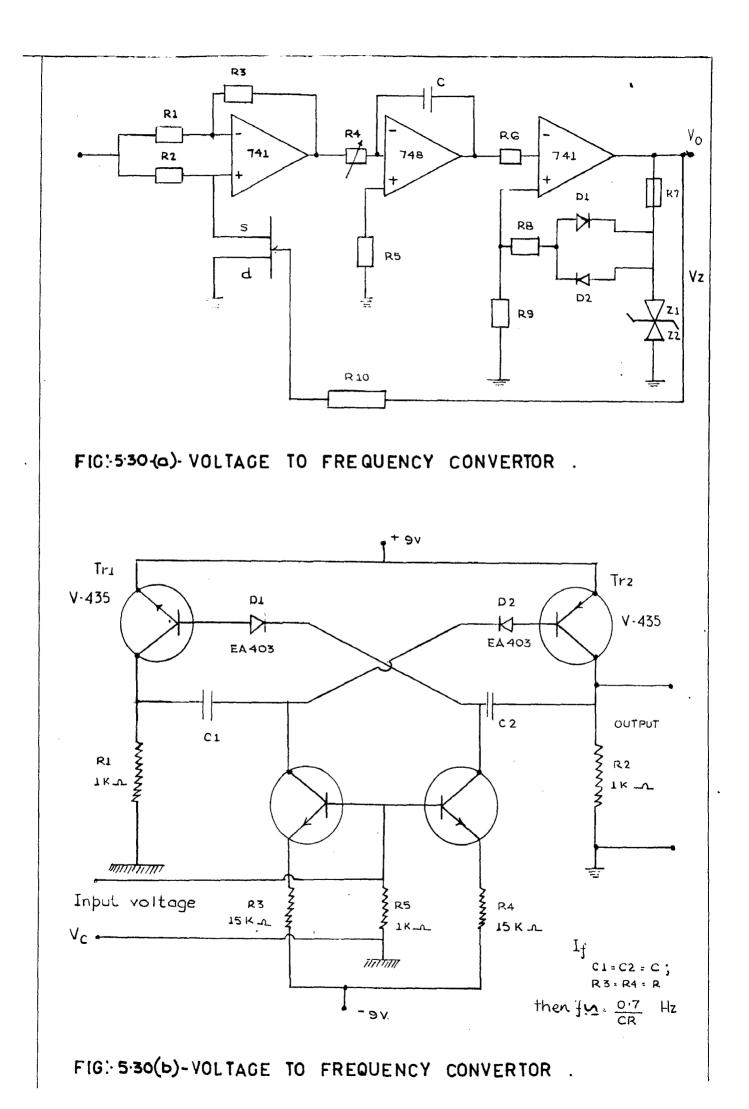

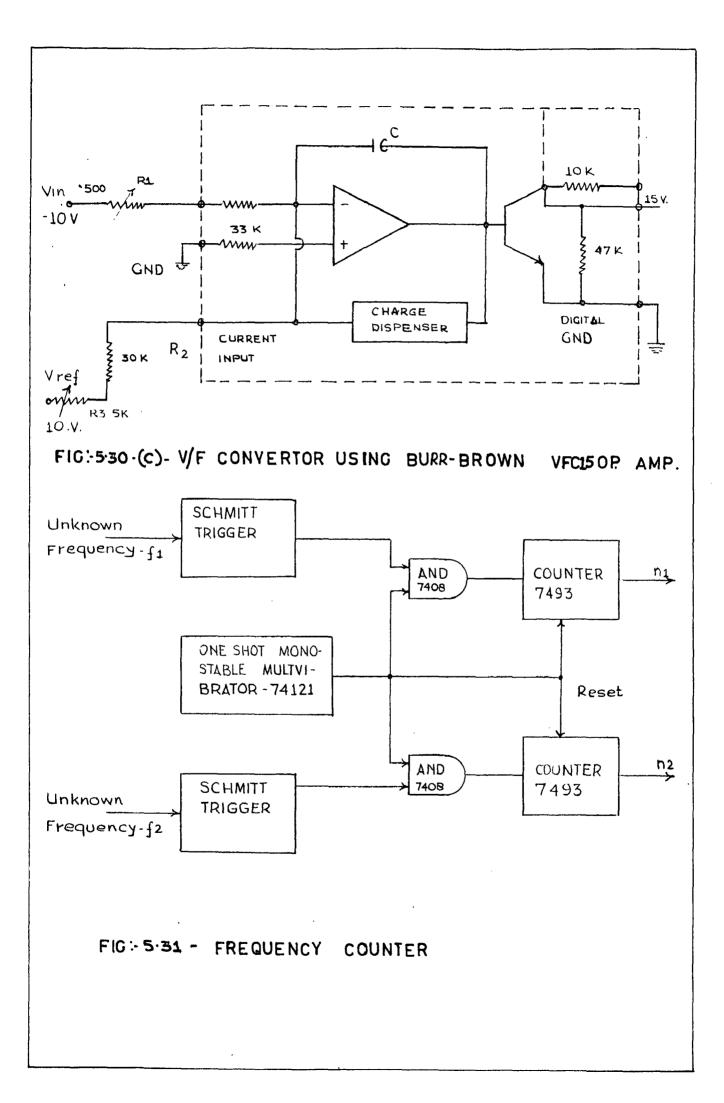

This characteristic is obtained by biasing either the impodence rolay or the she rolay with an additional replica impodence  $\mathcal{E}_0$  and the abount of biasing required decides the choice of the rolay to be used. Both negative effects i.e. characteristic overlapping the origin and positive effect i.e. characteristic with origin outside the she circle can be obtained.